勇敢的芯伴你玩转Altera FPGA连载69:LCD基本驱动实例

0赞勇敢的芯伴你玩转Altera FPGA连载69:LCD基本驱动实例

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1i5LMUUD

LCD的接口时序波形如图8.63所示。VSYNC是场同步信号,低电平有效,从时序图可以看出,VSYNC是每一场(即也可以理解为每送一幅完整图像)的同步信号;与此类似,HSYNC是行同步信号,也是在每一行数据传输的开始产生几个时钟周期的低脉冲。这两个信号用于同步当前的数据信号,根据固定的脉冲约定,我们在某些时钟上升沿前将图像数据送到数据总线上供LCD内部锁存。

图8.63 LCD驱动时序波形

如表8.11所示,这是LCD时序图中对应的时间参数。

表8.11 LCD驱动时序参数表

信号 | 列项 | 标记 | 最小值 | 标准值 | 最大值 | 单位 |

Dclk | 频率 | Tosc | 156 | ns | ||

最大时间 | Tch | 78 | ns | |||

最小时间 | Tcl | 78 | ns | |||

Data | 建立时间 | Tsu | 12 | ns | ||

保持时间 | Thd | 12 | ns | |||

Hsync | 周期 | TH | 408 | Tosc | ||

脉冲宽度 | THS | 5 | 30 | Tosc | ||

后沿 | THB | 38 | Tosc | |||

显示周期 | TEP | 320 | Tosc | |||

同步周期 | THE | 36 | 68 | 88 | Tosc | |

前沿 | THF | 20 | Tosc | |||

Vsync | 周期 | TV | 262 | TH | ||

脉冲宽度 | TVS | 1 | 3 | 5 | TH | |

后沿 | TVB | 15 | TH | |||

显示周期 | TVD | 240 | TH | |||

前沿 | TVF | 2 | 4 | TH |

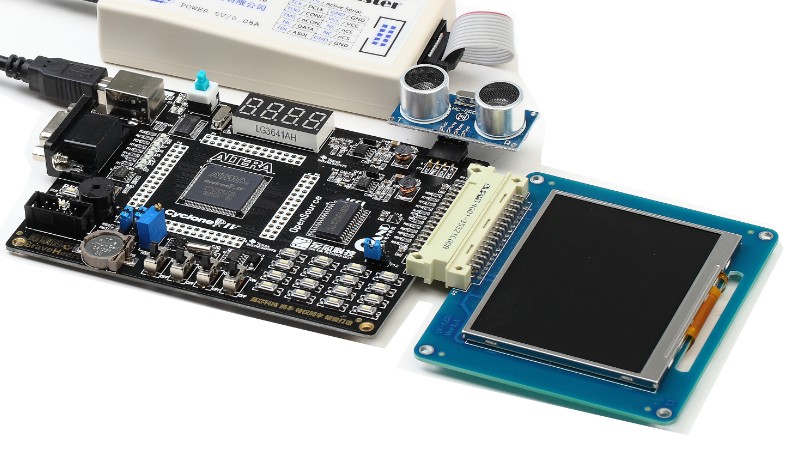

如图8.64所示,本实例除了SF-CY4开发板,还需要SF-LCD子板用于连接3.5寸320*240的真彩色液晶屏。FPGA内部产生32级红色的ColorBar以及LCD时序用于驱动显示。

图8.64 LCD实例功能框图

LCD的驱动大体如图8.65所示。

图8.65 LCD驱动控制逻辑功能框图

本实例模块划分如图8.66所示。

图8.66 LCD实例模块层次

图8.68 LCD装配图