FPGA72:RTLViewerStateMachineViewer

0赞勇敢的芯伴你玩转Altera FPGA连载72:RTL Viewer、State Machine Viewer与Technology Map Viewer

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1i5LMUUD

RTL Viewer

这里首先和大家阐释一下Verilog代码在编译器中是如何一步一步实现到最终的FPGA器件电路中的。设计者先编写RTL级代码(Verilog或VHDL)来描述自己需要实现的功能;然后在EDA工具中对其进行综合,RTL级的代码就被转换为逻辑电路,就如与、或、非等一大堆门电路的各种组合;最后这些逻辑电路通过映射转换到特定的FPGA器件中实现,这个步骤通常我们称之为布局布线。整个的过程如图8.89所示。

图8.89 FPGA代码编译过程

而RTL级的代码我们都很容易查看,好说歹说也是我们从别人的工程copy过来的(一般是自己写的),而逻辑电路是否有地方可以一窥?当然有,Quartus II工具中提供了RTL viewer供用户查看,此外,我们上一节的状态机也是能够查看到;布局布线后的结果,即我们的代码在FPGA器件中的最终效果也可以通过Quartus II中的Technology Map Viewer中进行查看。

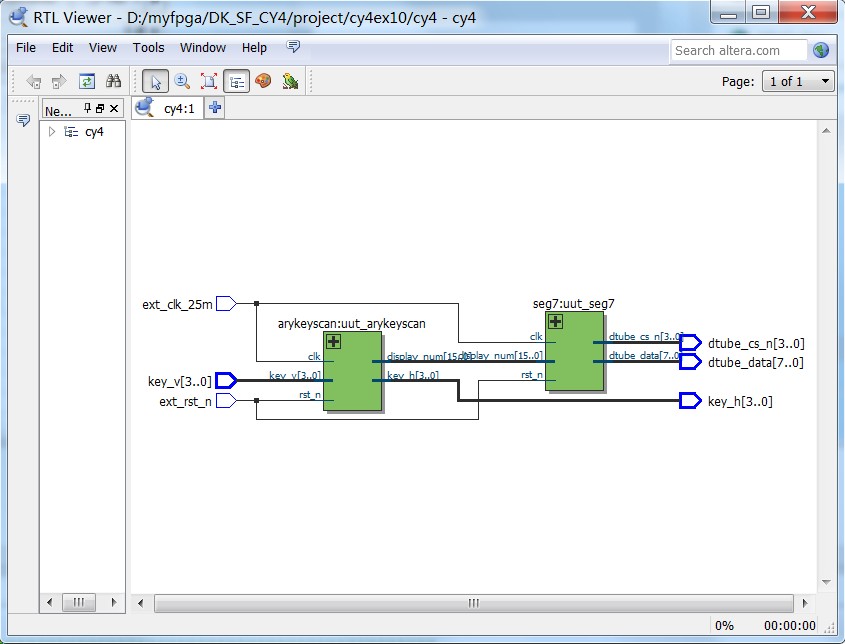

打开实例工程cy4ex10,如图8.90所示,在我们的“Task à Compilation”中,在展开“Compile Design à Analysis & Synthesis à Netlist Viewers”后,可以双击“RTL Viewer”选项。

图8.90 RTL Viewer编译菜单

随后弹出如图8.91所示的RTL Viwer界面。这里的绿色矩形寄存器框可以继续双击查看。

图8.91 RTL Viewer界面

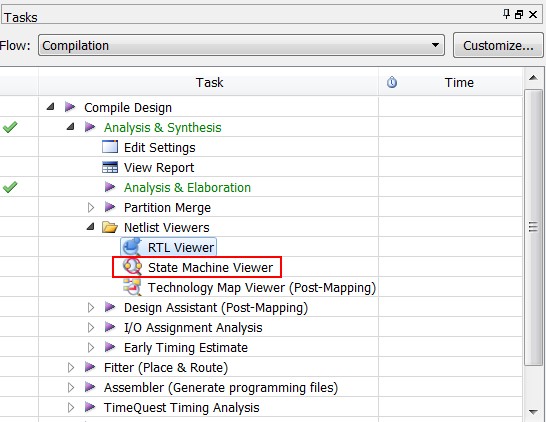

如图8.92所示,在我们的“Task à Compilation”中,在展开“Compile Design à Analysis & Synthesis à Netlist Viewers”后,可以双击“State Machine Viewer”选项。

图8.92 State Machine Viewer编译菜单

随后弹出如图8.93所示的State Machine Viewer界面。

图8.93 State Machine Viewer界面

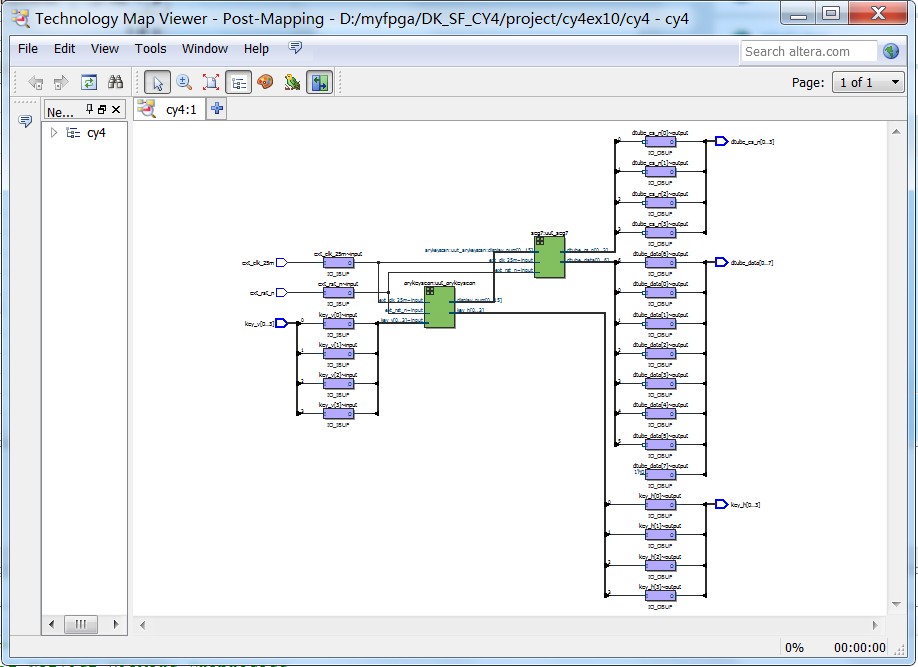

如图8.94所示,在我们的“Task à Compilation”中,在展开“Compile Design à Analysis & Synthesis à Netlist Viewers”后,可以双击“Technology Map Viewer”选项。

图8.94 Technology Map Viewer编译菜单

随后弹出如图8.95所示的Technology Map Viewer界面。

图8.95 Technology Map Viewer界面