玩转Zynq连载37——[ex56] 基于Zynq的AXI HP总线读写实例

0赞

1概述

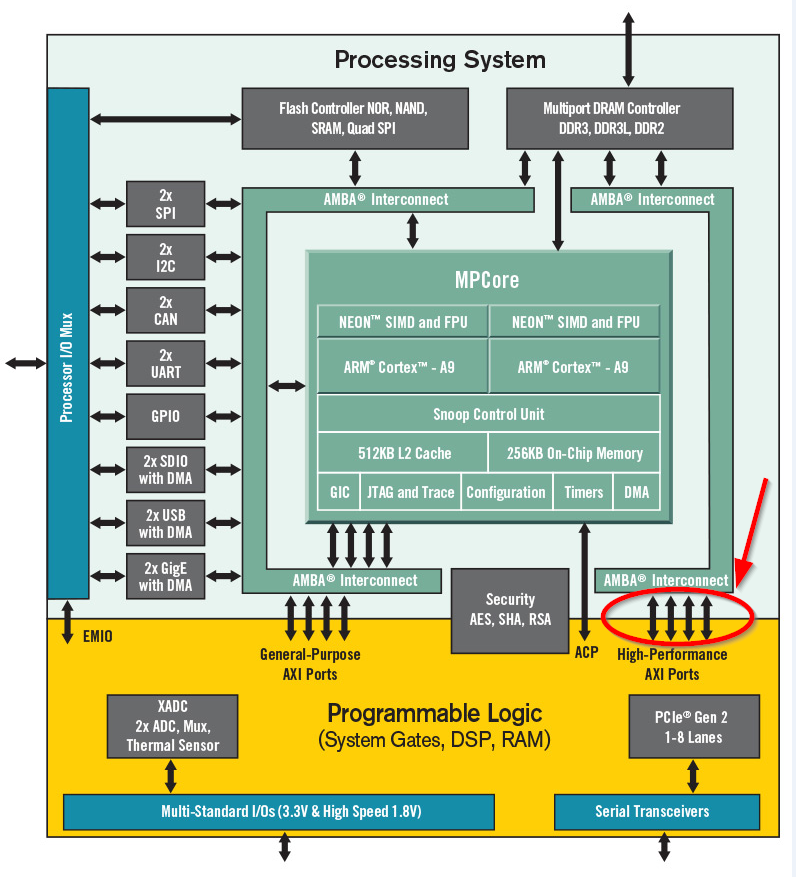

AXI HP总线是Zynq芯片非常重要的一个功能,它可以实现Cortex A9与PL之间大吞吐量的数据通信。可以说,Zynq芯片最大的卖点恐怕就是这条总线。对不起,不是1条,是4条这样的AXI HP总线。PL作为AXI HP主机,可以通过这4条总线实现对内存(DDR3)的读写访问,这4条总线加总的极限带宽,通常能够超过DDR3的最大有效带宽,因此,对于处理器与PL之间的数据交互,Zynq芯片可以做到了最优状态。因此,对于用Zynq做开发的工程师而言,如何玩转AXI HP总线就成为了必修课。

本实例(zstar_ex56)通过一个简单的AXI HP总线主机的读时序和写时序逻辑,来带领读者掌握基于Zynq的AXI HP总线基本使用方法。在这个实例中,首先需要在Zynq PS端对AXI HP总线进行配置,在系统硬件框图中进行必要的接口引出,然后在顶层源码中例化接口,并进行AXI HP读写时序的逻辑设计。

2 AXI总线协议介绍

参考文档《玩转Zynq-基础篇:AXI总线协议介绍.pdf》。

3Zynq PS的AXI HP配置

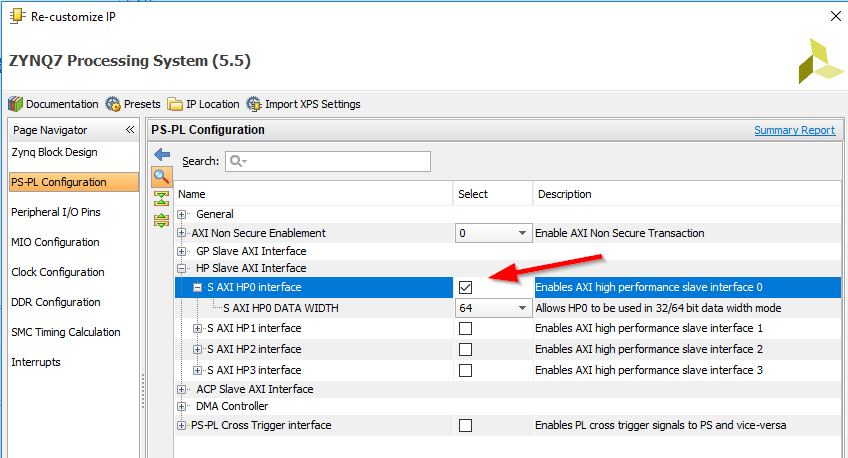

在ZYNQ7 Processing System中,点击左侧Page Navigator的PS-PL Configuration页面,右侧展开HP Slave AXI Interface --> S AXI HP0 Interface,勾选S AXI HP0 Interface并且在展开的S AXI HP0 DATA WIDTH后面选择数据位宽是64(可选项只有32bit和64bit)。

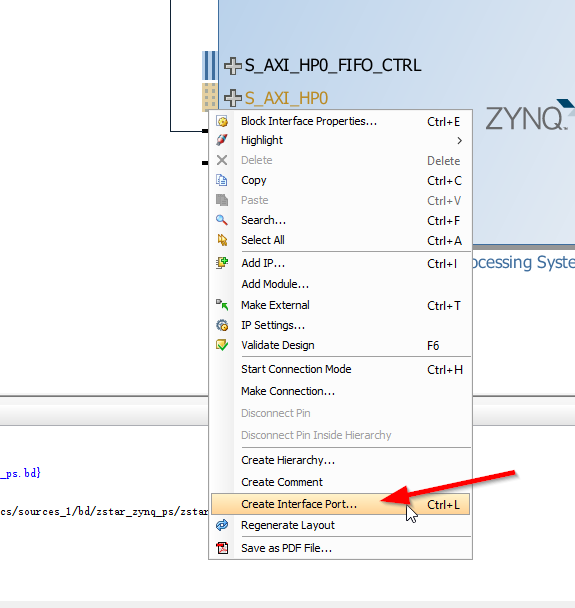

回到Diagram中,需要将新增加的S_AXI_HP0接口引出。如图所示,点击选中S_AXI_HP0,然后单击右键,在弹出菜单中点击Create Interface Port...。

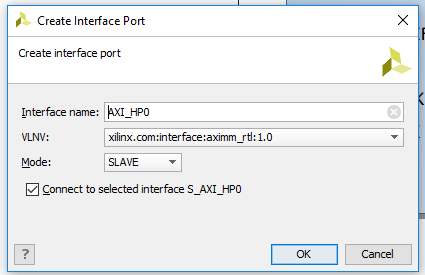

如图所示,将接口命名为AXI_HP0。

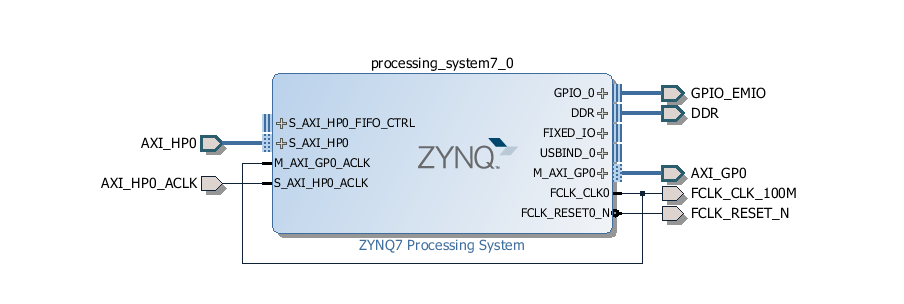

同样的方式,将S_AXI_HP0_ACLK引出,命名为AXI_HP0_ACLK。完成接口引出后,如图所示。

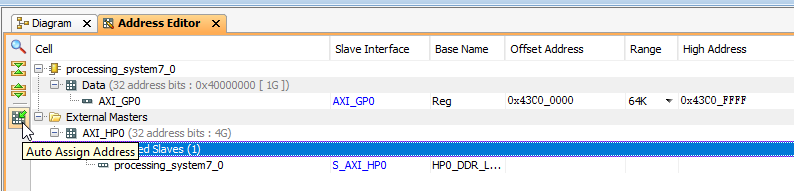

在Address Editor中,由于新增加的AXI_HP0总线地址还未做映射,所以如图所示,需要点击左侧的Auto Assign Address进行自动地址分配。

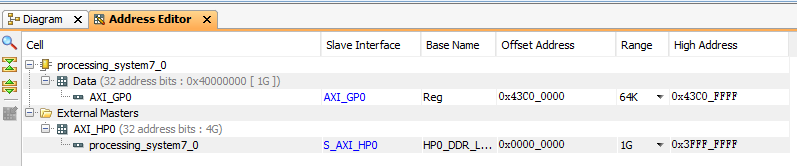

完成地址映射后,如图所示,AXI_HP0默认分配了偏移地址(Offset Address)0x0开始的1G内存空间。也就是说,这1G的地址空间是AXI_HP0可访问的地址空间。通常而言,DDR3也会默认映射到这一段地址空间中。那么,通过AXI_HP0就可以实现DDR3的读写了。

如图所示,点击Validate Design确认当前系统配置是否OK。

4 AXI HP主机读写逻辑设计

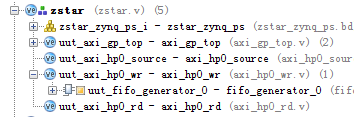

本实例工程源码的层次结构如下所示。我们重点来看和AXI HP相关的模块axi_hp0_source.v、axi_hp0_wr.v和axi_hp0_rd.v模块。

axi_hp0_source.v模块以1s为单位,计数定时,产生对AXI HP0总线固定地址32'h0100_0000写一组递增的burst lenght = 16的64bit位宽的数据。其产生的信号接口如下。

o_data_*信号送到axi_hp0_rd.v模块发起一次读DDR3的操作,i_data_*信号送到axi_hp0_wr.v模块发起一次DDR3写的操作。在ILA在线逻辑分析仪中,由于每秒都有AXI HP0总线的读操作和写操作,因此我们可以很容易抓到它们的时序进行观察和分析。

axi_hp0_wr.v模块对AXI HP0总线的写地址通道、写数据通道和写响应通道的信号接口产生必要的时序,完成一组数据的DDR3写入操作。该模块下例化了一个名为fifo_generator_0的FIFO,外部需要写入的数据都统一送到该模块中,当状态机检测到该FIFO的数据个数满足一个DDR3写入的burst length时,就发起一次DDR3写地址和数据的时序,读出FIFO中国的数据,通过AXI HP0的写数据通道送给DDR3。执行写操作的状态关系是先写地址(STATE_WADD),然后送数据(STATE_WDAT),最后等待写响应(STATE_DONE),完成一次操作(STATE_IDLE)。

axi_hp0_rd.v模块对AXI HP0总线的读地址通道产生必要的时序,由于读数据通道是由从机输出的,因此对该模块而言是输入,该实例的目的只是希望通过ILA在线逻辑分析仪进行时序查看,所以我们没有对读数据通道的接口做任何额外的连接。该模块的设计比较简单,按照axi_hp0_source.v模块给出的每秒定时脉冲和地址,每秒产生一个读地址通道时序即可。

5 AXI HP主机读写逻辑仿真

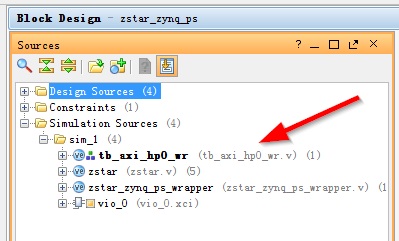

在本实例工程的Sources中,展开Simulation Sources --> sim_1,可以看到已经编写好的测试脚本tb_axi_hp0_wr.v,该测试脚本主要针对我们的AXI主机写模块axi_hp0_wr.v进行测试。在Simulation Sources中高亮的模块,表示当前有效的顶层模块。

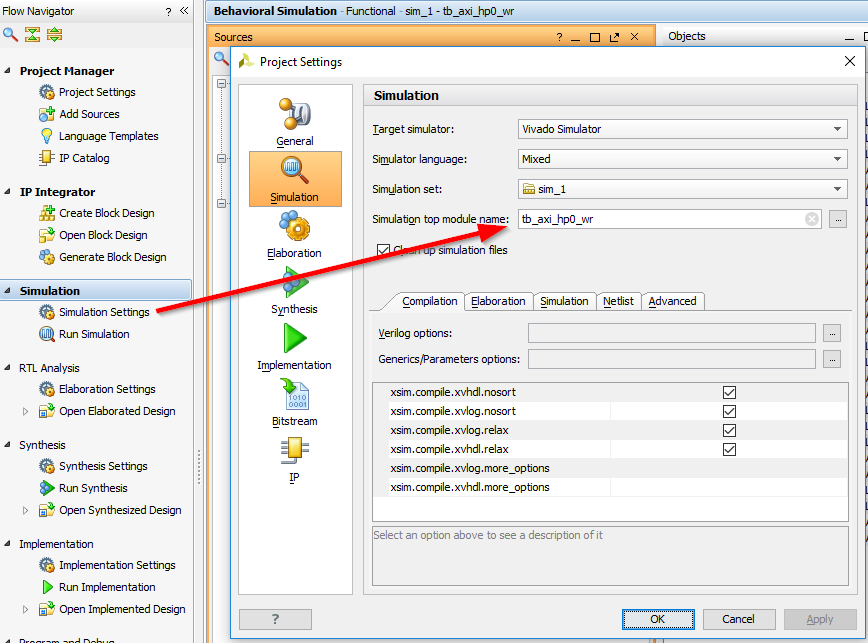

若是希望设定更改Simulation Sources中有效的顶层模块,如图所示,可以展开Flow Navigator --> Simulation,点击Simulation Settings。弹出选项卡中,设置Simulation top module name即当前有效的Simulation顶层模块。

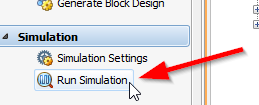

点击Simulation --> Run Simulation即可执行测试脚本的仿真。

如图所示,在弹出仿真界面后,点击Run All按钮,可以运行仿真测试。

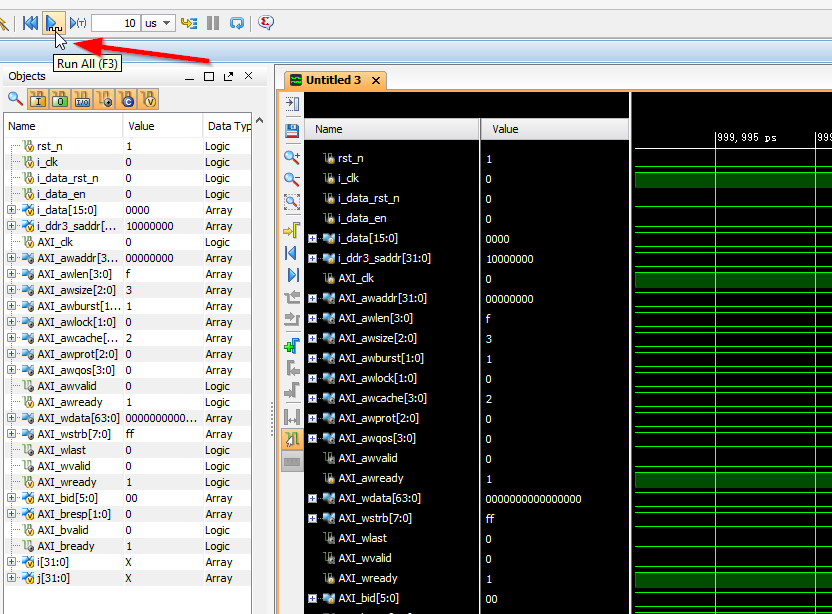

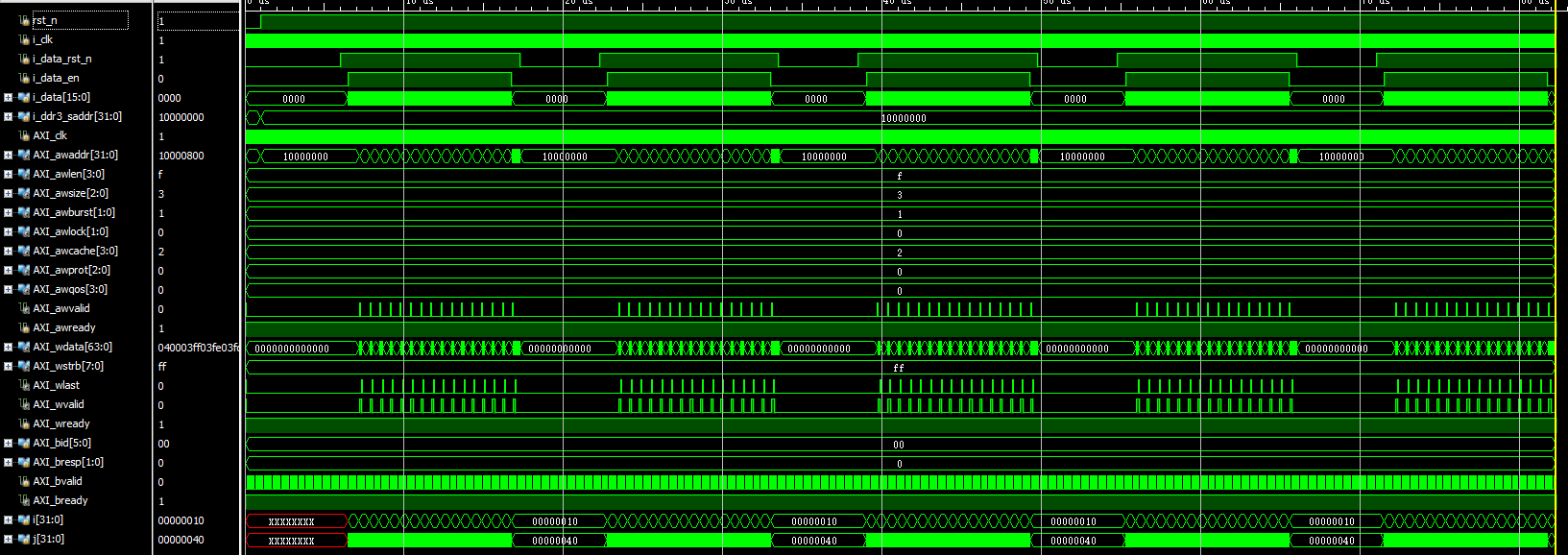

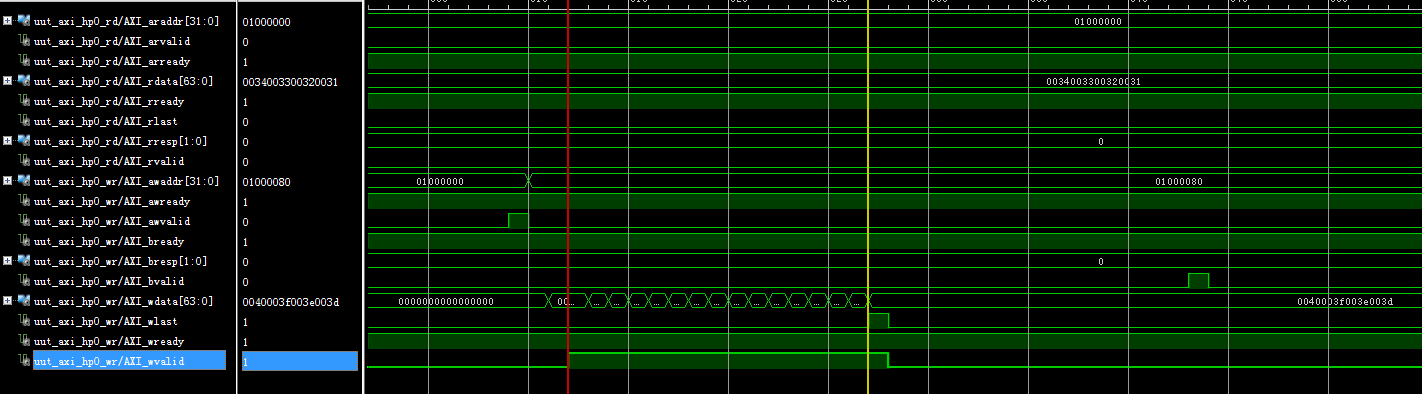

axi_hp0_wr.v模块的仿真波形如下。

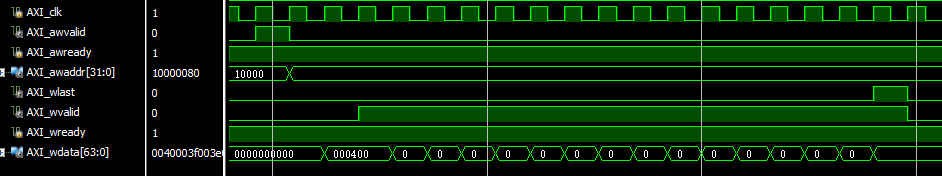

其中一次AXI HP0总线写地址和数据的时序波形如图所示。

6嵌入式软件工程创建

参考文档《玩转Zynq-工具篇:导出PS硬件配置和新建SDK工程.pdf》导出PS硬件工程,并打开EDK新建一个HelloWorld的模板工程。本实例并不需要在嵌入式软件中做任何其它的功能实现,只需要在.bit文件烧录完成后,运行嵌入式软件即可(主要是PL端的时钟源是来自Zynq PS,因此必须在嵌入式软件运行起来后,才能够产生时钟信号)。

7板级调试

在Zstar板子上,设置跳线帽P3为JTAG模式,即PIN2-3短接。

连接好串口线(USB线连接PC的USB端口和Zstar板的UART接口)和Xilinx下载线(下载器连接PC的USB端口和Zstar板的JTAG插座)。使用5V电源给板子供电。

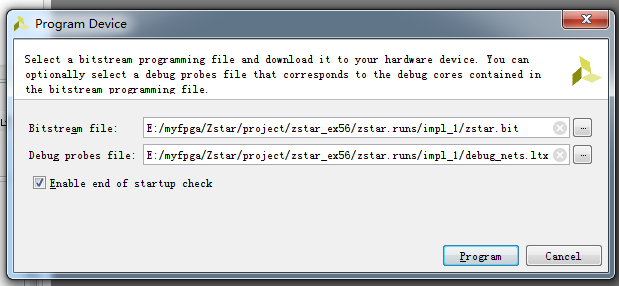

参考文档《玩转Zynq-环境篇:XilinxPlatformCableUSB下载器使用指南.pdf》烧录PL工程编译产生的.bit和.ltx文件到Zstar板中,如图所示。

参考《玩转Zynq-工具篇:SDK在线运行裸跑程序.pdf》导出硬件并打开EDK,创建HelloWorld模板工程。运行工程,注意PL的.bit文件已经烧录好,不用再次烧录,直接运行.elf文件即可。

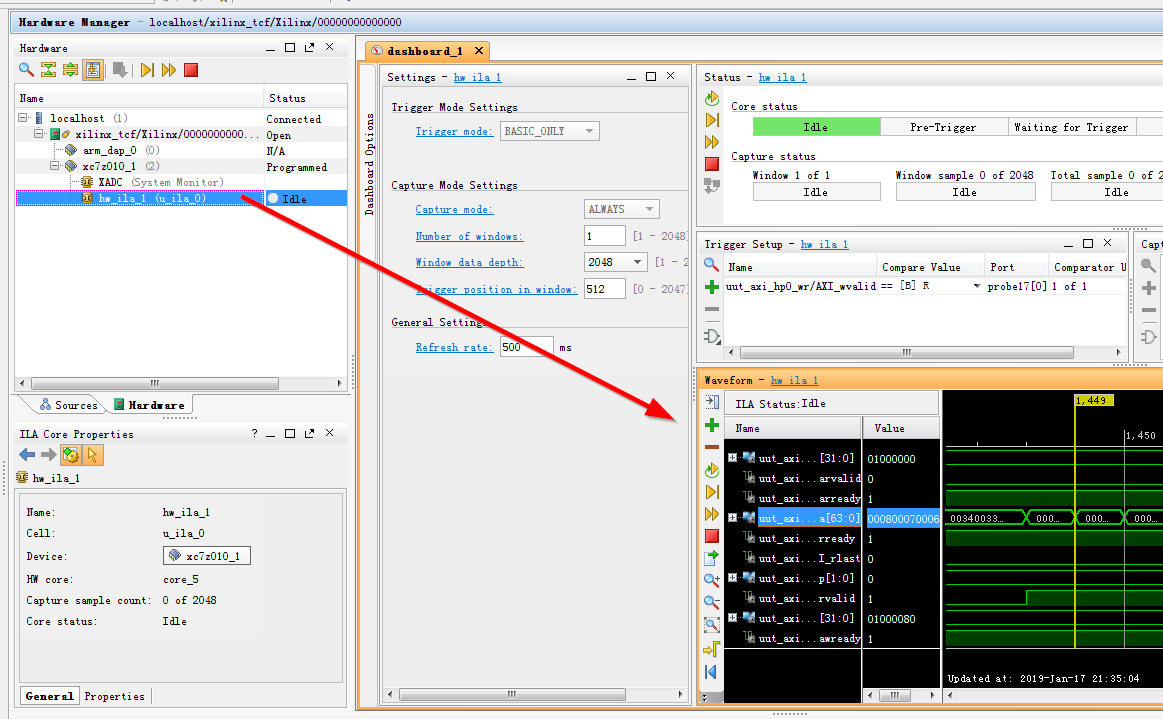

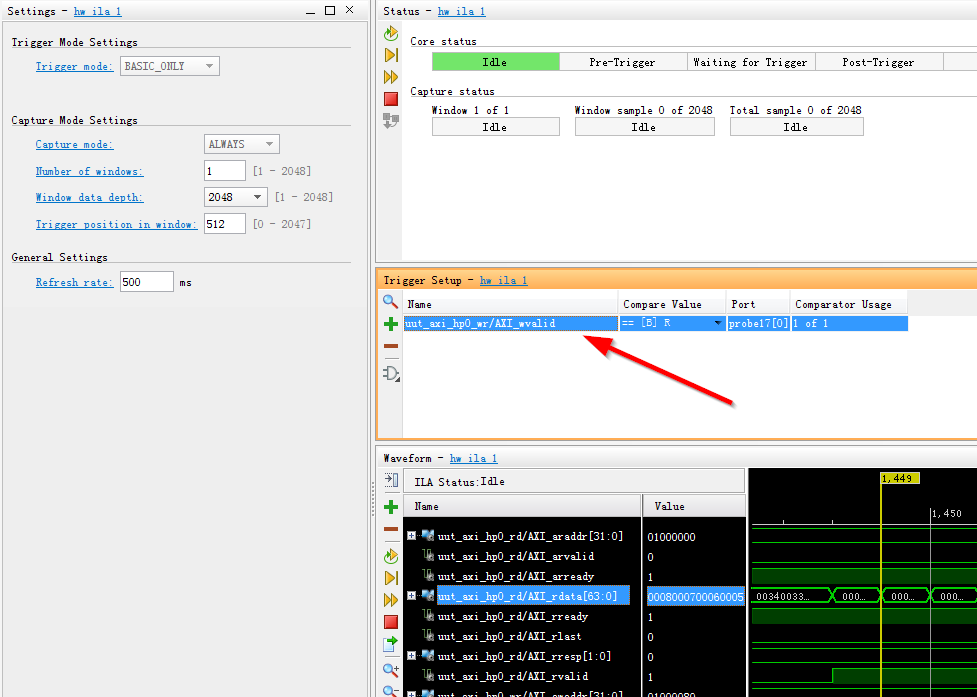

回到Vivado,查看当前引出的AXI接口。如图所示,可以双击hw_ila_1即可弹出dashboard_1界面。

如图所示,设置以AXI_wvalid == R作为触发条件,触发一次波形。

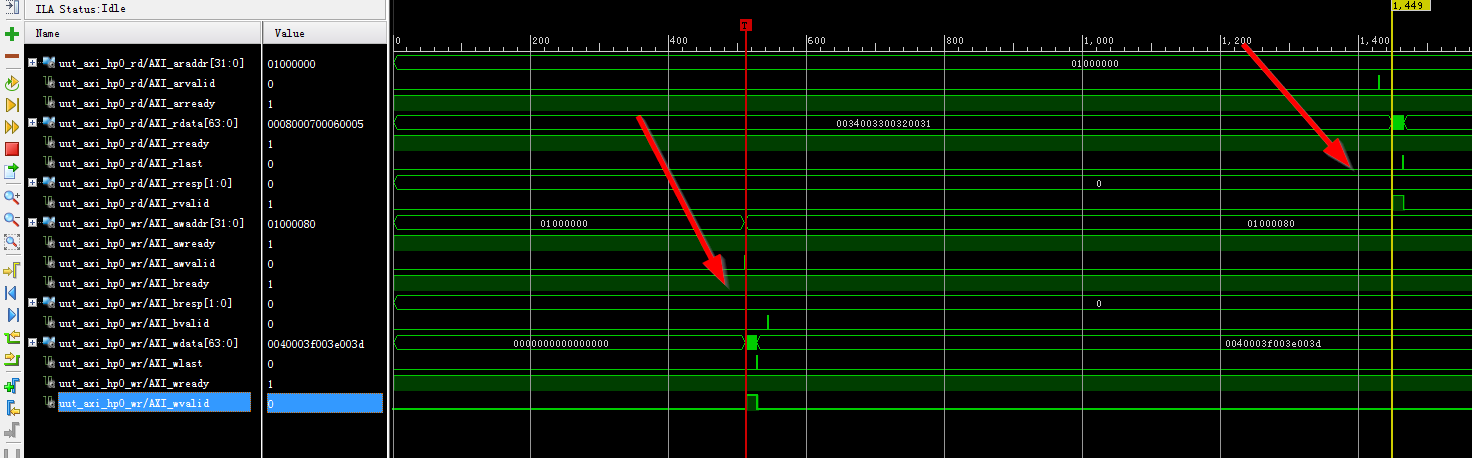

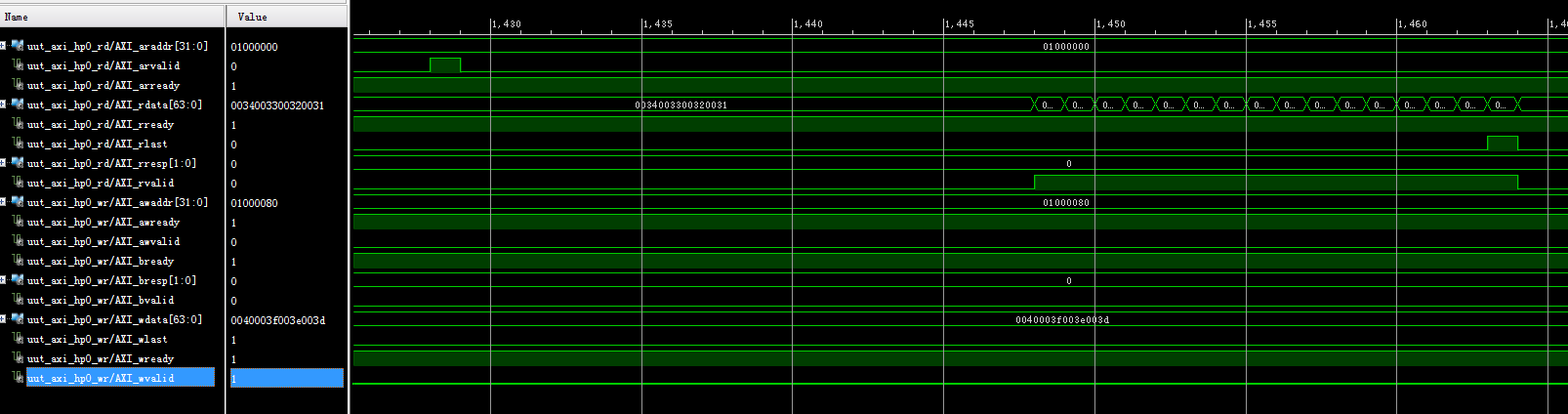

AXI_wvalid == R触发后,如图所示,出现了两组波形事件,前面一个是AXI HP总线写数据波形,后面一个是AXI HP总线读数据波形。

如图所示,前面一个波形是对AXI总线固定地址连续写入16个每16bit递增的64bit数据。

如图所示,后面一个波形是对相同地址的AXI总线读操作,读出的16个64bit数据和写入的数据一致。

更多资料共享

腾讯微云链接:https://share.weiyun.com/5s6bA0s

百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw

提取码:ld9c