简述DLL与PLL的区别

0赞在学习Lattice ECP3系列FPGA时,发现芯片内部集成了两个DLL和10个PLL。PLL一般可以用来分频,倍频、相位调整,而DLL也可以做到这些基本功能,那么他们之间到底有什么区别呢?下面来做一个简要的分析与总结。

DLL-Delay locked loop用在数字电路中,用来自动调节一路信号的延时,使两路信号的相位一致(边沿对齐), 在需要某些数字信号(比如data bus上的信号)与系统时钟同步的情况下, DLL将两路clock的边沿对齐(实际上是使被调节的clock滞后系统clock 整数个周期),用被调节的clock做控制信号,就可以产生与系统时钟严格同步的信号(比如输出数据data跟输入clock同步,边沿的延时不受到电压、温度、频率影响)。

PLL--Phase locked loop除了用作相位跟踪(输出跟输入同频同相,这种情况下跟DLL有点相似)外,可以用来做频率综合(frequency synthesizer),输出频率稳定度跟高精度低漂移参考信号(比如温补晶振)几乎相当的高频信号,这时,它是一个频率源。利用PLL,可以方便地产生不同频率的高质量信号,PLL输出的信号抖动(频域上表现为相噪)跟它的环路带宽,鉴相频率大小有关。总的说来,PLL的环路带宽越小,鉴相频率越高,它的相位噪声越小(时域上抖动也越小)。

由于在实际ADC系统中,采样系统总的动态特性主要取决于采样时钟的抖动特性,如果对频率要求不是太高,VCXO是比较好的选择。如果确实需要可变频率低抖动时钟,则基于PLL的时钟发生器是最好选择。

从应用上看

DLL即Delay Lock Loop, 主要是用于产生一个精准的时间延迟, 且这个delay不随外界条件如温度,电压的变化而改变.这个delay是对输入信号的周期做精确的等分出来的, 比如一个输入信号周期为20ns, 可以设计出等分10份的delay, 即最小2ns的delay. 这在高速界面做clock recovery and data recovery上很有用处。 由于普通的delay cell在不同的corner其delay会发生很大的变化(FF与SS相差几乎3倍), 有时候会被迫采用DLL来产生一个精准的delay而不是用普通的delay cell.

而PLL即Phase lock loop, 主要是根据一个输入时钟产生出一个与输入时钟信号in phase的倍/除频时钟, 其中倍频时钟和输入、输出时钟in phase是最主要的应用。

从内部结构上来看

DLL只有一个大的反馈环来调节最后1T后的信号与输入信号in phase来保证delay 出来的结果是对输入信号周期的均分,如示意图; 输出信号只是对输入信号的一个delay, 即为同频且有一个固定的phase差,同时由于输出信号与输入直接关联,输入信号的jitter,frequency 漂移会直接反映在输出信号上。在实现上,可以是模拟电路也可以是数字电路实现,但绝大多数应该是模拟电路实现比较好,因为需要调节电压来补偿环境变化带来的delay 变化。

PLL除了有一个大的反馈环来让PLL振出的clock与reference clock in phase,内部还有一个小的ring oscillatorl来振出想要的clock,如示意图。由于输出clock是由一个单独的ring oscillator振出来的,所以与reference clock的jitter,frequency漂移几乎完全无关。但由于是内部自己起振,所以比DLL要复杂。这个以前也有提过数字PLL, 但做出来的数字PLL振出来的clock很差,就几乎没有提数字PLL, 而是采用模拟电路来做。

ECP3系列FPGA中的DLL与PLL之间的主要区别

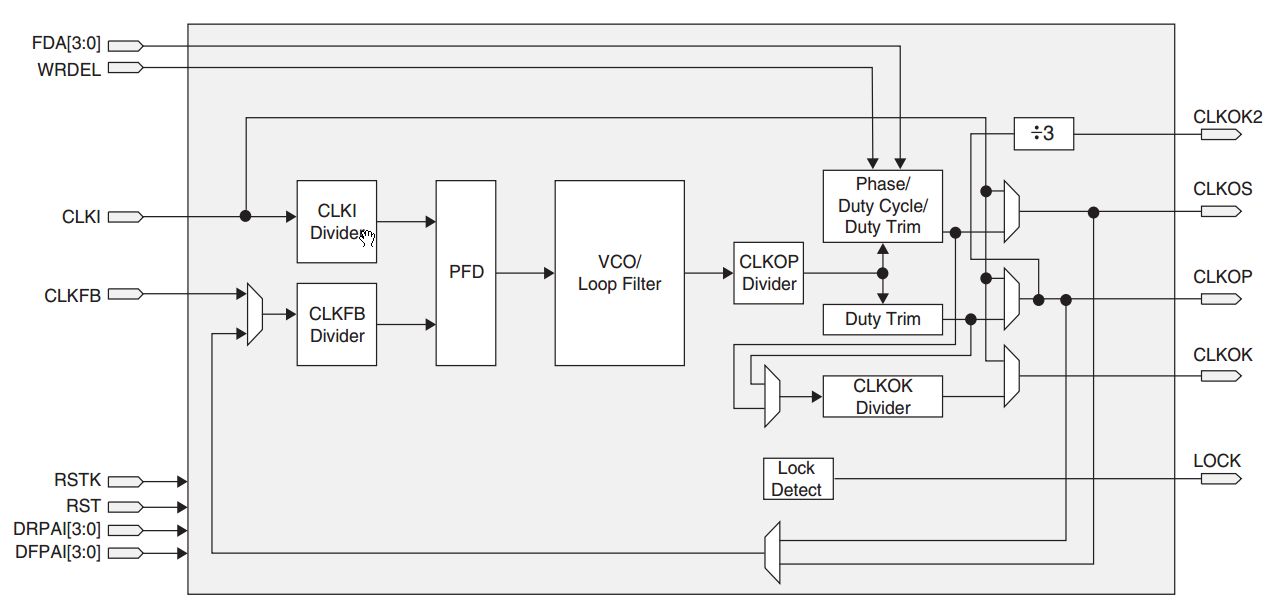

首先上两张图,图1是ECP3中的PLL结构图,图2时ECP3中的DLL结构图。

图1 ECP3中的PLL结构图

图2 ECP3中的DLL结构图

可以清晰地看到,PLL更加侧重分频,倍频与占空比调整等功能,而DLL更加侧重相位调整与时钟对齐等功能。虽然DLL也有分频的功能,但是从图表中可以看出,2分频或4分频在实际的应用中似乎并没有什么卵用(但在DDR控制中却非常有用)。而PLL则不同,其可以轻松完成N分频(N大于100)甚至是倍频的功能,此外PLL的时钟输出路数也更多。