【转】认识FPGA触发器的亚稳态

3赞边沿型触发器的输出有两个稳定状态: 高电平或者低电平。为保证可靠操作, 必须要满足触发器的时序要求,也就是我们熟知的建立时间和保持时间。如果输入信号违反了触发器的时序要求, 那么触发器的输出信号就有可能会出现非法状态---亚稳态。亚稳态是一种不稳定状态,在一定时间后, 最终返回到两个稳定状态之一。

亚稳态输出的信号是什么样子的? 对于系统有什么危害? 如果降低亚稳态带来的危害?这就是下面要探讨的问题。

亚稳态的特点

1、增加触发器进入稳定状态的时间

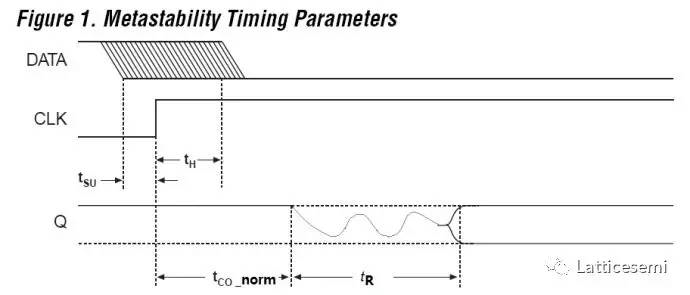

亚稳态的坏处之一是会导致触发器的TCO时间比正常情况要大。多出来的时间tR (resolution time) 就是亚稳态持续的时间,参考图1。如果触发器的时序要求tSU(建立时间)和tH(保持时间)被满足,那么触发器的延时TCO=tCO_norm; 否则如果违反了触发器的时序要求,那么触发器在经过tCO_norm时间后,进入亚稳态,亚稳态持续的时间叫做resolution time,标识为tR。tR过后,亚稳态返回到两个稳定状态之一。

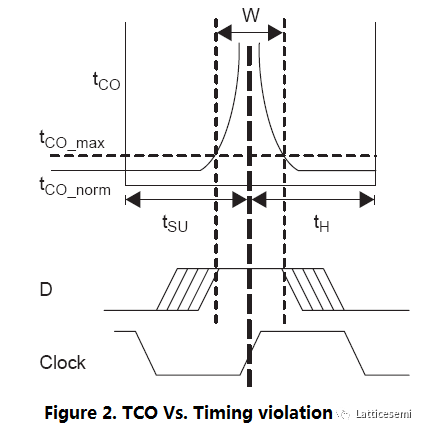

数据的跳变距离触发器的采样时刻越近,tR就越大。这种关系参见图2。

器件制造商给出的tSU和tH指标都是有余量的。轻微的违反tSU或者tH并不会发生亚稳态,只是导致触发器的tCO超出器件的规范(spec)。只有当数据的跳变出现在亚稳态捕捉窗口W (见图2中的W,fs级别的时间窗口),才会发生亚稳态。总的来说,数据的跳变越靠近W窗口,触发器进入稳定态的时间就越长。

在同步设计中,源触发器(Source FlipFlop)的输出必须在一个时钟周期内稳定下来,才能够被目的触发器(Destination FlipFlop)准确采样。如果tR过大,可能让目的寄存器采样到亚稳态,会导致亚稳态的传播。

2、输出毛刺、振荡、或中间电平

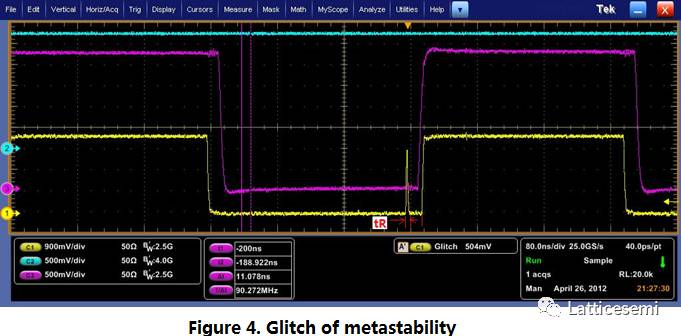

经过一段时间之后,亚稳态返回到稳定状态。有可能返回到高电平,也有可能返回到低电平, 这和输入的数据无关。且在亚稳态的过程中,触发器的输出可能在震荡,也可能徘徊在一个固定的中间电平上。我们来看一个真实案例。见图3。

在这个案例中,我们测试一个FPGA逻辑单元中的亚稳态现象。在测试中,我们让sel信号固定在0,那么逻辑关系为 F1 <= local_2m输入,F0 <= local_2m输入,local_2m和cdr_2m都是2MHz的方波信号,被一个50MHz的异步时钟作同步化处理。Verilog代码为:

always @(posedge clk_50m) if(sel==1)begin clk2m_oa <= cdr_2m ; clk2m_ob <= cdr_2m ; end else begin clk2m_oa <= local_2m ; clk2m_ob <= local_2m ; end

测试中我们发现触发器的输出clk2m_ob上偶尔有毛刺出现,但是触发器的输入F1和F0上并没有毛刺。而且这个毛刺和下一个clk2m_ob跳变沿的间隔刚好是50MHz的一个周期20nS。参考图4,红色为F1,黄色为clk2m_ob。

我们来分析下这个毛刺。由于2MHz输入信号local_2m和50MHz时钟clk_50m是异步的,因此毫无疑问会有亚稳态的出现。当亚稳态出现的时候,触发器的输出一开始随机震荡到高电平,但很快亚稳态结束,并返回到”错误的”低电平状态。于是就表现为毛刺。如果想从门电路角度解释为什么会出现毛刺,可以参考文献[Metastable Response in 5-V Logic Circuits].

在测试中,每大约一小时,clk2m_ob就会出现一次这样的毛刺。可以看出亚稳态的捕捉窗口是非常小的。这个实验中大约发生了 60 minutes * 60 seconds/20nS = 180*10^9次采样。因此捕捉窗口的大致范围为20nS * (2/25) / (180*10^9) ~= 9 *10^(-12) s = 9 fs. 这么高的精度,没有任何仪器可以精确模拟,这也是为什么亚稳态现象只能用统计的方法去研究的原因。

另一方面,同样的电路功能,clk2m_oa却从来没有出现过这样的毛刺。这说明亚稳态表现形式不是固定的。猜测clk2m_oa的亚稳态表现为中间电平的形式,并最终返回到”正确”的状态。由于tR时间非常短,并且亚稳态和信号的边沿混和在一起,无法和正常情况进行区分。根据XAPP094【Xilinx,Metastable Recovery in Virtex-II Pro FPGAs】的解释,亚稳态的表现是和器件的PVT(制作工艺Process,电压Voltage,温度Temperature)相关的,并且和具体电路的增益,噪声相关。如果是这样,clk2m_oa和clk2m_ob的各自触发器的或增益或噪声是有差异的,所以表现不一致。

3、亚稳态返回到哪一个稳定态是不可预测的,而且和输入数据无关。

亚稳态返回到哪一个稳定态是不可预测的,和输入数据无关。因此假设亚稳态较快的返回,目的寄存器(destination FF)能够采样到稳态电平,也可能采样到错误的电平,导致系统功能错误。

亚稳态的危害

目前主流的FPGA都是基于同步设计思想。一个良好的子模块设计都是同步于同一个时钟的子系统。当不同时钟域的多个模块进行通信时,就可能会发生亚稳态。

另外,同一个时钟域内,如果时序不满足,比如由于组合逻辑和走线的延时过大,导致源寄存器的跳变到达目的寄存器的时刻刚好位于时钟的跳变沿,也会发生亚稳态。当然,在同步模块中,对于一个时序收敛良好的设计,不会存在亚稳态的情况。

理论上讲,如果亚稳态不能够在一个时钟周期内返回到稳定态,那么目的寄存器也会发生亚稳态。这就是亚稳态的传播。

亚稳态的毛刺直接输出,有可能导致系统错误。比如毛刺信号送给CPU做中断,可能导致CPU产生错误的中断响应。

采样到错误的电平,导致功能错误。这是逻辑设计人员最容易遇到的问题。最典型的例子是,假设有一个4bits one-hot编码的状态机。正常的功能只有四个状态0,2,4,8。但是这个状态机有多个异步输入信号,那么就会发生亚稳态。我们知道,亚稳态返回到1或者0是随机的,这样就会出现状态机的输入有非法的组合,导致状态机进入到非法状态{1,3,5,6,7,9,10….}。如果状态机没有安全编码保护,状态机就会挂死在非法状态。

破坏Block RAM的内容。在读取RAM时,如果生成读地址的时钟和RAM的读时钟是异步的,那么读取也会破坏RAM的内容。基本上是因为读RAM会伴随一个自动的回写动作,这是大多数CMOS FPGA的特性。回写的时候,由于在地址上发生了亚稳态,导致某一个地址的内容回写到了另外的地址上,从而破坏了RAM的内容。

亚稳态的处理

理论上讲,异步信号输入到一个同步系统,亚稳态是不可避免的。现实问题是如何降低亚稳态带来的危害,如何降低亚稳态发生的概率。

亚稳态最终会返回到稳定态,因此只要等足够的时间,就可以免受亚稳态的危害。亚稳态返回的时间tR(resolution time)是个很复杂的问题,取决于系统的MTBF【Understanding Metastability in Altera FPGAs中有详细计算方法】要求和器件本身。总的来说是很短的。对于90nm或者更小的工艺,在可以接受的MTBF如10年内,tR大约在1nS左右;MTBF如1000年内,tR大约在2nS左右,具体可以咨询相应的FPGA制造商。

1、降低亚稳态发生的概率。

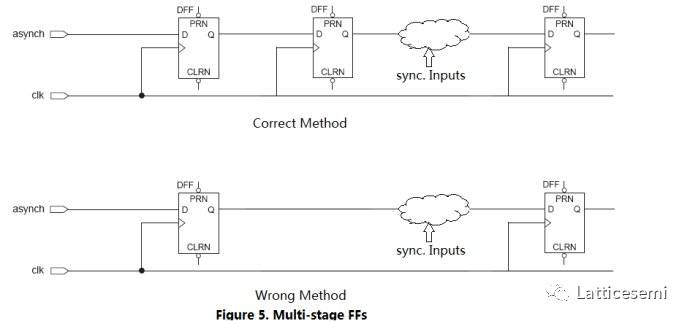

经典的处理方法是多拍同步。参见图5的Correct Method.

异步信号经过第一个寄存器,如果发生了亚稳态,2nS(假设MTBF=1000Y)左右返回到稳定态,如果时钟周期大于2ns(时钟频率小于500MHz), 那么显然第二个寄存器就没有亚稳态发生了。此时亚稳态的唯一影响就是不能在最准确的时刻识别到异步信号,有可能早一拍,或者晚一拍识别。

多说一点,为了处理亚稳态,识别异步信号需要的时间就较长(2拍或者更多),这就是目前流行的同步设计的代价。异步设计较好的解决了这个问题,异步设计靠硬件握手机制来反馈什么时候识别成功。

作为对比,我们看看图5中的wrong method。第一拍触发器在接收异步信号后,产生了亚稳态。由于经过了组合逻辑和走线的延时,亚稳态传播到目的寄存器的时间增大很多。这种情况下,只有在很低速的时钟频率时,第二拍触发器才可以避免亚稳态。因此是不正确的处理方法。

2、降低亚稳态带来的危害。

一个良好的设计必须有好的容错能力,让设计对亚稳态不敏感。如果亚稳态出现,至少要有能力恢复。

状态机如果有异步信号输入,一定要多拍处理异步信号,并且使用安全状态机,任何情况下不可以让状态机挂死在非法状态。

异步接口不可能做到准确地定时,在预算精度时,必须容忍+/-1拍的延时。

异步FIFO两个时钟域的地址交互时,使用格雷码计数器并多拍处理, 可减低对亚稳态的敏感.

能用低的频率实现的功能,不要用高的频率。频域较高时,要用三拍或者更多的触发器来降低亚稳态的危害。

较陡的信号边沿(包括数据和时钟)有利于降低发生亚稳态的概率。

小结

参考阅读:

![]() MetastabilityinMACHDevices.PDF

MetastabilityinMACHDevices.PDF

![]() Understanding Metastability in Altera FPGAs.pdf

Understanding Metastability in Altera FPGAs.pdf

![]() Metastable Response in 5-V Logic Circuits.pdf

Metastable Response in 5-V Logic Circuits.pdf