FPGA定点小数计算(Verilog版)第四篇——定点小数转换为浮点小数

0赞

发表于 2017/10/9 10:31:53

阅读(5883)

用FPGA实现定点运算,相对于浮点运算来说,开销要小很多(时间上和空间上的)。但是在某些特定的场合,如多机协同处理等,要求FPGA的输入数据(或者是输出数据)为浮点形式的数据,这是就需要我们来做一个浮点小数与定点小数之间的转换了。

本文为本次定点小数相关博文连载的第四篇,后面的写作计划分别为:第五篇——浮点小数转换为定点小数;第六篇——平方根运算(查表法);第七篇——平方根运算(牛顿迭代法,使用John Carmack方法)。

和前面一样的套路,开始贴图模式:

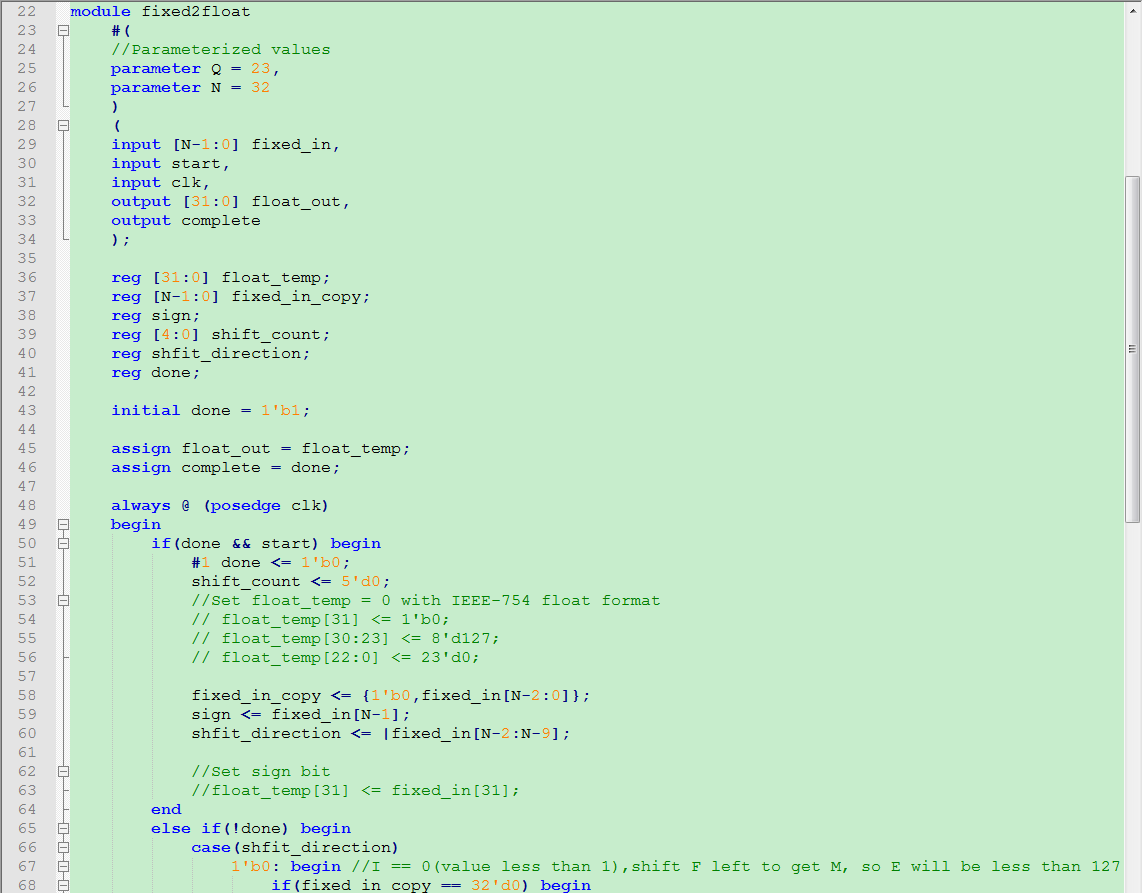

首先是fixed2float.v:

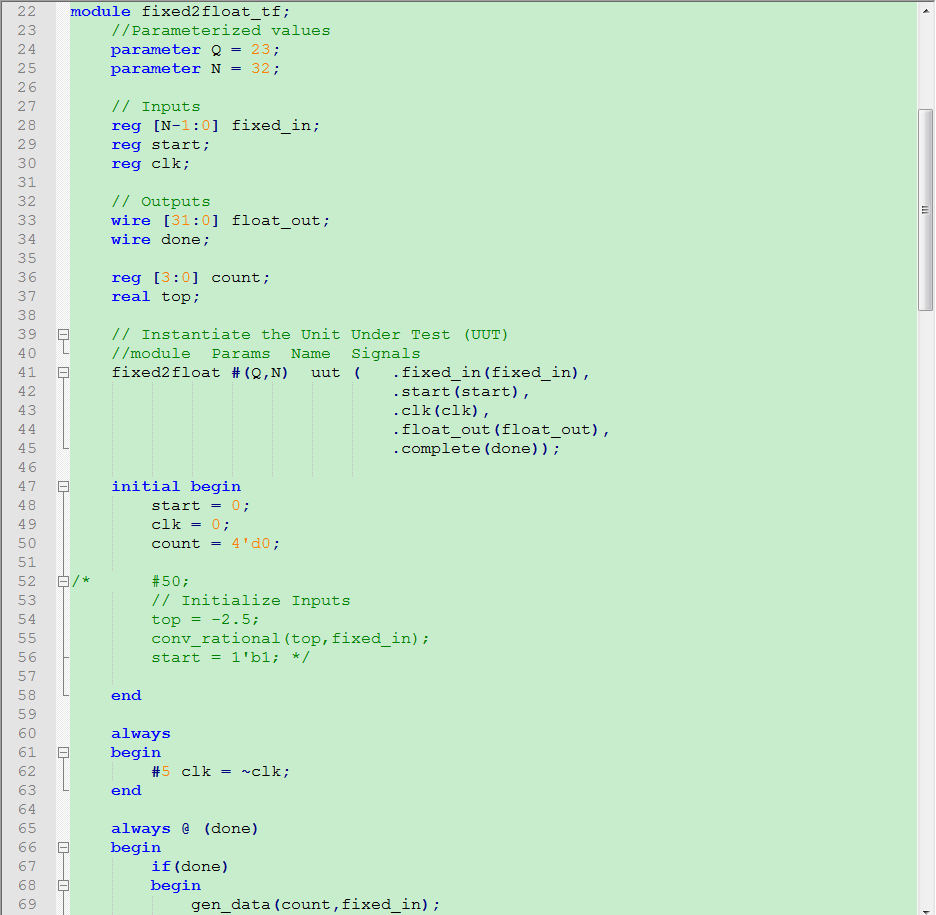

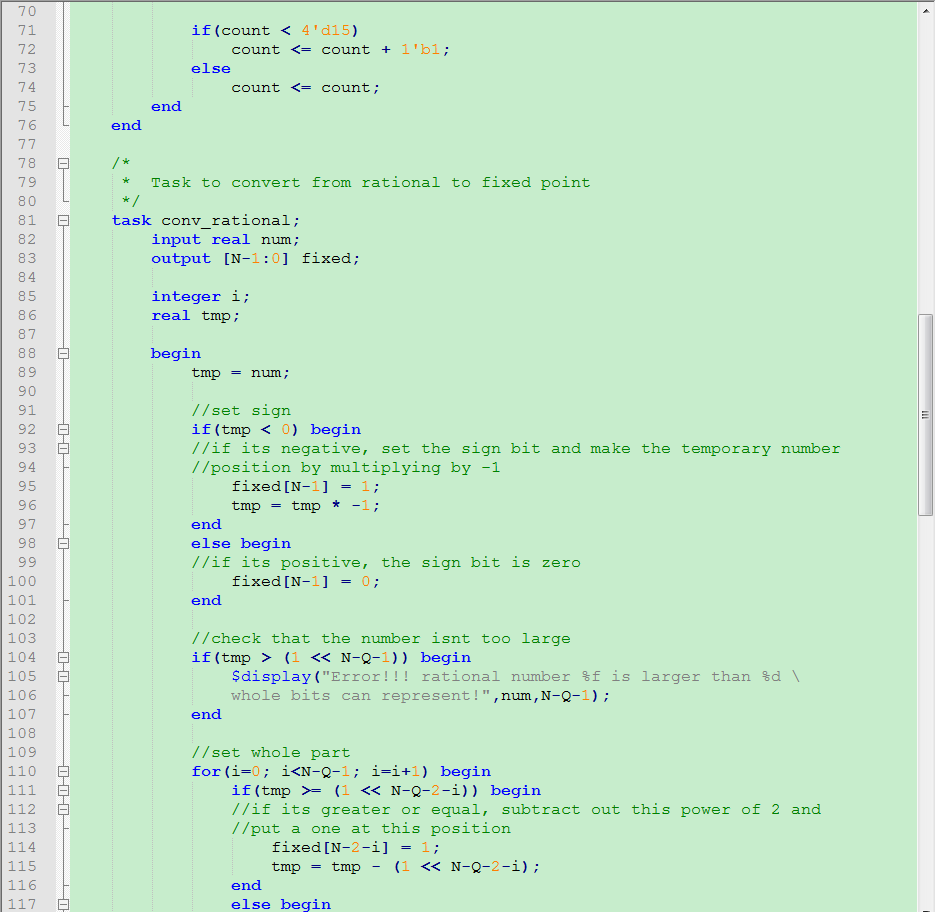

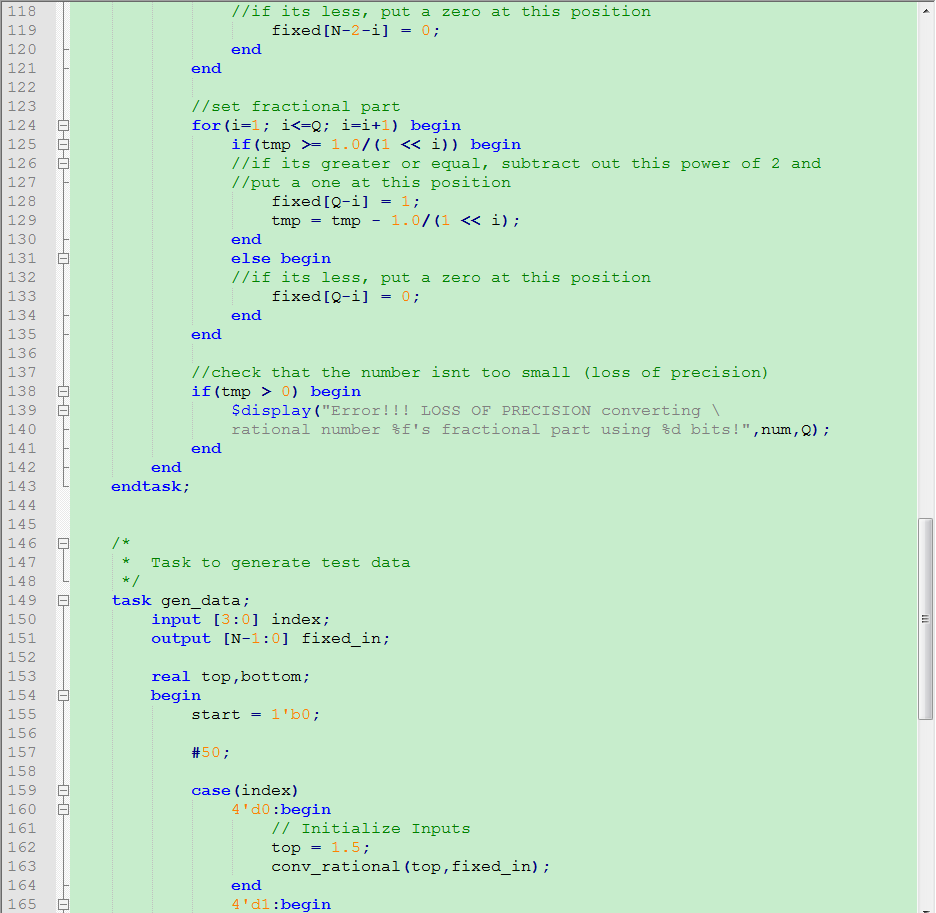

然后是Testbench:

使用Syplify Pro综合获得的RTL视图:(太长了,贴了也看不清楚,所以不贴了!)

使用Diamond综合得到的:

Design Summary Number of registers: 71 out of 83994 (0%) PFU registers: 40 out of 83640 (0%) PIO registers: 31 out of 354 (9%) Number of SLICEs: 62 out of 41820 (0%) SLICEs as Logic/ROM: 62 out of 41820 (0%) SLICEs as RAM: 0 out of 31365 (0%) SLICEs as Carry: 0 out of 41820 (0%) Number of LUT4s: 92 out of 83640 (0%) Number used as logic LUTs: 92 Number used as distributed RAM: 0 Number used as ripple logic: 0 Number used as shift registers: 0

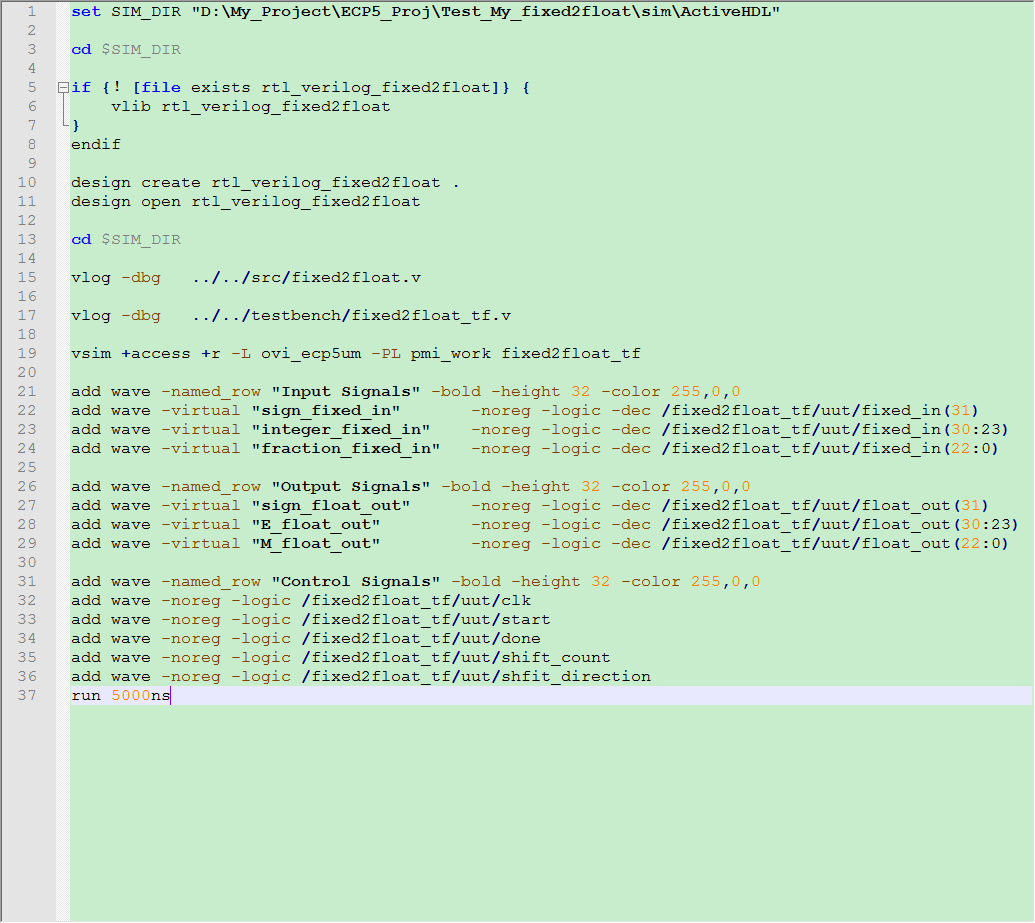

下面是ActiveHDL的脚本文件:

功能仿真的波形图如下: