MIPI扫盲——Lattice CSI-2 / DSI DPHY Receiver IP介绍

0赞目录篇地址:http://blog.chinaaet.com/justlxy/p/5100052503

Clarity提供的MIPI D-PHY IP主要有两种,一种是Module(不需要License),另一种是正式的IP(需要License)。如下图所示:

其中Module中的提供的mipi_phy和下面圈出来的两个IP都能够实现CSI-2和DSI的收发功能,但是IP的功能要更加强大一点,提供了可供仿真验证的工程给用户,并增加了很多的调试信号,而这些Module中的mipi_phy是没有的。从实现的难度来说,使用mipi_phy要更加困难一点,同时也更加灵活一点。需要注意的是,无论是Module还是IP,无论是CSI-2还是DSI,Receiver可以使用硬核或者软核,但是Transmitter只能使用硬核来实现。

如本文标题所示,下面将要介绍的是IP中的CSI-2/DSI D-PHY Receiver的基本特性和注意事项。

CSI-2/DSI D-PHY Receiver IP(下称该IP)是基于MIPI D-PHY v1.1、MIPI CSI-2 v1.1和MIPI DSI v1.1版本开发的。各种配置(模式)下,资源使用情况和性能如下图所示:

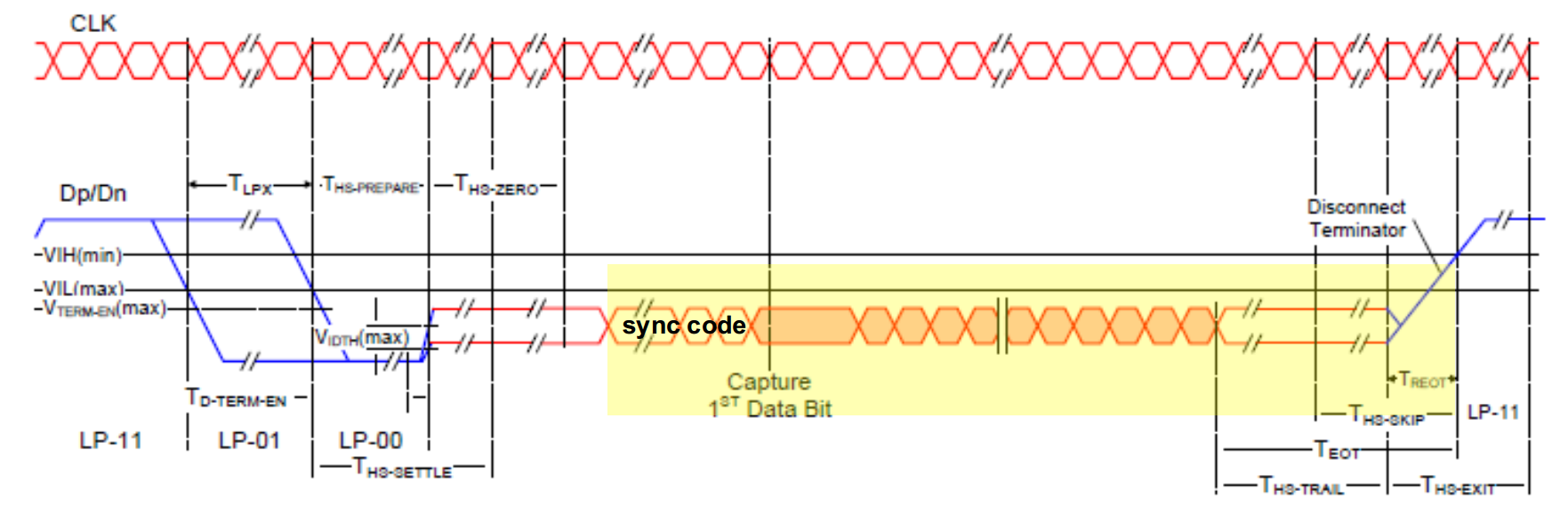

这里需要说明一下的是,Gear8表示每个Data Lane每个字节时钟周期传输一个字节数据,而Gear16则表示每个字节时钟周期传输两个字节数据。因此,两种情况下的同步码(Sync code,即前面文章提到的Sync-Sequence ‘00011101’,按照正常的字节顺序就是8'hB8),Gear8是8'hB8,而Gear16是8'hB800。Sync code在SoT之后,如下图所示:(如不理解,可以查看之前的相关文章)

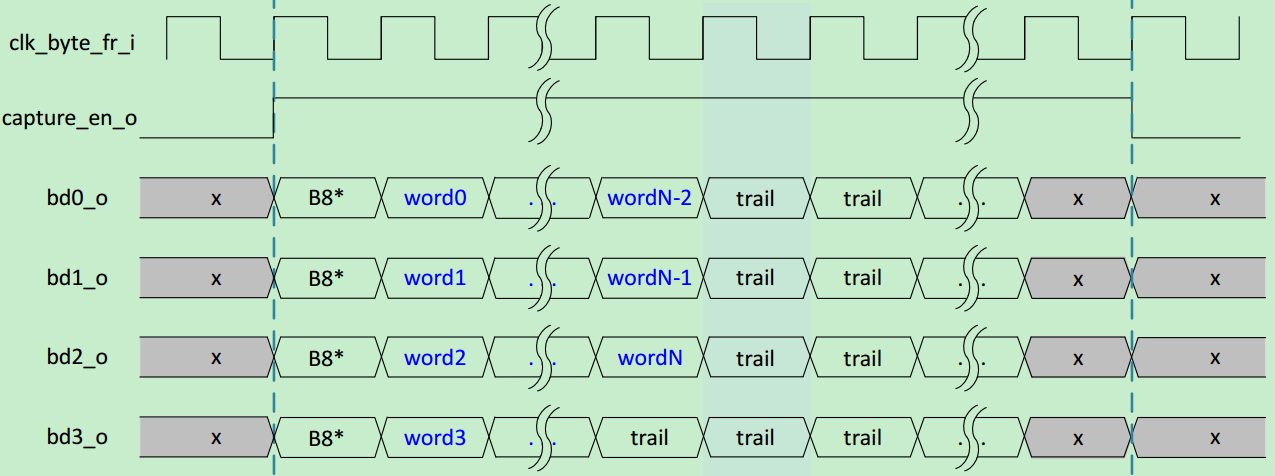

Fabric Interface端的数据波形图如下,其中capture_en_o表示bdx(0,1,2,3)的有效信号(包括了同步码和trail code,一般是8'hFF或者16'hFFFF)。

需要注意的是,正常情况下,必须保证在一个完整的周期里所有的bdx上的信号均为trail code,方可完成一次数据的接收。

为了方便调试,该IP还支持Packet Parser功能,通过Packet Parser可以实现对接收到的数据的数据类型进行检验。这里就不详细介绍了,有兴趣的可以参考本文最后的参考资料部分所提供的文档,或者到Lattice的官网上做进一步了解。

此外,该IP还实现了一个对齐模块(Aligner Modules),可以实现字节对齐(Word Aligner)和通道对齐(Lane Aligner)。具体如下图所示:

主要参考资料: