8B / 10B Encode/Decode详解

0赞1、编码技术基础理论

在高速的串行数据传输中,传送的数据被编码成自同步的数据流,就是将数据和时钟组合成单一的信号进行传送,使得接收方能容易准确地将数据和时钟分离,而且要达到令人满意的误码率,其关键技术在于串行传输中数据的编码方法。

目前, 高速接口正在被广泛应用于包括 SATA、 SAS、 高速 PCI 等多种标准中。 这些接口的速率甚至可以达到并超过每线 10Gbits/s。 同时, 所有主流 ASIC 和 FPGA 平台也都支持这些高速接口技术。 从结构上看, 这些高速接口主要包括三个组成部分:

1) 电路部分(串行/解串行)

2) 物理部分(实现编码)

3) 链路与协议部分(高层)

支持多速率、 多协议的串行/解串行器已经实现。 以 OIF(光互联论坛) 为例, 他们已经为两组速率制定了电路规范, 分别为 5Gbits/s- 6.375Gbits/s 和 10Gbits/s-11Gbits/s。 OIF 同样为两种应用距离制定了规范, 分别为短距离(采用一个连接器, 8 英寸) 和长距离(采用两个连接器, 40 英寸)。 串行/解串行器还可以被设计用来满足更多的规范, 包括不同的速率、距离、 电路规格等等。

物理部分的主要任务是对数据进行编码, 以保证串行/解串行器的正常运行。 这些编码的目的包括: 确保必须的变换(“1” 到“0” 和“0” 到“1” 的变换), 保证稳定的直流均衡(“0” 码与“1” 码的个数相当), 以及满足其它标准的要求(最大化信道带宽利用率, 提高对误差的容忍能力等等)。

在光纤通信中, 线路编码是必要的, 因为电端机输出的数字信号是适合电缆传输的双极性码, 而光源不能发射负脉冲, 只能用光脉冲的“有” 和“无” 来表示二进制码中的“1”和“0"。 该方法虽然简单, 却存在三个问题:

1)遇到数字序列中出现长连“0” 或长连“1” 时, 将给光纤线路上再生中继器和终端光接收机的定时信息提取工作带来困难;

2)简单的单极性码中含有直流分量。 由于线路上光脉冲中“1” 和“0” 是随机变化的,这将导致单极性码的直流成分也作随机性的变化。 这种随机性变化的直流成分, 可以通过光接收机的交流耦合电路引起数字信号的基线漂移, 给数字信号的判决和再生带来困难;

3)不能实现不中断通信业务下的误码检测;

为解决以上问题, 通常对于由电端机输出的信号码流, 在未对 LED(或 LD)调制以前,一般要先进行码型变换使调制后的光脉冲码流由简单的单极性码,转换为适合于数字光纤传输系统传输的线路码。 适合于光纤通信的线路码型有多种, 但都要满足以下要求:

1)能保证比特序列独特性。

2)能提供足够的定时信息。

由于在光纤数字传输系统的传输中, 只传送信码, 而不传送时钟, 因此在接收端, 必须从收到的码流中提取出定时信息, 以利于上述的定时提取。 必须限制线路码流中同符号连续数不能过大, 也就是说, 应避免长连“0” 及长连“1” 的出现, 提高电平跳变的密度, 使定时提取较为简单。

3)减少功率密度中的高低频分量。

线路码的功率谱密度中的低频分量是由码流中的“0”、“1” 分布状态来决定的, 低频分量小, 说明“0”、 “1”分布比较均匀, 直流电平比较恒定, 也就是信号基线浮动小, 有利于接收端判决电路的正常工作。 高频分量是由线路码的速率决定的, 这在带宽(色散)限制系统中特别值得注意, 在这种系统中, 中继距离主要由光纤线路的总带宽(总色散)决定, 如果线路码速率提高的太多, 会使中继距离大大缩短。

4)要有利于减少码流的基线漂移, 即要求码流中的“1"、 "0” 码分布均匀, 否则不利于接收端的的再生判决。

5)码率增加要少, 光功率代价要低。

6)接收端将线路码还原后, 误码增殖要小。

线路传输中发生的一个误码, 往往使接收端的解码(反变换)发生多个错误, 这就是误码倍增, 也叫做误码扩展或误码增值。 由于误码倍增, 使光接收机要达到原要求的误码性能指标, 必须付出光功率代价, 即光接收机灵敏度劣化。 因此误码倍增系数越小越好。

7)能提供适当的冗余度。

8) 低的对称抖动。

传输的比特序列必须保持低的码型相关的抖动。

9)易于实现。

数字光纤通信系统中常用的线路码型有:加扰二进码、 插入比特码和 mBnB 码。

2、8B/10B 编解码原理

8B/10B编码最初由IBM公司的Albert X.Widemer和Peter A.Franaszek发明,并应用于ESCON(200M互连系统)中。 它是mBnB编码中的一个特例。

8B/10B编码方法是把8bit代码组合编码成10bit代码,代码组合包含256个数据字符编码和12个控制字符编码,分别记为Dx. y和Kx.y。 通过仔细选择编码方法可以获得不同的优化特性。 这些特性包括满足串行/解串行器功能必须的变换; 确保“0” 码元与“1” 码元个数的一致, 又称为直流均衡; 确保字节同步易于实现(在一个比特流中找到字节的起始位); 以及对误码率有足够的容忍能力和降低设计复杂度。

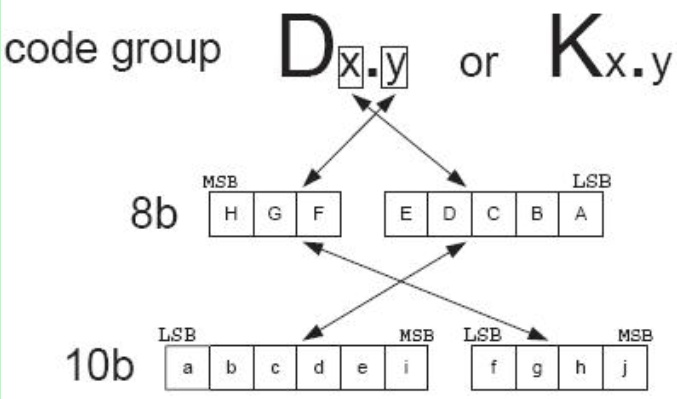

8B/10B编码方案是把8bit数据分成2个子分组: 3个最高有效位(y)和5个最低有效位( x)。 代码字按顺序排列,从最高有效位到最低有效位分别记为H、 G、 F和E、 D、 C、 B、 A。 3bit的子分组编码成4 bit,记为j、 h、 g、 f; 5 bit的子分组编码成6bit,记为i、 e、 d、 c、 b、a,其映射关系如图1所示,4bit和6bit的子分组再组合成10bit的编码值。

图1 8B/10B码编码原理图

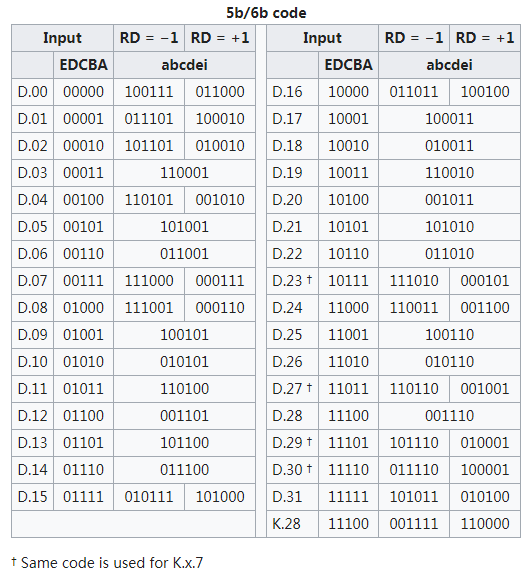

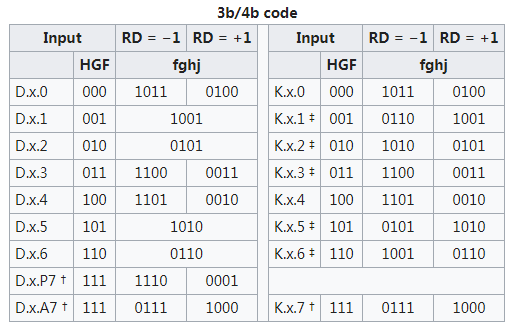

将8bit数据分成3bit和5bit两组,分别对应10bit中的4bit和6bit,直流平衡代码的不平衡度就是通过“0” 的个数减去“1” 的个数来计算得到的。 如果4bit和6bit的各分组中“0”和“1” 的个数相等,称为完美平衡代码,或称为完美的直流平衡代码,无需补偿,但是这种情况是不可能的。 因为在4bit的子分组中,16种编码中只有6 种是完美平衡的,这对于3bit的8种编码值是不够的。 同时,在6bit的子分组中也只有20种编码是完美平衡的,对于5bit的32种编码值也是不够的。 由于4 bit和6bit的两个子分组都是偶数个位数,而不平衡度不可能是“+1” 或“-1”,因此,在8B/10B编码方案中还要使用不平衡度为“+2” 和“-2” 的值。 在编码过程中,用一个极性偏差( running disparity,RD)参数表示不平衡度,在不平衡时用2个10 bit字符表示一个8位字符,其中一个称为RD- ,表示“1” 的个数比“0” 的个数多2个,另一个称为RD+ ,表示“0” 的个数比“1” 的个数多2个。如下图所示:

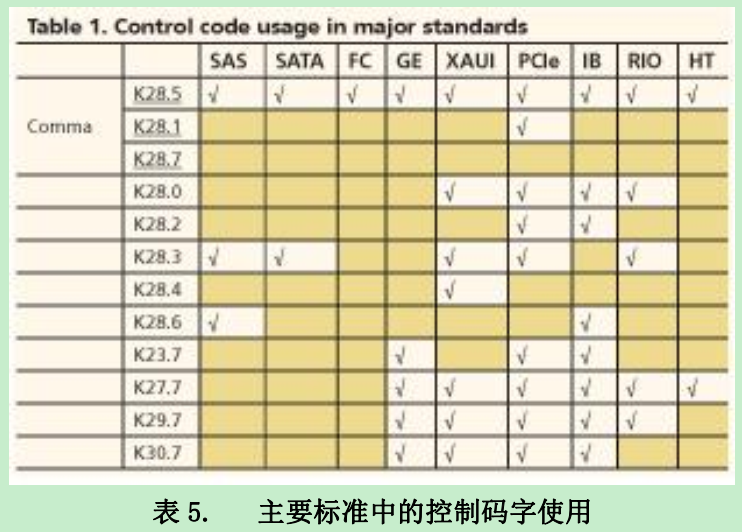

8B/10B编码中将K28.1、K28.5和K28.7作为K码的控制字符,称为“comma”。在任意数据组合中,comma只作为控制字符出现,而在数据负荷部分不会出现,因此可以用comma字符指示帧的开始和结束标志,或始终修正和数据流对齐的控制字符。

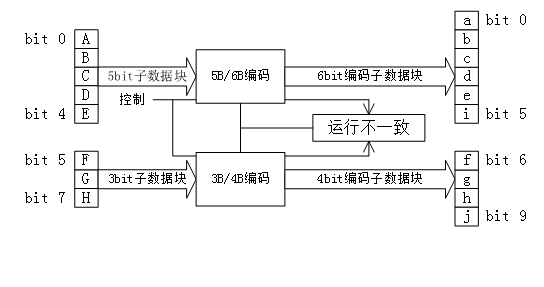

编码时,低5bit原数据 EDCBA经过5B/6B编码成为6bit码abcdei,高3bit原数据HGF经3B/4B成为4bit码fghj,最后再将两部分组合起来形成一个10bit码abcdeifghj。10B码在发送时,按照先发送低位在发送高位的顺序发送。

5B/6B编码和3B/4B编码的映射有标准化的表格,可以通过基于查找表的方式实现。使用 “不一致性(Disparity)”来描述编码中"1"的位数和"0"的位数的差值,它仅允许有"+2"( "0"比"1"多两个)、"0"( "0"与"1"个数相等)以及"-2"("1"比"0"多两个)这三种状况。 由于数据流不停地从发送端向接收端传输,前面所有已发送数据的不一致性累积产生的状态被称为“运行不一致性(Runing Disparity,RD)”。RD仅会出现+1与-1两种状态,分别代表位"1"比位"0"多或位"0"比位"1"多,其初始值是-1。Next RD值依赖于Current RD以及当前6B码或者4B码的Disparity。根据Current RD的值,决定5B/4B和 3B/4B编码映射方式,如下图所示。

这样,经过8B/10B编码以后,连续的“1”和“0”基本上不会超过5bit,只有在使用comma时,才会出现连续的5个0或1。接收端的数据解码过程如下图所示:

3、8B/10B 码的优势

8B/10B编码技术编码之所以能得到广泛应用,主要在于它较好地解决了以下问题。

(1) 转换密度:

保证数据流中有足够的信号转换。 采用8B/10B编码方法,数据流中连续的“1” 或连续的“0”不超过5个,使接收端锁相环( PLL)能正常工作,避免接收端时钟漂移或同步丢失而引起数据丢失。 保证了1和0的相对平衡组合,而与数据值无关,简化了时钟恢复,降低了接收机成本。

(2)DC补偿:

在高速的数据传输线路中,一般采用差分信号,需要直流分量尽量小,而8B/10B有DC补偿功能,即链路中不会随着时间推移而出现DC偏移。

(3)检错:

8B/10B编码采用冗余方式,将8位的数据和一些特殊字符按照特定的规则编码成10位的数据,根据这些规则,能检测出传输过程中单个和多个比特误码。

(4)特殊字符:

8B/10B编码规定了一些特殊字符,可用作帧同步字符和其他的分隔符或控制字符, 有助于比特流的码组定位和信息识别。 许多独立标准都以这个公共字符集为基础,定义更高的协议层:

(5)链路灵活性:

由于采用 8B/10B 编码, 链路可以是交流(AC)耦合的, 这样就给任一端的设备厂商提供了更大的灵活性。

4、8B/10B 码的实现与应用

进行编解码设计时通大体下面几种方法。

第一种是用查找表直接将8位信号映射成10位信号,该方法用存储器存储所有可能出现的码组,再将输入码组转换为存储地址,找出对应的编解码。 方法逻辑简单,开发时间很短,但是编解码电路的工作速度受到FPGA内部存储器读取时间的限制,同时不可避免地增加了芯片的面积和功耗。

第二种是通过逻辑运算直接完成编解码功能对,该方法的优点是可以明显减小内部使用面积,难点在于逻辑关系复杂。如果采用卡诺图直接化简则会产生大扇入逻辑表达式,大大限制电路的最高工作速度,同时对逻辑电路的驱动也将加大电路功耗。

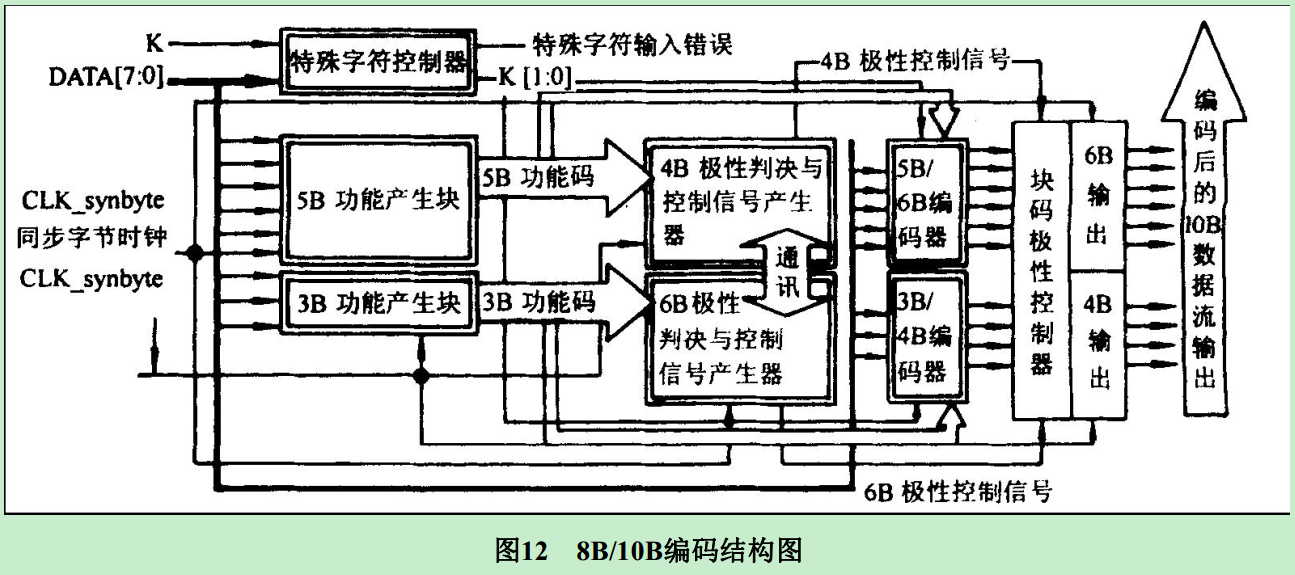

第三种是,8B/10B编码模块化实现,较好地反映了8B/10B编码的特点,实现流程清楚。 实现步骤:

①判断是特殊字符还是数据;

②若是特殊字符,根据RD极性直接取值;

③若是数据,把一节8位字节拆成3bit和5bit,然后在RD控制器的控制下以并列的方式编/译码。 RD控制器的原则是: 系统设定的RD默认初始值为RD-, RD的初值作为选择信号用以决定5B/6B编码模块中6B码的选取, 同时由所选取的6B码计算出新的RD值作用于3B/4B编码模块。 4B编码所得到的RD值又作为下一组编码的RD输入值, 由此完成了全部的8B/10B编码。

这种方法的组合逻辑实现可以简化码表、 减小电路板的面积、 有效提高编码工作速度。同时由于电路板的面积减小,功耗也显著降低。

目前大多数高速串行标准都采用8B/10B编码方案,例如串行连接SCSI、 串行ATA、 光纤链路、 吉比特以太网、 XAUI(1吉比特接口)、 PCI Express总线、 InfiniBand、 Serial RapidIO、HyperTransport总线、 DVB-ASI以及IEEE1394b接口(火线) 技术中。

参考阅读:

2、百度百科:https://baike.baidu.com/item/8B%2F10B/9125856?fr=aladdin

3、http://blog.csdn.net/hit_wzj/article/details/50403243

4、Wiki:https://en.wikipedia.org/wiki/8b/10b_encoding