一种借助EBR实现数据延时的方法

0赞

发表于 3/11/2018 8:33:24 PM

阅读(4149)

数据延时线(Delay Line)在数字信号处理中具有广泛的应用,例如FIR滤波器设计中就会需要用到数据延时线。实际上,在绝大部分的Pipeline设计中都会需要用到数据延时。本文介绍一种基于EBR(Embedded Block RAM,Xilinx叫做BRAM,Altera叫做Embedded memory)的数据延时的实现方法。

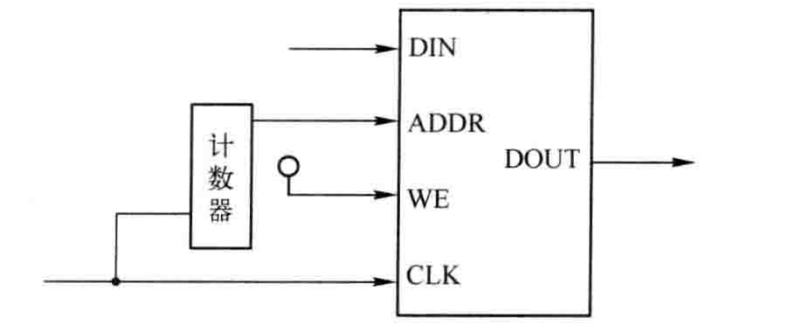

如下图所示:

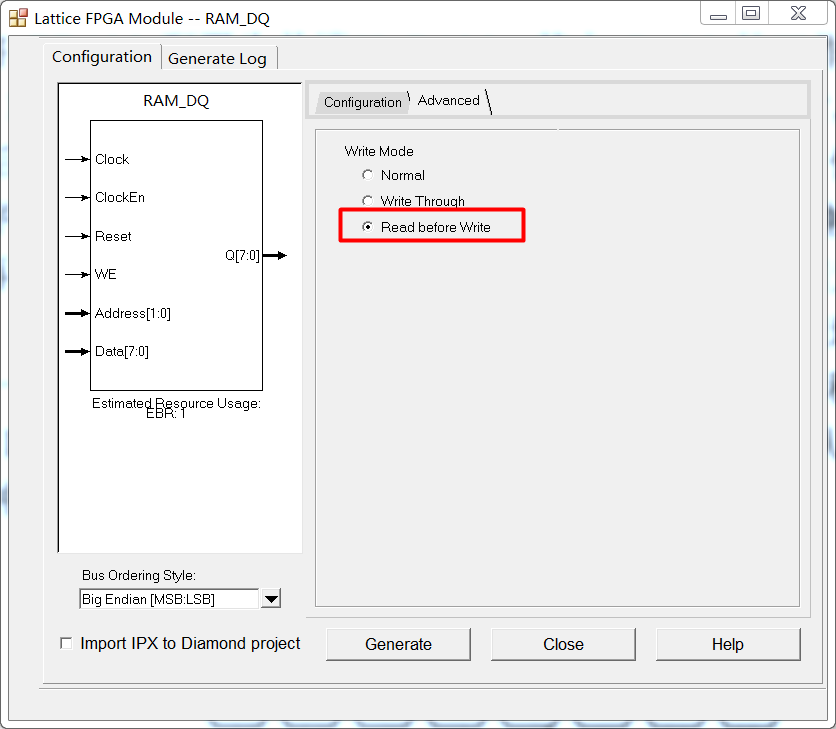

将EBR配置为单端口的RAM(即RAM_DQ),其中,Write Mode配置为Read before write。即同时对同一地址进行读写操作时,将首先读取出改地址空间的原有数据,然后在将新的数据写入到该地址空间中。如下图所示:

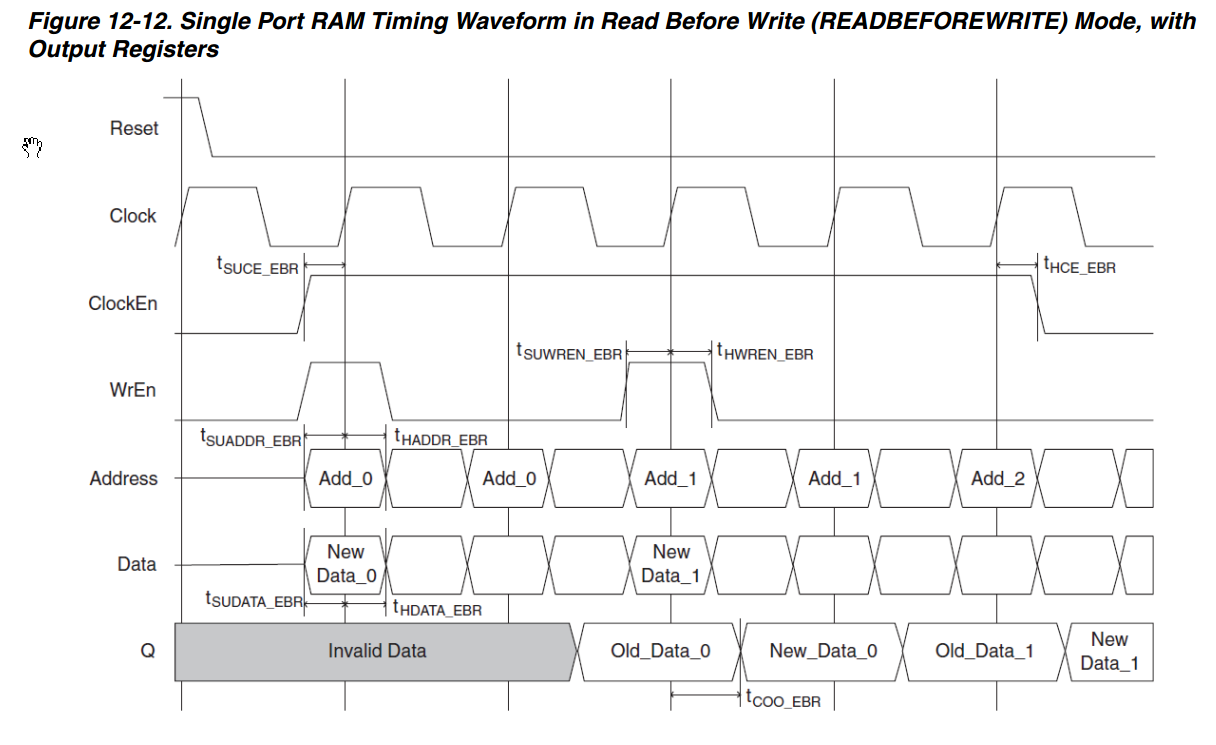

此模式下的波形图为:

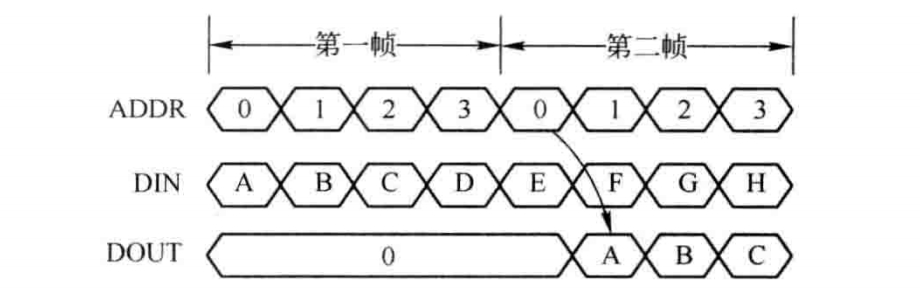

假定计数器模为4,并将WE信号接高电平,RAM的初始值为0,则相应的时序图如下图所示:

在第一帧地址内,从0号地址读出的数据为0,再将数据A写入0号地址中,从1号地址读出的数据为0,再将数据B写入1号地址。类似的,数据C和数据D分别被写入到2号地址和3号地址中。在第二帧地址内,从0号地址读取出的数据即为在第一帧地址内写入的数据A,类似的,从1~3号地址中读出的数据分别为B,C和D。由于我们使能了输出寄存器,所以从输入端DIN到输出端DOUT一共有5级时钟周期的Latency。