Sub-LVDS介绍以及Lattice FPGA对Sub-LVDS的支持

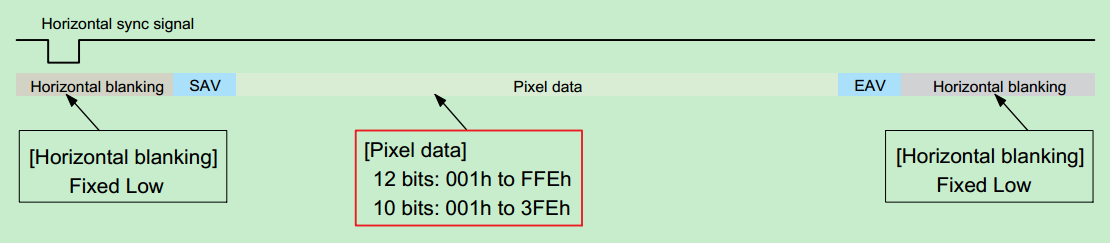

1赞Sub-LVDS是LVDS技术在Camera接口上的一种应用,相比于标准的LVDS信号,Sub-LVDS的电压更低(共模电压1.8V,差模电压150mV)。目前,Sub-LVDS技术在Sony的Camera/Sensor中比较常见,主要传输的数据格式为RAW10或者RAW12。Sub-LVDS还定义了同步字,用于同步各个数据Lane(如果没有数据Lane上的同步字,将会对各个数据Lane的走线等长的要求更加严格,参考LVDS7:1、FPD-Link I技术)。SAV表示有效数据的开始,EAV表示有效数据的结束,如下图所示:

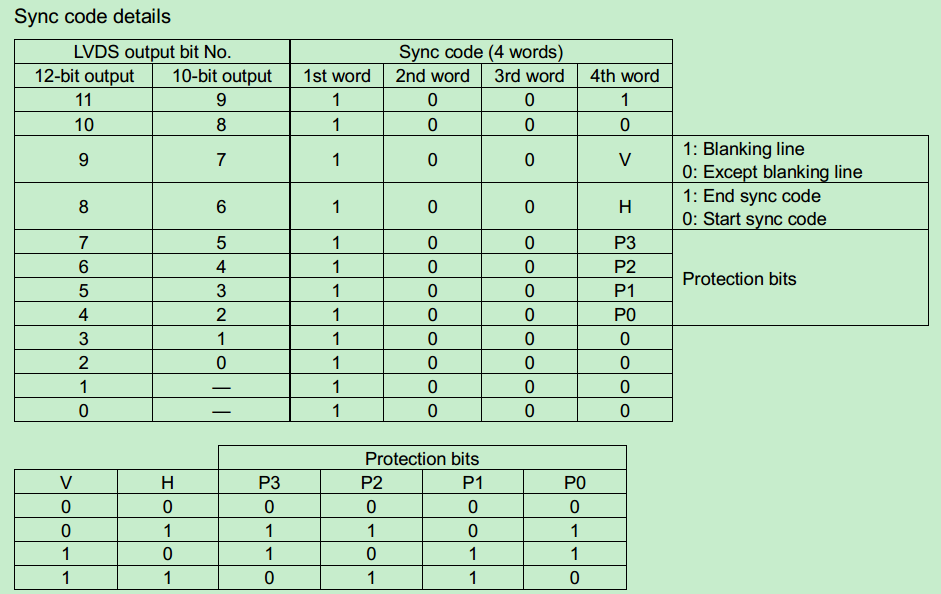

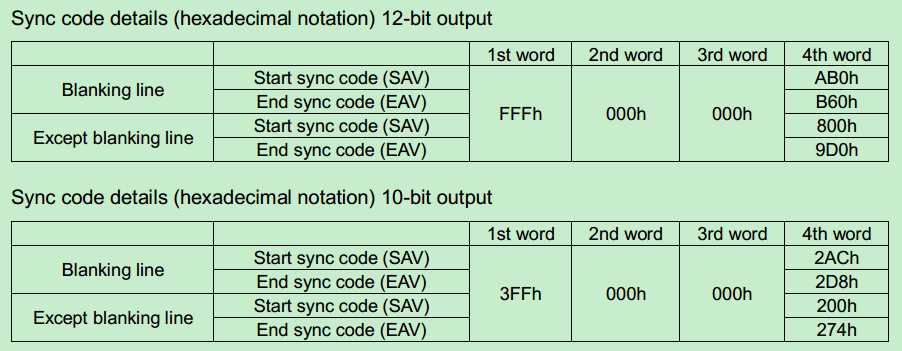

SAV/EAV的编码如下图所示:

RAW10对应的是10bit的编码,而RAW12则对应的是12bit的编码,具体如下表所示:

由于Sub-LVDS可以看做是Reduced-Voltage版本的LVDS,因此对于大部分的LVDS Rx端口来说都是可以兼容Sub-LVDS的。Lattice的MachXO2/MachXO3/ECP3/ECP5/CrossLink系列FPGA均支持Sub-LVDS的接收。如下表所示,

ECP3/ECP5可以通过SSTL18D_II和外部电阻网络的方式实现Sub-LVDS的发送,如下图所示。

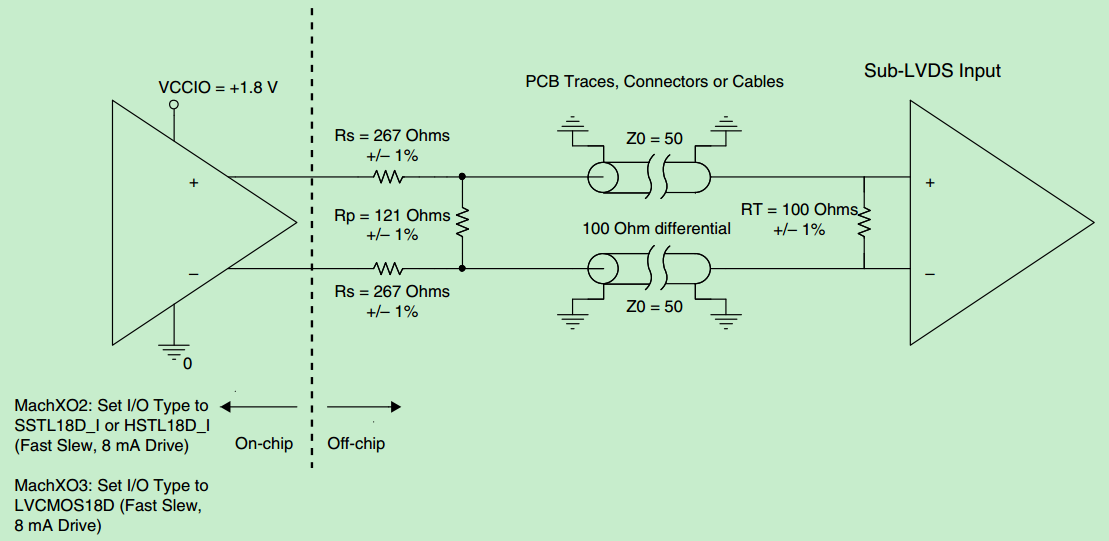

MachXO2/MachXO3的Sub-LVDS发送实现方式如下:

此外,Lattice官网上还提供了多种基于不同器件的Sub-LVDS Rx或者Bridge的参考设计/IP。

主要参考资料:

1、Lattice,Sub-LVDS Signaling Using Lattice Devices,TN1210

2、Sony,IMX274 Datasheet

3、Lattice,Sub-LVDS to MIPI CSI-2 Image Sensor Interface Bridge Soft IP UG