AMBA学习笔记——AHB总线详解

1赞AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:

1 单个时钟边沿操作(时钟上升沿);

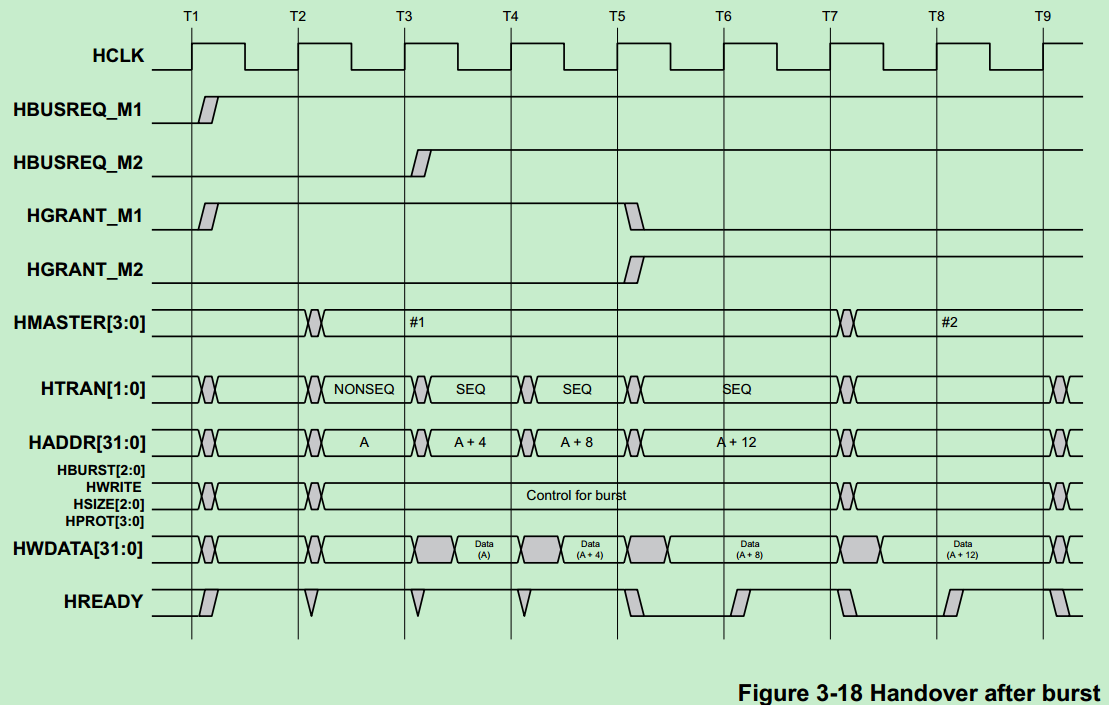

2 单时钟周期主机控制权切换(Master Handover);

3 非三态的实现方式(便于在芯片内部实现);

4 支持批量传输(Burst Transfers);

5 支持分段传输(Split Transaction);

6 支持多主机模式;

7 可配置32~256位总线宽度(AMBA Spec还允许8/16/512bits的总线宽度,不过一般应用的很少);

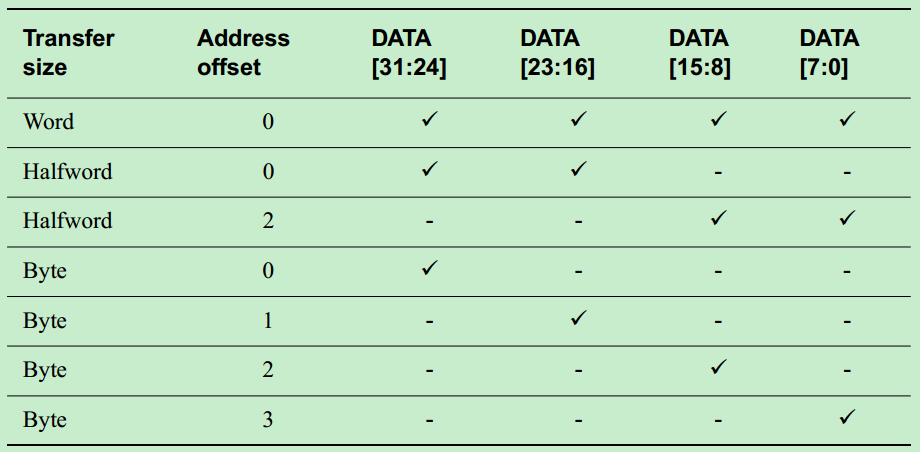

8 支持字节、半字(HalfWord=2Bytes)和字(Word=4Bytes)的传输方式。

AHB总线概述

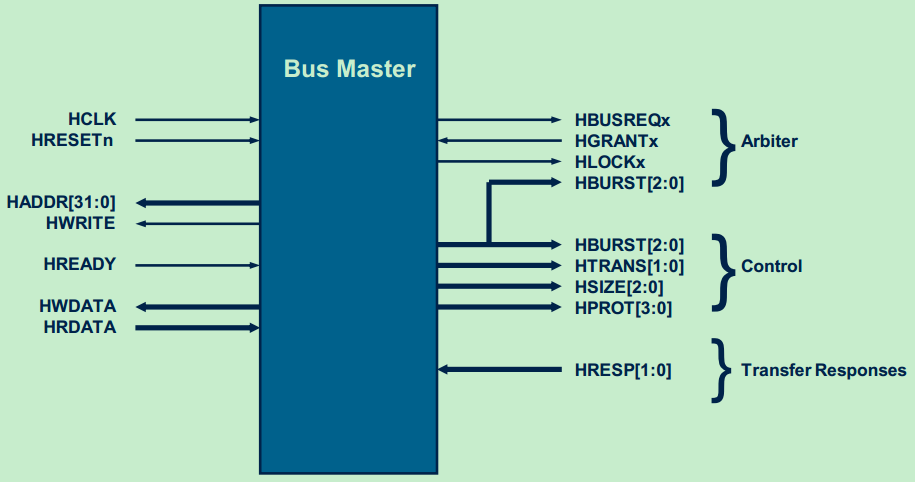

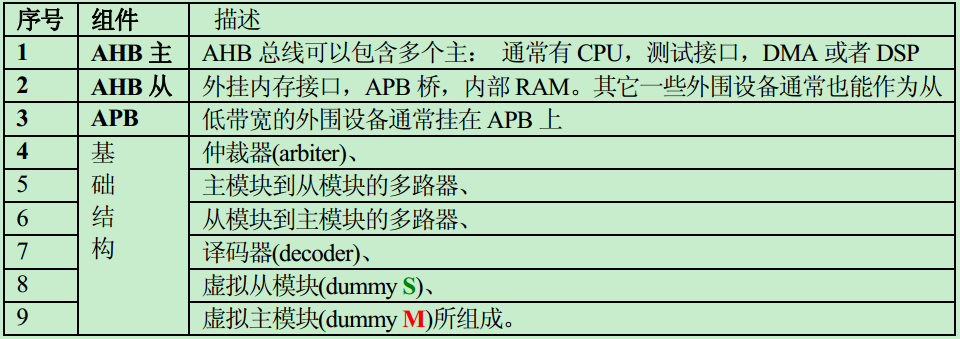

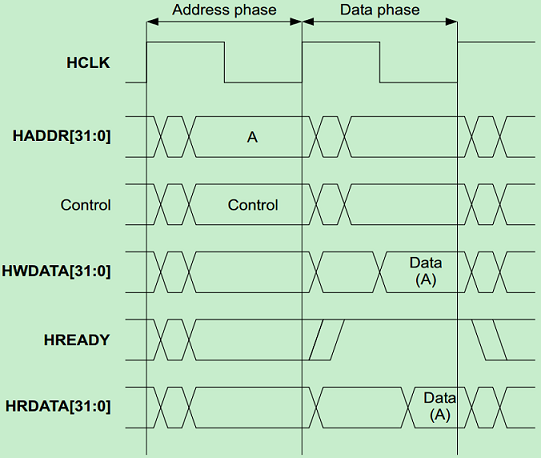

AHB系统由主模块、从模块和基础结构(Infrastructure)3 部分组成,整个AHB总线上的传输操作都由主模块发起,并由从模块负责应答。具体如下表所示:

注:M表示主机(Master),S表示从机(Slave)。

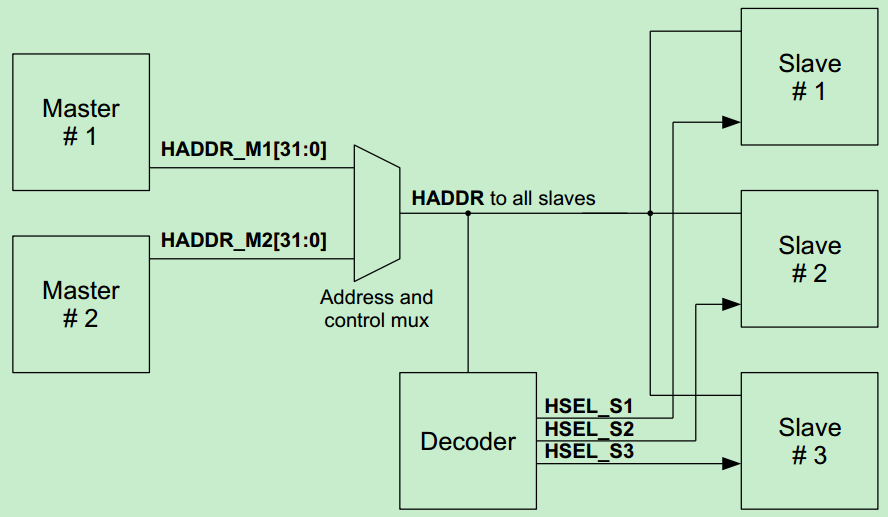

AHB中的仲裁器和解码器在多主机多从机系统的结构图如下图所示:

AHB以仲裁器(Arbiter)来控制多任务器以连接在其上的主机与从机。其操作顺序一般如下:

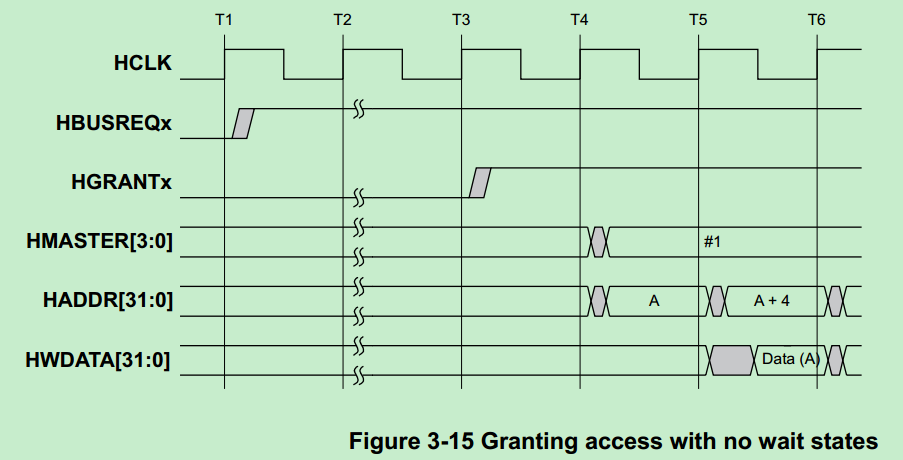

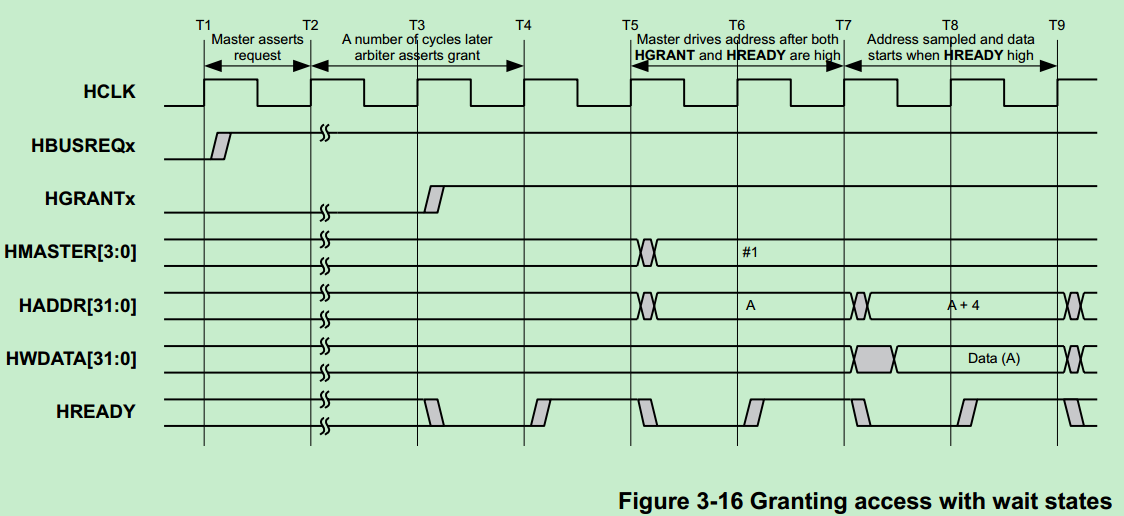

Step1. 主机(Master)通过HBUSREQx 信号向仲裁器申请总线控制权;

Step2. 裁器器(Arbiter)根据相关的优先级算法通过HGRANTx 信号响应某一个主机,并给与其总线控制权;

Step3. 主机(Master)送出地址与控制信号,开始总线传输操作。

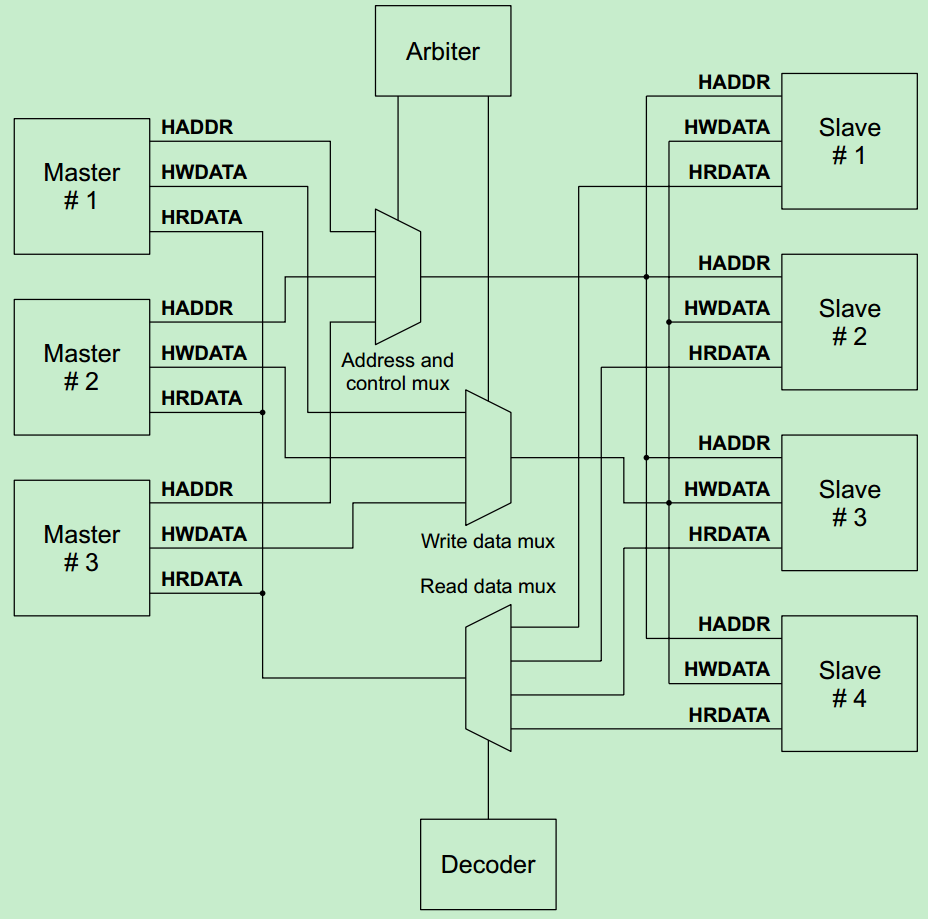

一次传输操作至少应包括 地址/控制信号周期(Address/Control)与数据周期(Data Cycle)。地址与控制信号周期最少需要一个周期,但是会因为数据的原因多出几个周期。数据周期可以通过从机拉低HREADY信号来延迟。从机拉高HREADY代表此次传输已经成功完成。

从机通过HRESP[1:0]信号来表示传输的状态:

HRESP[1:0] = 00 (OKAY):当此信号再加上从机拉高的 HREADY(OKAY+高 HREADY)就表示此次的传输已完成。

HRESP[1:0] = 01 (ERROR):传输失败。

HRESP[1:0] = 10 (RETRY) and HRESP[1:0] = 11 (SPLIT):当数据传输无法立刻完成时,主机会继续尝试完成数据的传输。

AHB支持两种批量式数据传输方式:持续递增(Incrementing without Wrapping at Address Boundary);另一种为回绕传输(Wrapping at Address Boundary)。具体会在后面详细地解释。

AHB传输操作要点

a. 在AHB传输开始之前,主机必须得到仲裁器的总线访问授权:主机向仲裁器发出总线请求信号,然后仲裁器指示这个主机什么时候可以得到授权;

b. 主机到总线访问授权后,驱动地址与控制信号,来开始AHB总线传输。这些信号将提供传输地址,传输方向,传输带宽,是否这次传输是Burst传输等信息;

c. 在AHB上,一次传输包括给出地址、控制信号周期与数据周期。地址与控制信号周期最少需要一个周期,但是会因为数据的原因多出几个周期。数据周期可以通过从机拉低HREADY信号来延迟;

d. AHB支持批量式数据传输,可以自动递增地址。递增地址方式分为:持续递增与回绕传输;

e. 当HREADY被从机拉低时,会进入等待状态,此时地址与数据都必须延伸(在等待周期内保持不变);

f. 从机输出的HRESP[1:0]信号表示传输的状态为:OKAY,ERROR,RETRY,或SPLIT;

g. 主机的传输状态可由HTRANS[1:0]来表示,有IDLE,BUSY,NONSEQ,SEQ四种类型;

h. HWRITE表示传输方向,高电平表示主机发起的是写操作,数据会由主机放到HWDATA[31:0]信号上;

i. HWRITE为低时,主机发起的是读操作,被寻址到的从机会将数据放到HRDATA[31:0]信号上;

j. HSIZE[2:0]表示每次传输的字节数目;

k. 在AHB上可使用大端摆放法或小端摆放法,由系统设计者决定;

l. 仲裁器以HMASTER表示当前是哪一个主机在使用总线,此信号也可用来控制地址多任务器;

m. 支持分割传输的从机可以通过HSPLIT[15:0]信号,让仲裁器知道要让哪一个主机完成其未完成的分割传输;

n. 从机可以用SPLIT的方式来解决延迟太长的问题,但仲裁器必须时刻观察该从机的响应信号HSPLIT[15:0],并且临时屏蔽已被分割传输的主机,使其等候HSPLIT信号的通知后才可以被分配总线控制权。

基本传输方式(Basic Transfer)

下图是一个最简单的AHB传输的例子,包括了一次AHB传输最基本的两个周期——地址、控制信号周期和数据周期。并且没有被插入任何的等待周期。

然而,在主机发起操作是,从机未必处于就绪状态,此时从机会通过拉低HREADY信号来通知主机插入等待周期,如下图所示:

需要注意的是,在等待周期(Extended Cycles)中,如果是写操作,主机必须保持数据信号保持不变;如果是读操作,则从机不需要将有效数据输出到数据信号上。具体如上图所示。

一个连续传输的例子如下,其中A、C操作没有插入等待周期,而B操作插入了一个等待周期:

控制信号详解

AHB定义了四种传输类型,通过HTRANS[1:0]表示:

一个简单地例子如下:

批量传输是以群组为单位的传输方式,主要根据地址的给法来区分:

递增传输(Incrementing Burst),会根据上一次的地址来递增。

回绕传输(Wrapping Burst),如:WRAP4,HSIZE为4个字节,则每 4 个字节要对齐在 16 字节的范围内。如果第一个地址 = 0x64,则传输的顺序为 0x68、 0x6C、 0x60。

每次传输数据的大小由 HBURST[2:0]定义:

注:递增传输(Incrementing Burst)可以是任意的长度,但是不可跨越1KB的边界(Boundary)。

一个4-beat的Wrapping Burst的例子如下,请注意地址HADDR的变化。

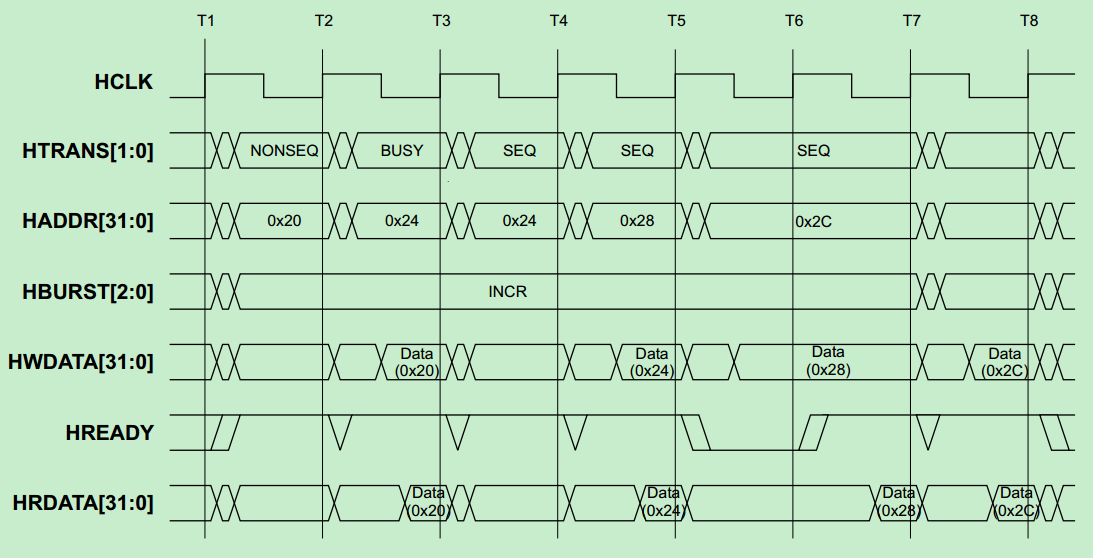

一个4-beat的Incrementing Burst的例子如下,请注意地址HADDR的变化。

一个不指定长度的Burst的例子如下:

此外,控制信号还包括HWRITE(表示或者写)、HPORT(保护控制)。需要注意的是,并非所有的主机都会输出HPROT[3:0]信号,所以除非从机有需要否则不会使用到HPROT[3:0]信号。

从机地址译码

在AHB中,中央译码器会依据地址的高位产生不同的选择信号HSELx,如下图所示,而从机只有在HREADY拉高时,才会将地址、控制信号与选择信号接收下,因为 HREADY 拉高时,表示当前的数据传输已完成。

AHB 有几点特别的规定:

每个从机至少都有 1KB 的内存空间;

主机每次读写的地址空间不可超过 1KB(因为不得跨越1KB的边界);

如果在 NONSEQ 或 SEQ 状态下读写到不存在的地址时,应当有一个预设的从机发出 ERROR 的响应信号;

如果在 IDLE 或 BUSY 状态下存取到不存在的地址时,应当有 OKAY 的响应信号;

预设的从机是中央译码器的一部分;

根据系统设计,使用地址的高位来产生选择信号;

地址的低位送给从机以寻址其的内部存储器或缓存器。

从机应答

一旦主机开始传输,AHB不允许由主机发起取消传输。从机可以使用HREADY与HREPS[1:0]来响应传输的状态,从机可以用下列几种可能表示数据传输的结果:

※ 零等待状态, 立即完成传输

※ 插入一个或多个等待状态, 使有充足时间完成传输

※ 因 ERROR 而结束传输

※ 分段传输,可暂时将总线放出,让其它的 M 先完成数据传输,再接着传输。

HREADY:从机应答主是否读写操作传输完成,从拉低此信号用来延续传输。1表示传输完成; 0表示从机忙,当前时刻无法完成传输。

注:每个从机必须预先设定它回到总线而插入的最大等待周期,用来计算访问总线的延时。推荐但不必须的是, 等待状态最多只可使用 16 个周期,已防止任何访问长时间霸占总线。

从机传输应答信号HRESP[1:0]的详细定义如下:

注:AHB 从设备的错误等异常情况可以有专门的错误处理模块,这样 AHB 从设备可只响应 OKAY 状态。

当主机接收到ERROR信号时,它可以选择结束当前的批量数据传输;也可以选择继续传输剩下的批量数据,但通常不这样做。在从机送出ERROR的信号之前必须先送出OKEY + HREADY(LOW)的信号,而 ERROR 信号至少需要维持两个周期。如下图所示:

在第二个周期从机送出 OKAY+ low HREADY 信号,让从机有充分的时间决定是否需要发出ERROR信号。

在主机收到 ERROR 信号后,立刻结束当前的数据传输。

注意: 从机须维持ERROR信号至少两个周期

对于主机而言,SPLIT与RETRY可视为相同。SPLIT与RETRY其不同之处在于对仲裁器与从机。

对于仲裁器与从机而言,RETRY 与 SPLIT 的不同:

RETRY:※ 仲裁器使用默认的优先级;※ 从机只要求主机重新发起总线控制权申请和传输操作。

SPLIT:※ 仲裁器会调整做分段传输主机的优先权,所以即使该主机的优先级比较低,还是可以及时地得到总线控制权来完成数据的传输;※ 从机的数据就绪后,必须告知仲裁器,让相关主机重新发起传输操作; ※ 分段传输必须要有从机和仲裁器的支持;※ 分段传输的暂停时间中,总线的控制权可以交由其他的主机。

从机应答的时序:

从机可以只给一个周期的 OKAY 信号,如有需求可维持多个周期。

ERROR、 SPLIT 与 RETRY 至少都要维持两个周期。从机必须在最后一个周期送出HRESP[1:0]信号,并且要维持到此次传输结束, HREADY 在传输的最后一个周期要拉高。

如果有需要,从机以在响应的开始即插入多个 OKAY+HREADY (LOW)信号。

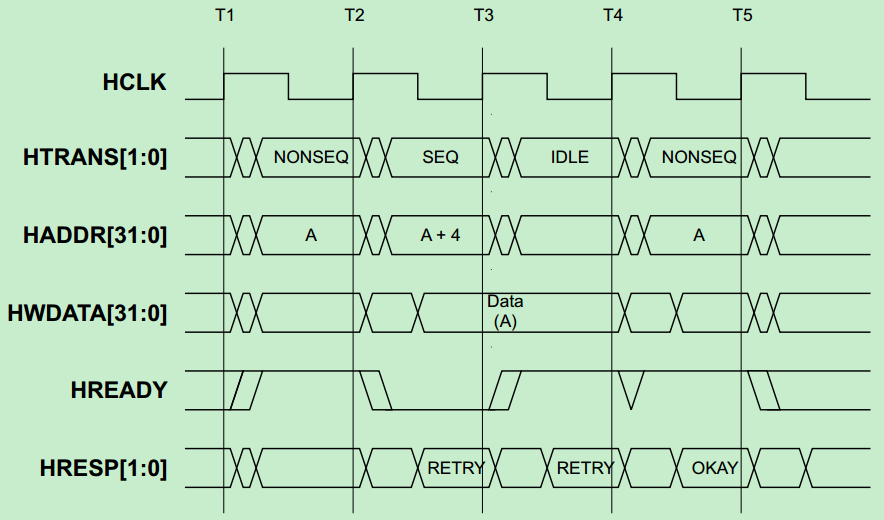

一个Retry的例子如下图所示:

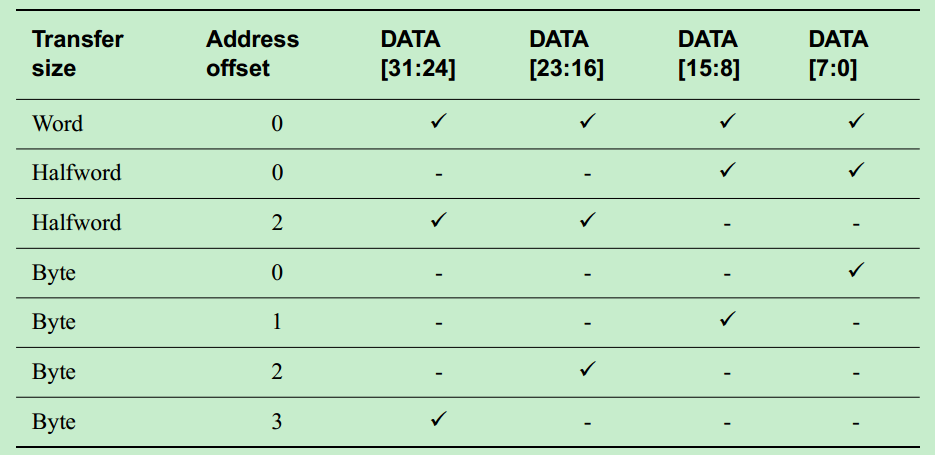

数据信号HRDATA/HWDATA与Endianness

AHB不支持动态的Endianness,在一个AHB总线系统中,需要保证Endianness的一致性。以32bits的AHB总线为例,当采用小端(Little-Endianness)时,

当采用大端(Big-Endianness)时,有:

总线仲裁机制

为了确保任何时刻有且仅有唯一的主机(Master)在控制总线,仲裁器通过观察不同主机的总线请求信号,并根据特定的仲裁算法来确定当前状态下,优先级最高的主机获得总线控制权。此外,仲裁器还需要接收来自从机的相关信号,来完成剩余的SPLIT传输操作。

与仲裁器相关的信号包括:

※ HBUSREQx:由主机到仲裁器,主机通过此信号向仲裁器发起申请总线控制权的请求。

1、主机可在任何时间向仲裁器发起请求;

2、对于固定长度的传输,只要要求一次就可,仲裁器会依据 HBURST[2:0] 来判断传输的长度;

3、对于未定的换输出长度,主机必须持续提出请求,直到完成全部的传输为止;

4、当所有主机都不需要使用总线时,必须在HTRANS上送出 IDLE 信号,仲裁器就会将总线的使用权交给预设的默认主机(Default Master)。

※ HLOCKx:此信号与 HBUSREQx 配合,表示一个不可分段的传输啊操作, HLOCKx 必须在地址周期之前至少一个周期有效。

※ HGRANTx:由仲裁器输出到主机,仲裁器通知某个主机表示此主机得到总线的使用权。

※ HMASTER[3:0]:仲裁器以此信号表示当前是哪一个主机在使用总线,此信号也可用来控制地址多任务器。

※ HMASTLOCK:仲裁器以此信号表示当前的总线是否是被Lock住的,即当前传输的多个序列(多次传输)不允许被其他主机发起的传输操作打断。

※ HSPLIT[15:0]:一个可执行分段传输的从机以此信号让仲裁器知道要让哪一个主机完成其未完成的分段传输。

下面是几个例子:

关于提前结束Burst:

通常仲裁器不会移交总线控制权给新的主机,除非批量传输完成;

但仲裁器为避免存取时间过长, 可提早结束传输。

主机果被提早结束传输,如果一定要完成剩余的传输,就必须重新申请总线控制权,主机必须让仲裁器知道还有未完成的数据传输,并要确保 HBURST 与 HTRANS 信号的匹配。

如 8 笔数据传了 3 笔,被中断后,HBURST 与 HTRANS 来表示后续进行 5 笔的未定长批量传输,或 4 笔定长批量传输+单笔传输。

关于锁定传输(Locked Transfer):

仲裁器允许主机执行Locked Transfers 以确定最后一笔传输完成而不会有Retry或 Error的响应信号。

主机可在锁住传输后插入 IDLE 周期。

仲裁必须从观察每一个主的 HLOCKx 信号, 来决定什么时候主希望执行一个锁定顺序传输,仲裁然后负责确保没有其它主机被授予总线控制权,直到这个锁定顺序传输完成。

当一个锁定传输的序列完成后,仲裁器仍然会保正当前的主机的总线控制权,并通过发起一个附加的传输来保证锁定传输的最后一个序列已经成功完成,或者收到 SPLIT or RETRY 的应答之一。

所以对于锁定传输,推荐的做法是:当前主机可以在锁定序列后插入一个 IDLE 传输,这样其他主机便有机会通过仲裁器获得总线的控制权。

关于总线预设主机(Default Master):

每个系统都有且只能有一个预设主机;

没有主机申请总线使用权时,仲裁器会将总线使用权交给预设主机;

预设主机只可以执行 IDLE 类型的传输;

如果所有其他主机都在等待 SPLIT 传输的完成,系统也应将总线控制权交给预设的主机。

分段传输(Split Transfer)

从机可以用 SPLIT 来解决延迟太长的总线操作。仲裁器必须观察响应信号并且暂时屏蔽(mask)正在处于分段传输状态的主机,直到仲裁器收到来自相应从机的 HSPLIT 信号的通知后才 grant 其总线使用权。仲裁器必须在 HMASTER[3:0] 上产生一个 tag 表示哪一个主机正在执行数据传输。当从机要执行分段传输的动作时,这个从机必须存下此信号。当从机就绪后,可以继续完成被分段的传输时会在 HSPLITx[15:0]信号上,送出要完成传输的主机代号。仲裁器以 HSPLITx[15:0] 来决定哪一个主机可以重新获得总线的控制权。

分段传输顺序:

1. 某一个主机送出地址与控制信号,开始传输;

2. 被寻址到的从机立即提供数据,或者送出分段传输应答信号。在每次的传输,仲裁器会广播出当前是哪一个主机在使用总线。从机需要记录主机号,以便后面重传使用;

3. 当仲裁器收到来自从机的 SPLIT 信号时,仲裁器会将总线使用权交给别的主机使用,如果所有其它主机都处于分段传输等待的状态时,则将总线控制权移交给预设主机。

4. 当从机要继续完成分段传输时,从机应在 HSPLITx 上设定对应的主机ID,来告知仲裁器之前与之传输的是哪个主机。

5. 仲裁器应在每个周期观察 HSPLITx 信号,并及时更新主机的优先级(仲裁算法)。

6. 仲裁器将会允许重新要求使用权的主机,但如果有更高优先级的主机在用总线,可能会延迟。

7.从机会响应 OKAY 信号表示传输完成。

关于多重分段传输(multiple split transfers):

只要一个主机有额外的 HBUSREQ 与 HGRANT 线, 即可发出超过一个以上的传输请求。

仲裁器将一组信号 (REQ and GNT) 视为一个主机。

支持分段传输的从机可被设计去处理额外的传输请求而不需纪录额外的地址与控制信号,但要记录主机ID。

从机可利用 HSPLITx 来表示当前正在处理的是哪一个主机要完成分段传输。

仲裁器可重新仲裁这些主机的请求,高优先级的主机可被重新给予总线控制权。

关于防死锁/ 锁住避免(deadlock prevention):

Deadlock可能发生在很多不同主机对同一个从机发出 SPLIT 和 RETRY 的从机身上, 而该从机又无法处理那么多的SPLIT和RETRY 时,便会发生 deadlock。

Deadlock 可以通过限制分段传输的数目(最多 16 个)来避免。

从机不会记录下每个要求的地址与控制信息,如果要作 SPLIT 的话,只会记录下当前传输对象的 ID 信息。当从机可完成分段传输时,才会锁定要求的地址与控制信息。

从机会依序地让仲裁器知道从机要服务哪些请求。

从机可以任何顺序处理要求的服务。

关于重传:

当从机无法在很短的时间内完成传输的动作时, 它可以要求主机重传。从机一次只可对一个主机发出 RETRY

信号,确定所服务的主机是同一个时, RETRY 的动作才能完成。如果 RETRY 是不同主机时可以采取下列措

施:

给一个 error 回应

通知仲裁器

产生中断

重置系统

关于分段传输之总线转换:

当主机收到 SPLIT 或 RETRY 响应信号时,必须先进入 IDLE 状态并且重新要求总线控制权,仲裁器会在 IDLE 周期结束前将总线控制权分配给新的主机,如下图所示。主机在收到 SPLIT 或 RETRY 信号后须立刻进入 IDLE 状态。

在 T2 与 T3, 从机传两个周期的 SPILT 信号。

该主机在 T3 正沿时发现有 SPLIT 响应信号,于是进入 IDLE 状态。

仲裁器在 T3 正沿时,决定将总线控制权分配给哪一个主机。

在 T4,新的主机送出地址与控制信号。

Split 应答是由于从机当前不能全部准备好主机所请求的全部数据,从而给出该应答信号,从而使得仲裁器屏蔽掉该主机的总线请求,使其不能获取总线,以给从机留出准备数据的时间。

当从机准备好数据之后,它将通过 HSPLITx 信号通知仲裁器取消前面对该主机的请求屏蔽,使其能够重新请求总线,完成传输过程。 SPLIT 操作需要从机和仲裁器都提供硬件上的支持,实现起来有一定的复杂度。

复位

关于AHB 重置(复位)的规定:

HRESETn 为异步信号,被拉低后在 HCLK 正沿后拉为 HIGH(异步复位,同步释放)。

在复位器件,所有的主机都必须为 IDLE 状态。

AHB各组件示意图