Lattice Radiant 加密RTL设计文件简明教程

1赞Lattice Radiant软件是Lattice近年来新推出的FPGA开发平台,主要针对的是2019以后发布的新器件。之前我转载过一篇关于如何使用Diamond中的Synplify Pro产生NGO文件(黑匣子)来加密用户RTL设计文件的,具体请参考:

http://blog.chinaaet.com/justlxy/p/5100051878

Lattice Radiant将不再支持Diamond之前使用的加密策略,以及相关的NGO文件,转而支持的是文本加密功能。本文将介绍如何使用Radiant来对RTL设计文件,进行加密:

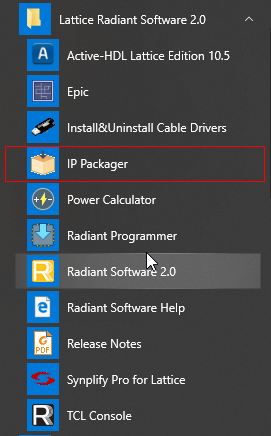

Lattice官方推荐使用IP Packager工具对需要加密的RTL设计,进行IP封装。使用该工具产生的结果可以和Radiant中可以下载的官方IP完全一致。缺点是过程繁琐,还需要些XML脚本文件。具体可以参考IP Packager的Help文件,这里不再详细地介绍。

本文要介绍的是另一种简易的加密方式,通过TCL Console使用加密命令,对RTL设计文件进行加密,并产生加密的RTL文件。这里举一个简单的例子:示例Project中有三个RTL设计文件:

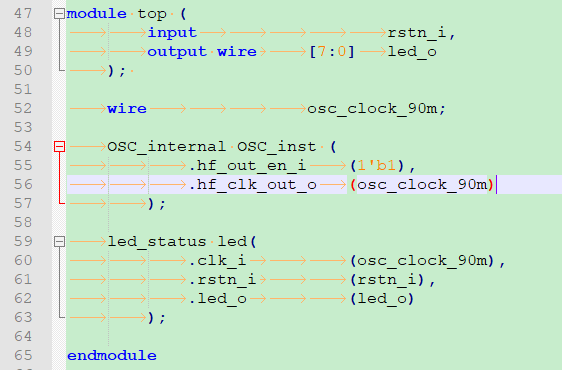

1、top.v:Verilog 顶层文件

2、OSC_internal.v:Radiant IP Catalog中自带的Module

3、led_status.v:需要加密的用户设计RTL文件

top文件全部内容如下:

具体的加密过程如下:

1、首先将需要加密的RTL设计模块合并到同一个文件中,以Verilog设计为例,即将需要加密的Module的所有子模块全部拷贝到同一个.v文件中。注意顶层module在文件的最前面,其他module在后面。【我这个示例比较简单,只有一个文件】;

2、使用如下约束关键字设置需要加密的范围:

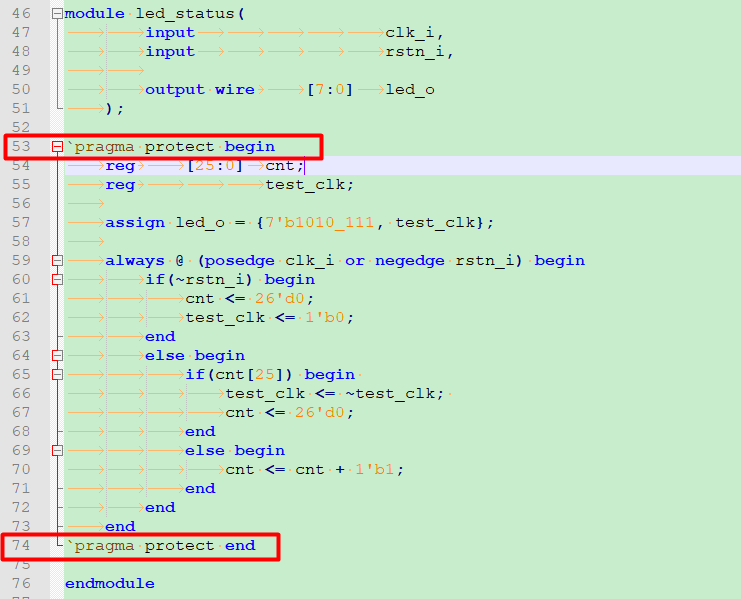

对于Verilog语言,使用`pragma protect begin 和 `pragma protect end

对于VHDL语言,使用`protect begin 和 `protect end

举例如下:

3、在Radiant的安装目录下找到key.txt文件【秘钥文件】,并将该文件拷贝到需要加密的.v文件的文件夹下面,默认地址为:C:\lscc\radiant\1.1\ispfpga\data\key.txt

4、在Radiant的TCL Console 中把当前路径切换到需要加密的.v文件的文件夹,举例如下:

cd D:/12-Lattice_Internal_Work/2021-01-RadiantEncryptedGeneration/Test_Project/src

5、输入如下命令,执行加密程序:

针对Verilog语言: encrypt_hdl -k key.txt -o 输出文件名.v 待加密文件名.v

针对VHDL语言: encrypt_hdl -k key.txt -l vhdl -o 输出文件名.v 待加密文件名.v

举例如下:

encrypt_hdl -k key.txt -o led_status_en.v led_status.v

然后,控制台会输出如下信息:

Options:

Key repository file: key.txt

Directive language: <not specified>, use verilog as default

Output file: led_status_en.v

Processed 1 envelopes.

6、加密完成,可以在当前路径下找到加密后的文件:led_status_en.v。该文件前半部分内容如下:

7、用加密后的文件替换原本文件,重新综合,MAP,PAR并产生bitstream,并进行验证。功能正常。