关于quartus ii开发平台如何调用modelsim

0赞关于quartus ii开发平台如何调用modelsim

----hello·tao

对于这个问题,一直折磨我两天,在网上查,跟问群里兄弟,大部分都是问问题的多,回答的少,所以只能靠自己,在我几天不断的努力下终于搞定了,以前安装的时候一次就安装好,这次多了一些问题,我在此整理出来出来,希望各位FPGA朋友以后碰到类似问题,可以少走弯路。

我用的软件是quartus ii 9.1 和modelsim 6.2se 版本![提别提示一下]你的工程存放文件夹不许带汉字,要不无法调用!!!

1、首先务必记住你的modelsim安装路径

2.然后打开quartus ii 软件新建一个工程和保存文件,然后在菜单项里面tools-option里面EDA tool options 在modelsim下设置路径;

$)@(%5dXDTV%7bKH.jpg)

$)@(%5dXDTV%7bKH.jpg)

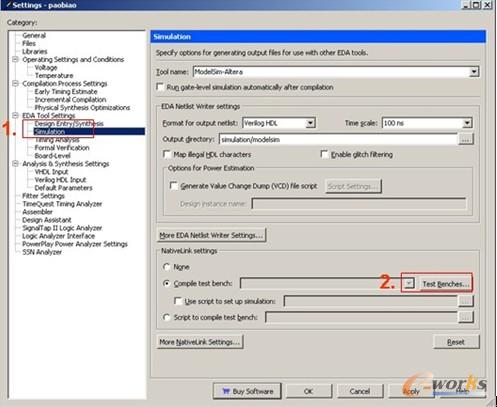

3.在Quartus II 11.0界面菜单栏中选择Assignments->Settings。

1.选中该界面下EDA Tool settings中的Simulation一项;

2.Tool name中选择ModelSim-Altera;

3.Format for output netlist中选择开发语言的类型Verilog或者VHDL等,

4.Time scale 指定时间单位级别

5.Output directory指定测试文件模板的输出路径(该路径是工程文件的相对路径)。

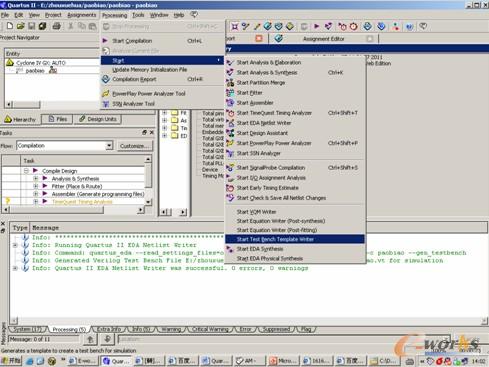

选择Quartus II 11.0开发界面菜单栏下Processing->Start->Start Test Bench Template Writer,提示生成成功。

4、打开仿真测试文件(在上述3中指定的Output directory 目录下找到后缀名为".vt"的文件)并根据自己需要进行编辑。

1. 在Quartus II 11.0界面菜单栏中选择Assignments->Settings->EDA Tool settings->Simulation;

2.选择Compile test bench右边的Test benches;

3.然后在出现的界面中选择New,在新出现的界面中Test bench name 输入测试文件名字,在Top level module in test bench 栏中输入测试文件中的顶层模块名;

4.选中Use test bench to perform VHDL timing simulation并在Design instance name in test bench中输入设计测试文件中设计例化名默认为i1;

5.然后在Test bench files栏下的file name 选择测试文件(在第3步中指定的测试文件输出路径下的后缀名为" .vt " 文件的测试文件),然后点击add,一步一步OK。

【注意】Test bench name和Top level module in test bench 以及Design instance name in test bench分别为".vt"文件的文件名、vt文件中顶层实体模块名、Verilog或者VHDL文件中的模块的例化名。

5、仿真文件配置完成后回到Quartus II 11.0 开发界面

在Quartus II 9.1界面菜单栏中选择菜单栏Tools中的Run EDA Simulation Tool->EDA RTL Simulation 进行行为级仿真,接下来就可以看到ModelSim- 6.2se的运行界面,观察仿真波形。

一般到这步就好使了,如果还不能运行就按照下面步奏设置

6、如果这样还不好使,那么就要找到安装的modelsim-6.2se文件里找到modelsim.ini文件首先右键把只读的√取消,然后.ini 文件里面找到VoptFlow,把VoptFlow = 1设置VoptFlow = 0,保存了,然后右键。Ini文件在只读下打上√就好了。

在试着运行一下看看能否出来波形图

7、可能是没有环境变量的问题,回到在桌面,点击我的电脑-右键属性

%7dSGVVML8I(R@SA($$9%60DHT.jpg)

在点击环境变量

8GL%5b1G6)$GD.jpg)

在系统变量添加变量名跟你modelsim安装路径

这样就应该好使了。

8.仿真结果

看不到图片的可以下载附件

看不到图片的可以下载附件