关于Lattice的DDR_GENERIC(DDIO)的相位调整

1赞

发表于 3/30/2016 11:04:31 PM

阅读(7063)

Lattice的ddr_generic可选择center模式和edge-to-edge模式。

但是两种模式在低于200M的时候,均没有动态调整相位的办法,而在某些环境下动态调整相位又是必不可少的。

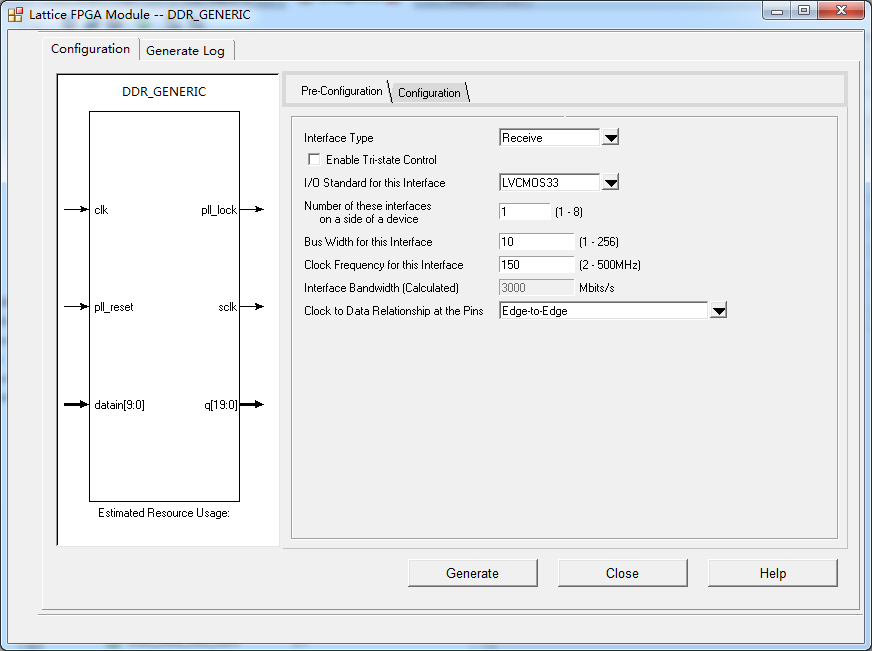

如图:

外部接口为10bit,数据在随路时钟clk上升沿和下降沿均有发送,即dual_edge模式。由于外部走线延迟的不确定性,导致采集到FPGA的数据会出现误码。解决误码最便捷的方式就是调节随路时钟clk与数据data的相位关系,使时钟采集在数据的稳定期间。

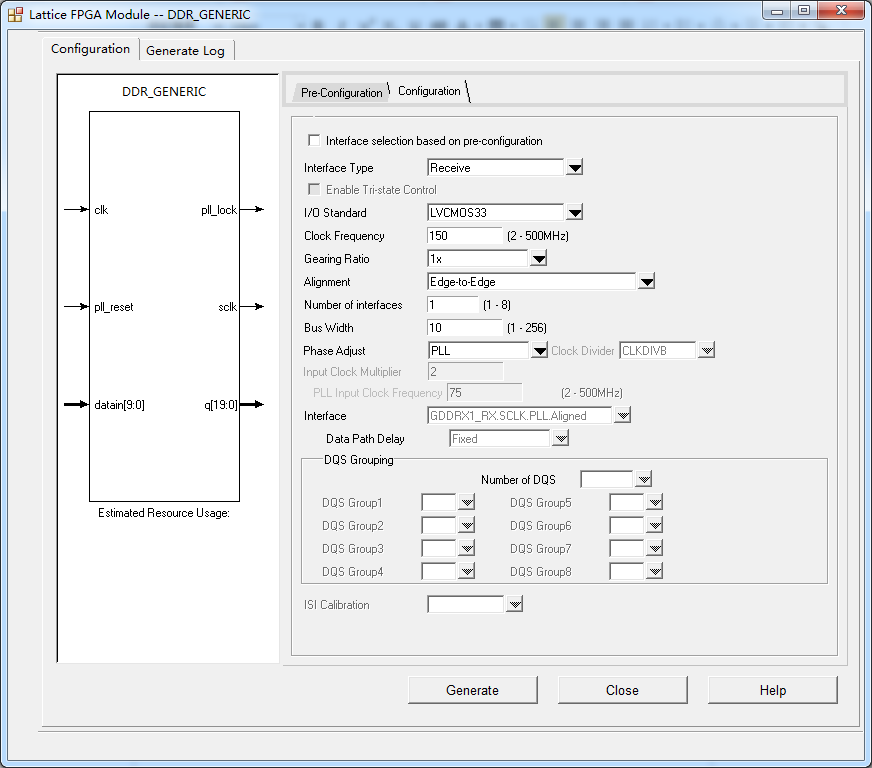

ddr_generic在采用dege-to-edge模式下,内部是带有PLL/DLL的,这里以PLL为例。

生成代码后,对比ddr_generic与PLL(动态模式)生成的代码,我们发现

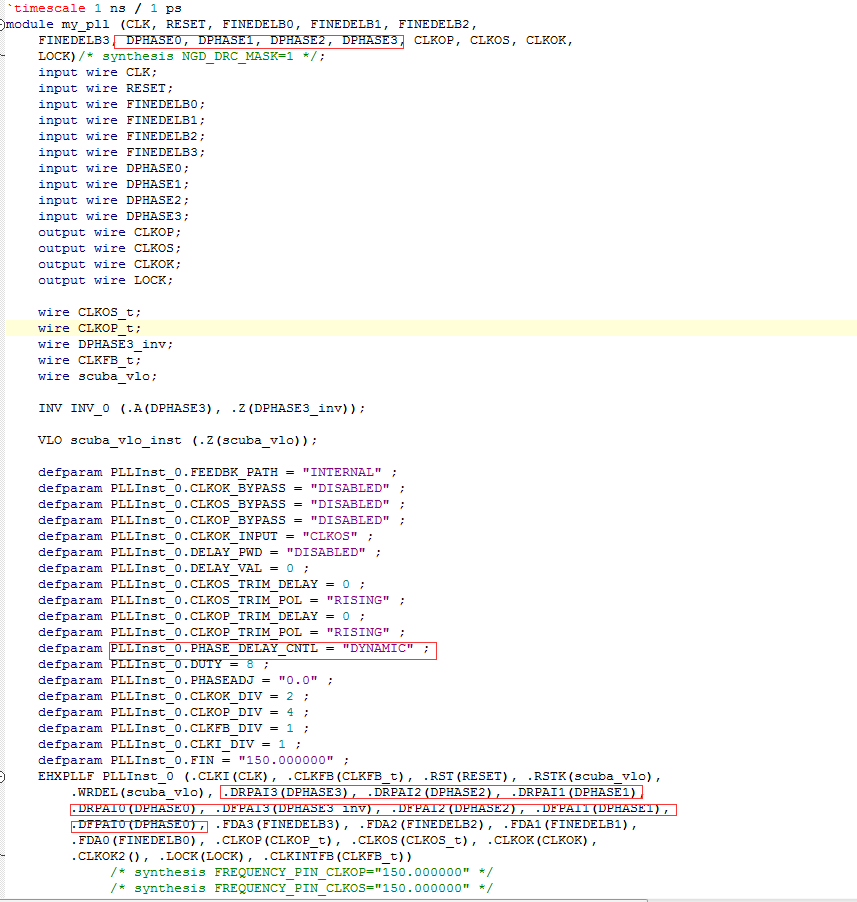

PLL截图:

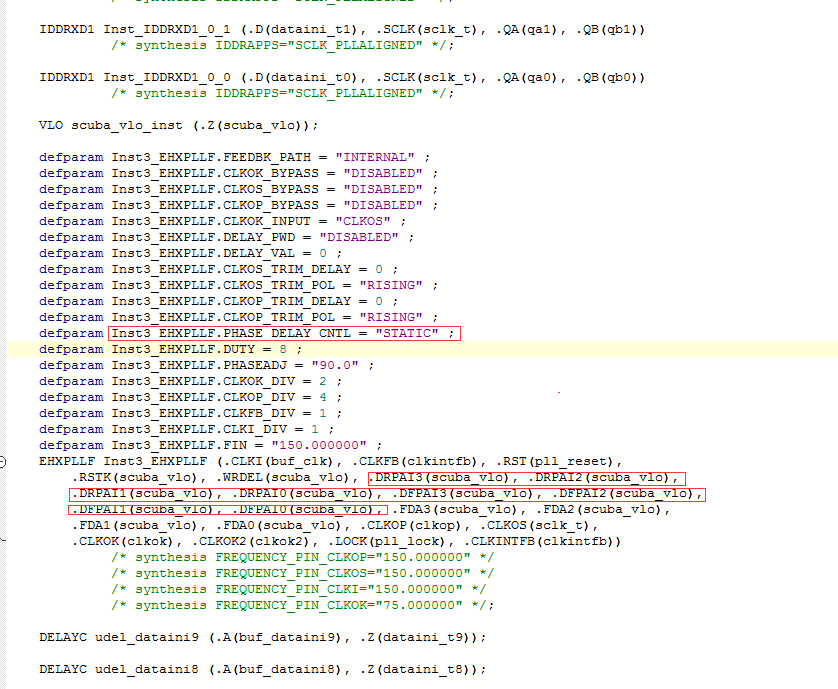

ddr_generic中PLL部分

对比,我们发现在ddr_generic中的PLL原语和PLL单独使用的原语是相同的,都是EHXPLLF,并且配置类似。所以我们只需要将PLL单独使用的时候,负责调整相位的port添加到ddr_generic生成的代码中,并且将这些port与EHXPLLF相连,就可以实现ddr_generic的动态调整。

PLL动态调整可以通过FPGA内部软核mico32控制,或者通过外部mcu或者串口控制,通过对

{DPHASE3, DPHASE2, DPHASE1, DPHASE0}控制,就可以实现输出CLKOS的相位调整。