【原创】Allegro SI 高速信号完整性仿真连载之二(附详细流程)

2赞

Allegro SI 高速信号完整性仿真连载之二(附详细流程)

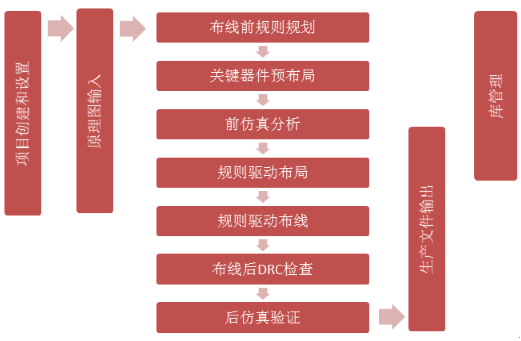

高速PCB设计的流程为:

传统的PCB设计流程如下图所示:

而引入的Allegro PCB SI仿真工具后的设计流程改进为:

原理图输入:

编制元件表、建立连线网表、建立元器件封装库、确定电路逻辑符号与物理器件的映射(指定元器件封装)

前仿真分析:

高速PCB 的前仿真包括以下几个方面:信号完整性(SI)仿真,时序(TIMING)仿真,电磁兼容性(EMI)仿真。

规则驱动布局布线:

模板设计、确定PCB 尺寸、形状、层数及层结构、元件放置、输入网表、设计PCB 布线规则、PCB 交互布局、PCB 走线、PCB 光绘文件生成、钻孔数据文件。

后仿真验证:

信号完整性(SI)后仿真,电源完整性(PI)后仿真,电磁兼容性(EMI)后仿真。

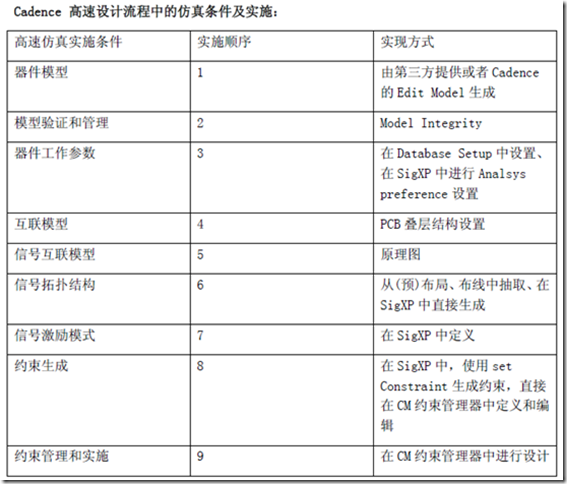

以下将逐个介绍如何在Cadence的高速设计流程中实现这些仿真条件,通过仿真分析,得到高速设计的约束条件和实施设计约束。

一、获取模型

1、http://www.eda.org/ibis/home/models/models.htm

2、到器件厂商的官方网站下载。

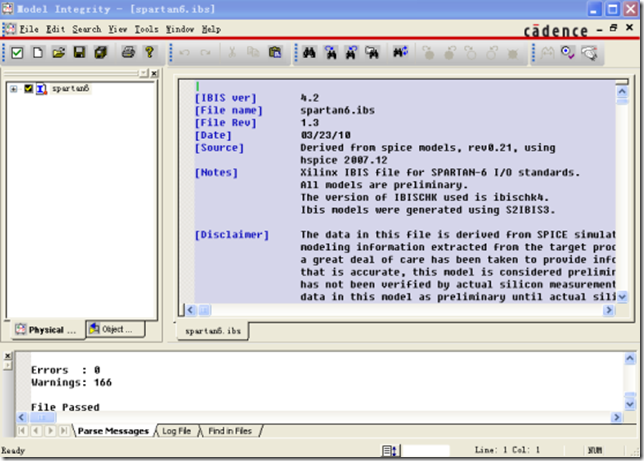

二、模型验证和管理

用Cadence集成工具Model Integrity打开模型,此工具将自动检查验证模型。如果没有错误,将模型转换成DML格式。

注意:DML是Cadence专用的模型语言,在Cadence的高速设计环节中所有的器件模型都以DML格式存储并使用。不管用户使用的是什么文件,在仿真之前都要转换成DML格式的文件才能被Cadence的仿真引擎所识别并使用。

三、仿真库的建立和设置

上一步得到了经过验证的DML模型库,下面将把这个模型库加入到设计中使用。

在PCB SI菜单中,选择Analyze---SI/EMI sim---Model Browser,出现如下模型库管理界面:

选择 Set Search Path,出现以下界面,可以通过选择Add Directory指向我们之前保存的模型库文件夹。

四、仿真分析条件设置

通过菜单Tools=》Setup Advisor命令打开Database Setup Advisor 窗口,打开的窗口如下图所示:

Cross-section:定义在Layout中使用的叠层和材料参数;

DC Nets:定义直流电压值,也即系统静态工作点;

Device:指定器件的类型和Pinuse属性;

SI Module:为器件的指定电气模型;

SI Audit:对前面的设置进行检查以确保能够进行正常地进行抽取和仿真。

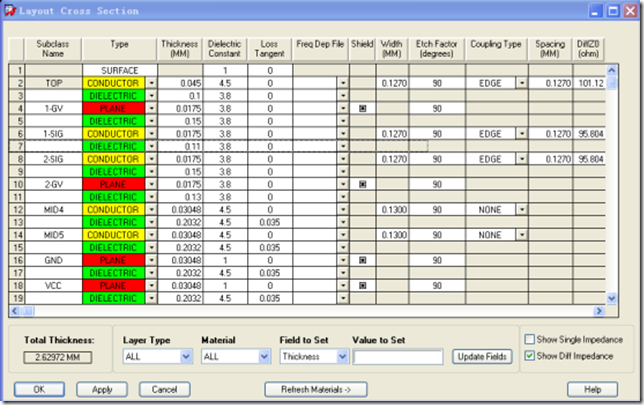

点击Next,选择Edit Cross-section,出现PCB叠层参数设置界面:

在此对话框中,可以添加或者删除叠层,也可以改变每一层的类型、材料、厚度、电导率、介电常数、线宽和特征阻抗等参数。

做完并关闭叠层参数的设计之后,回到Database Setup Advisor界面,点击Next,进入直流电源网络的设置界面,如下:

选择左侧列表框中的待选网络,在右侧的文本框中可以指定该网络直流电压值。设置好直流电压后,回到Database Setup Advisor界面,点击Next,出现以下界面:

点击Device Setup,进入器件类型设置界面:

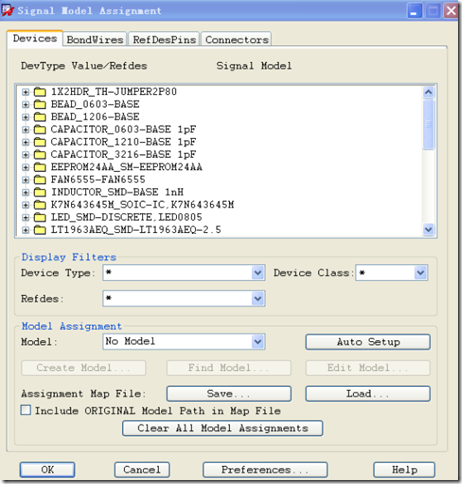

在此界面中,用户可以指定以特定字符开始的器件标号属于某一类器件。对于Default Value,原理图中标明的是多大就标多大。设置好后继续Next,进入模型分配界面:

Devices目录显示了所有网表中导入的元器件,要指定模型,先选中,然后点Find Model,弹出模型分配对话框:

在Model Name Pattern中输入“*”,按“Tab”键,库目录中所有的模型将列出来,选择合适的,点击Assign,模型就被分配好了。

当以上所有的仿真条件及参数设置完成之后,在Database Setup的最后一步我们可以用SI Audit进行一下验证,以确保我们所关心的网络上所有和仿真相关的因素都已经处理好了。如果Audit的结果出错,对照结果的提示,找到出错的原因,重复前面的某些步骤,对仿真条件进行修改和完善,如果没有问题就可以进入下一步的高速信号仿真了。

说明: 由于本人能力有限,博文上有不正确的地方欢迎批评指正,另外也可加QQ群进行讨论:中国硬件设计交流PCB&SI 217166793。