Zedboard 学习笔记之《Vivado Logic Analyzer的使用》

0赞

发表于 12/28/2016 5:38:10 PM

阅读(6415)

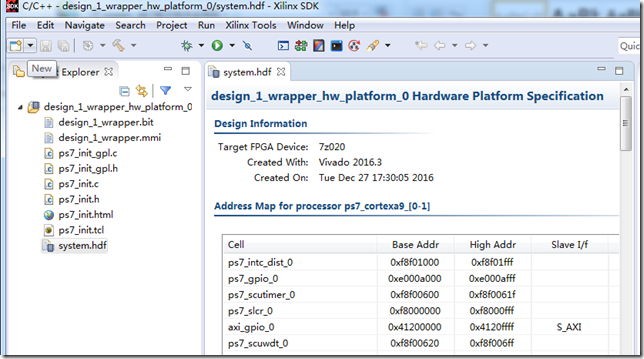

接着上篇,Zedboard 学习笔记之《创建ZYNQ处理器设计和Logic Analyzer的使用》,导出到SDK后,自动启动了SDK,

新建一个应用工程,工程名为Zynq_Design,

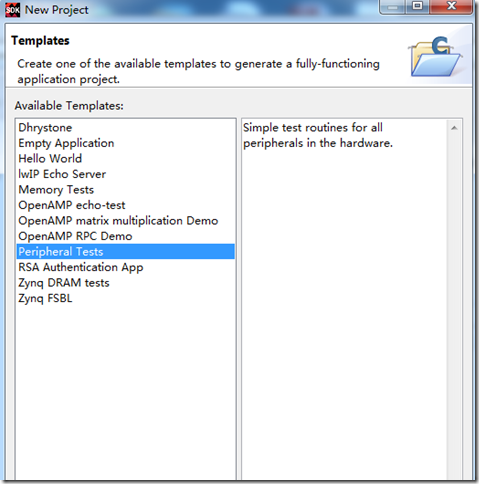

选择工程模板-Peripheral Tests,

这样就创建了一个工程,编译,完成后右键选择Zyn_Design--Debug as—Debug Configurations,双击xilinx C/C++ application(GDB),自动产生子目录Zynq Design Debug,

设置串口,波特率等,

设置完成后,软件自动下载bit文件到FPGA,并执行Debug,我们看到在console窗口有打印输出,

现在转到Vivado,连接硬件,自动打开下图所示界面,

点击Run Trigger Immediate按钮来观察波形,可是我的没有数据采集到,

参考UG940文档来做的,什么原因呢?排查中……

![_]`0E}(]G_{0658O%ETO5QL _]`0E}(]G_{0658O%ETO5QL](http://files.chinaaet.com/images/blog/2019/20161228/636185434805830000123534.png)

![1{R~0]V(OL@3HIM4(D~OE`J 1{R~0]V(OL@3HIM4(D~OE`J](http://files.chinaaet.com/images/blog/2019/20161228/636185434851780000641906.png)