基于FPGA的以太网控制器(MAC)设计

1赞今天给大侠带来基于FPGA的以太网控制器(MAC)设计,由于篇幅较长,分三篇。今天带来第一篇,上篇,以太网基本原理以及以太网控制器(MAC)的基本框架。话不多说,上货。

为了方便参考学习,后两篇这里也放上超链接:

导读

当前,互联网已经极大地改变了我们的生产和生活。与之相适应的,在嵌入式系统的研究开发方面,也越来越重视网络功能。嵌入式系统已经不再局限于一个个孤立的控制、处理单元,而是走向网络集成化,从而实现了多个系统的集中控制、信息共享。

以太网(Ethernet)技术在嵌入式系统上的开发应用,已经成为当前嵌入式研究领域的技术热点之一。一方面,与传统的 RS-485、CAN 等相比较,以太网更加高速、通用,而且还可以直接与 Internet 相连接,提供更大范围的远程访问;此外,经过适当剪裁和优化的 TCP/IP 协议栈,也完全可以适应工业用途的需求。另一方面,相对于新兴的 USB 2.0、IEEE 1394 等总线,以太网技术在传输距离、布线成本以及控制软件的通用性上都有明显的优势。

基于以太网的嵌入式系统,在以下方面都有良好的应用前景:

• 工业:工业控制、网络仪表、远程的分布式数据采集……

• 家庭自动化:智能家庭、信息家电、家庭网关……

• 商业:远程销售平台、智能自动售货机、公共电话卡发行系统……

• 环保:水源和空气污染监测,防洪体系及水土质量监测、堤坝安全……

• 其他:交通管理、车辆导航、自动抄表……

因此在使用 FPGA 设计各种嵌入式应用系统时,需要考虑为系统提供以太网接口。本章将 通过 FPGA 实现一个以太网控制器(MAC)的实例,详细介绍实现过程。

第一篇内容摘要:本篇会介绍以太网基本原理,包括以太网协议的参考模型、MAC 子层、媒体无关接口(Media Independent Interface)等相关内容,还会介绍以太网控制器(MAC)的基本框架等相关内容。

一、以太网基本原理

一般所说的以太网协议是指根据 IEEE 802.3 规范制定的局域网协议(LAN,Local AreaNetwork)中的 CSMA/CD 协议。目前,以太网通信常用的介质是双绞线和光纤。

注意:CSMA/CD 协议是 Carrier sense multiple Access with Collision Detection 的缩写,是带有检测冲突的载波侦听多路存取协议,具体内容请参考 IEEE 802.3 规范。

1.1 以太网协议的参考模型

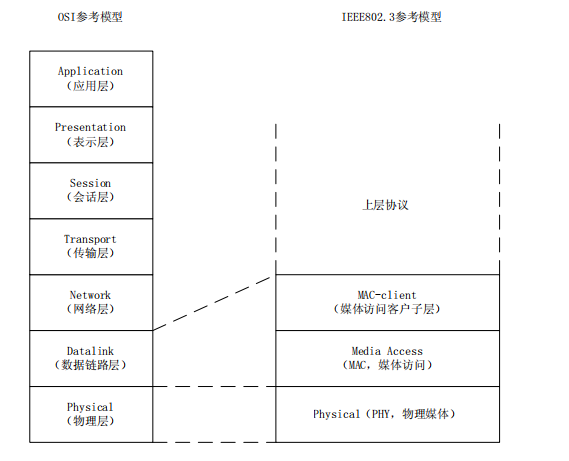

以太网协议的逻辑关系遵循 OSI 参考模型(Open System Interconnect Reference Model,开放式系统互联参考模型),如图 10-1 所示。

物理层是指网络通信连接的媒介物质,用于携带计算机之间的以太网信号。当前应用最多的是双绞线和光纤。使用这两种媒介,以太网目前可以实现 4 种传输速率。

• 10 Mbit/s:10Base-T 以太网。

• 100 Mbit/s:快速以太网。

• 1000 Mbit/s:千兆位以太网 802.3z。

• 10 千兆位以太网:IEEE 802.3ae。

图 1 以太网协议逻辑关系的参考模型

MAC 子层有两个基本职能:数据封装,包括传输之前的帧集合和接收中、接收后的帧解析/差错监控;媒体访问控制,包括帧传输初始化和传输失败恢复。

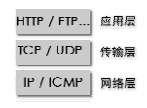

上层协议根据实际应用可以选择多种不同的协议,如 IP 协议、TCP 协议、HTTP 协议等。常用的 TCP/IP 协议如图 10-2 所示。

图 2 上层协议

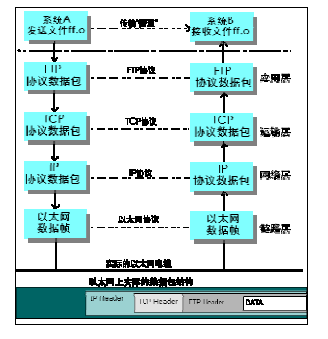

在进行实际的以太网通信中,每一种协议都是运行在其下面层次的协议基础上。例如,当两个计算机系统使用 FTP 协议传输文件时,从用户看来是两个系统基于 FTP 协议的直接交流,实际上文件的数据传输则是经过了层层打包和解包的协议路径,如图3 所示。

图 3 FTP 协议的通信过程

上层的各个协议栈要分别实现对数据的打包、解包、校验以及对下一层相关协议的调用。例如,在 IP 协议栈从以太网驱动收到一个数据包后,经过解包、校验,确认是否为有效的 IP包,如无效则舍弃该包;如有效则进一步判断包内的数据,转而调用 TCP、UDP、ICMP 等协议或使用户自定义的处理服务。而以太网控制芯片的功能是完成 TCP/IP 协议簇分层模型中链路层的相关工作,它处理与双绞线 RJ-45 接口之间的所有物理细节。

本篇将要介绍的以太网控制器将实现有关 MAC(媒体访问)子层的控制功能。在此基础上,开发人员可以简便、快速地开发出基于以太网的嵌入式系统应用。因为以太网的上层协议可以根据需求的不同进行选择,物理层可以根据网络速率不同选择特定的媒介物质。下面将详细介绍有关 MAC 层的内容。

1.2 MAC子层

MAC 子层在上层协议和以太网网络之间传输和接收数据,其主要功能是确保以太网上每一帧数据的传输都遵循了 IEEE 802.3 规范所规定的介质存取规则。

a.基本帧数据格式

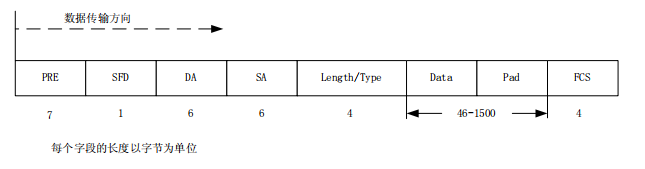

IEEE 802.3 规范为实现 MAC 定义了一套基本的帧数据格式,如图 4 所示。

图 10-4 帧数据格式

各个字段的含义及规定如下。

• Preamble(PRE):报头,字段中 1 和 0 交替使用,接收方通过该字段知道导入帧,并且该字段提供了同步接收物理层帧接收和导入数据流的方法。

• Start-of-frame delimiter(SFD):帧起始分隔符,字段中 1 和 0 交替使用,结尾是两个连续的 1,表示下一位是目的地址的第一个字节的第一位。

• Destination Address(DA):目标地址,用于识别需要接收帧的目的地。

• Source Address(SA):源地址,用于识别发送帧的源地址。

• Length/Type:长度/类型,表示包含在帧数据字段中的 MAC 数据大小,也可以表示帧的类型。

• Data:数据,是一组 n(46≤n≤1500)字节的任意值序列。

• Frame check sequence(FCS):帧数据校验序列,该序列包括 32 位的循环冗余校验(CRC)值,由发送方生成,通过接收方进行计算以校验帧是否被破坏。

b.帧传输

MAC 层从上层协议接收到发送帧数据的请求,首先按照下面的次序将数据和地址信息保存到 MAC 层的帧数据缓冲区中。

• 插入报头和帧起始分隔符。

• 插入目标地址和源地址。

• 统计来自上层协议数据的数量,插入数量值。

• 插入来自上层协议的数据,如果数据量小于 46 字节,则补齐 46 字节。

• 根据目标地址、源地址、长度/类型和数据产生 CRC 校验序列,并插入校验序列。

一帧完整数据组成后,MAC 层可以开始发送帧数据。有两种发送方式可供选择:半双工(half duplex)和全双工(full duplex)。IEEE 802.3 规范规定所有的以太网 MAC 都要支持半双工方式,即一个时刻只能进行发送或者接收,而不能同时进行发送和接收。全双工方式下发送和接收可以同时进行。

c.帧接收

帧接收的过程和发送的过程是相反的。首先检查帧数据中的目标地址和当前地址是否相符,然后检查接收到的帧数据中的数据长度、CRC 校验序列和实际的数据长度、CRC 校验序列是否相符。如果都相符,则将数据交给上层协议进行解析,MAC 层的传输任务完成。

1.3 媒体无关接口(Media Independent Interface)

IEEE 802.3 规范提出媒体无关接口(Media Independent Interface,MII)就是为了能够实现 MAC 层和不同的物理层(PHY)之间的逻辑连接,如图 5 所示。

图 10-5 媒体无关接口

MAC 层可以通过媒体无关接口连接不同的物理层。根据对以太网通信速率的要求选择合适物理层接口。针对不同的物理层,媒体无关接口可以以不同的方式实现到 MAC 的逻辑连接。例如在 10Mbit/s 以太网通信中,媒体无关接口使用 1 位来串行发送/接收数据流;在 100Mbit/s以太网通信中,媒体无关接口使用 4 位来串行发送/接收数据流;在 1000Mbit/s 以太网通信中,媒体无关接口使用 8 位来串行发送/接收数据流。

二、以太网控制器(MAC)的基本框架

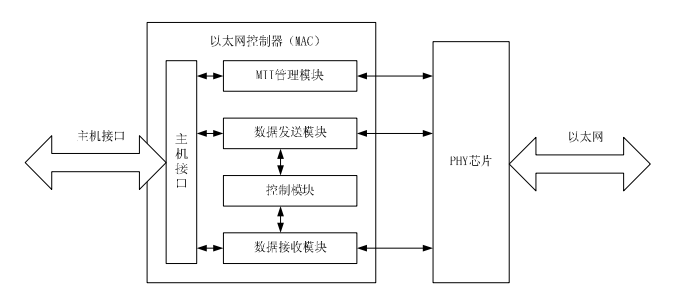

下面将要介绍的以太网控制器(MAC)实现了以太网标准的第二层协议——MAC(媒体访问控制)协议,完全符合 IEEE 802.3 和 IEEE 802.3u 规范所规定的 10Mbit/s 和 100Mbit/s 以太网标准。如图 6 所示,使用这个以太网控制器外部连接一块 PHY 芯片(实现了物理层功能的芯片)就可以进行数据链路层的通信,即帧通信。在此基础上可以方便、快捷地开发出更高层次的协议,实现 FTP、HTTP 等协议。

图 6 以太网控制器

这个以太网控制器具体实现了以下内容。

• 符合 IEEE 802.3x 规定的全双工帧控制。

• 半双工传输模式下的 CSMA/CD 协议。

• 32 位 CRC 校验序列的自动产生和检查。

• 报头的产生和去除。

• 发送和接收数据包的完全状态控制。

• 满足 IEEE 802.3 规定的 MII(媒体无关接口)。

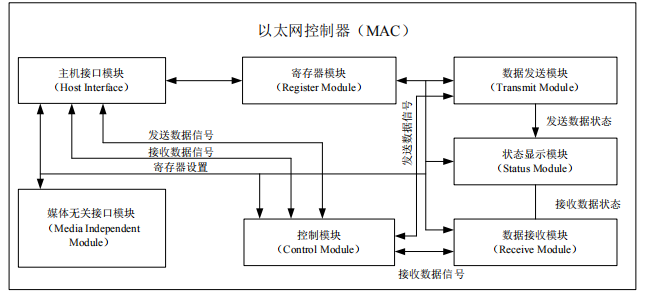

针对以太网控制器需要完成的任务,本节将设计以太网控制器的程序框架,并对各个重要部分进行讲解,如图 7 所示。

图 10-7 以太网控制器程序框架

以太网控制器的程序框架包括如下几个主要部分。

• 主机接口(Host Interface):主机接口用来连接主机部分,将接收到的数据帧保存到存储器中,同时从存储器中载入需要通过以太网接口传输的数据。主机上可以实现更高层次的以太网协议。

• 数据发送模块(Transmit Module):完成所有与发送数据相关的操作,包括产生报头、添加 CRC 校验序列等。

• 数据接收模块(Receive Module):完成所有与接收数据相关的操作,包括去除报头、CRC 校验。

• 控制模块(Control Module):完成以太网控制器所有功能需要执行的操作。

• 媒体无关接口模块(Media Independent Interface):提供一个与媒体无关的接口,用来连接外部的以太网 PHY 控制芯片。

• 状态显示模块(Status Module):记录以太网控制芯片进行数据传输时各个状态的变化。

• 寄存器模块(Register Module):为以太网控制芯片提供需要的所有寄存器。

本篇到此结束,下一篇带来基于FPGA的以太网控制器(MAC)设计(中),会介绍以太网控制器(MAC)程序的实现,包括顶层程序、媒体无关接口模块(Media Independent Interface Module)、数据发送模块、数据接收模块、控制模块等相关内容。

为了方便参考学习,后两篇这里也放上超链接: