基于FPGA的按键消抖你真的设计正确了吗?

2赞

发表于 8/26/2016 4:54:47 PM

阅读(9931)

其实这个代码本来不想发的,因为一说按键消抖,FPGA入门的第一个设计就是它。然而...............

翻开百度结果却很难找到正确的程序。通常设计思想是酱紫的

1,采集key_in 进入key_reg 寄存器1

2,延时DELAY_TIME后,再采集的数据进入寄存器2

3,如果寄存器1和寄存器2数据相等 —— 同为1或者0 。

4,证明稳定,输出。

网络上某金以及某权的代码都是写了很长,很长。用了很多的reg,最终还是这么设计的 。

他们的代码太长,手机看着累,就省略了吧。

而实际的设计思路是这样子的:

1,采集key_in 进入key_reg 寄存器

2,如果key_in 在输入保持0/1不变,保持了DELAY_TIME时间

3,证明数据稳定,输出。

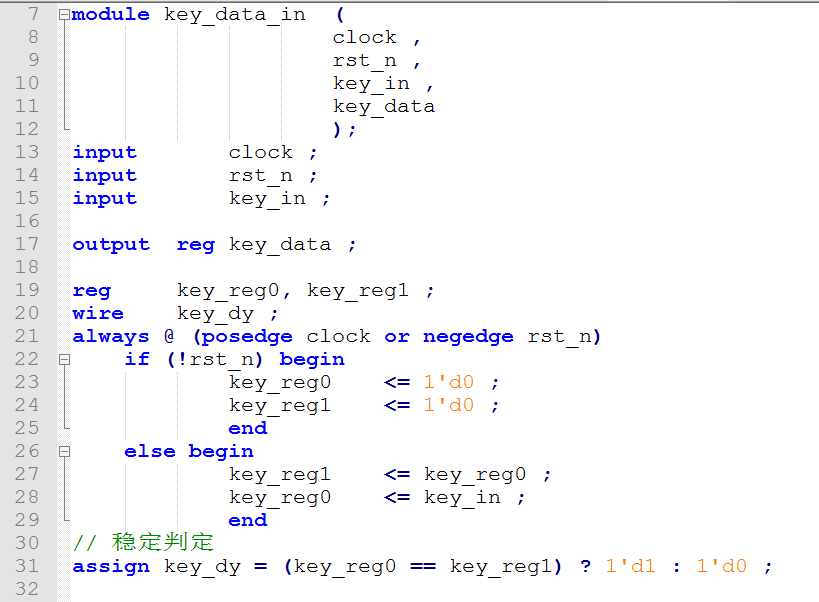

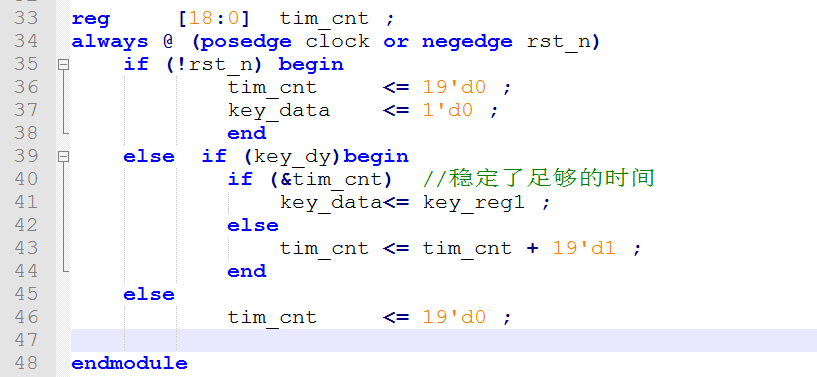

基于这种思路,所以我的代码是这样子的:

如果大家有好的设计方案,欢迎提出哦。

(AET居然不支持verilog代码上传,没办法,为了不改变格式,就只有上图片了)

本宝宝最怕的是有人会说,你这个设计没看出有啥区别啊

1,本宝宝的设计才是正确的。几个大网咖的大家熟知的程序居然是错误的。

2,比起其他正确代码,用的逻辑少了至少1/3.

FPGA从业者学习交流 ——

微信公众号:FPGA攻城狮之间

FPGA广东交流群:162664354

FPGA开发者联盟: 485678884