【原创】从零开始学FPGA系列练习一--------------------计数器设计

0赞啦啦啦,我又开始写博客了,希望这次能一直坚持下去,养成总结的好习惯

1. 脉冲

功能描述:

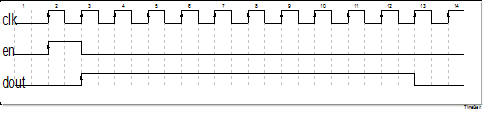

当收到en=1时,dout产生一个宽度为10的高电平脉冲。

信号列表:

信号名 | I\O | 位宽 |

clk | I | 1 |

en | I | 1 |

dout | O | 1 |

波形图:

从零开始学FPGA,计数器练习。

一、 计数器编写规范

1. 计数器规则1:计数器逐一考虑三要素,初值、加1条件和结束值;

2. 计数器规则2:以下是计数器一般形式。

assign 加1条件 = xxxx;

assign 结束条件 = (加1条件)&&(结束值)

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

cnt <= 初值;

end

else if(加1条件) begin

if(结束条件)

cnt <= 初值;

else

cnt <= cnt +1;

end

end

3. 计数器规则3:计数初值必须为0;

4. 计数器规则4:结束条件必须是加1条件;

5. 计数器规则5:结束后必须回到0;

6. 计数器规则6:结束值必须是n-1的形式;

7. 计数器规则7:assign形式必须为:(加1条件)&&(cnt==计数值-1)

8. 计数器规则8:限定范围必须用“>=”和“<”两种符号;

9. 计数器规则9:cnt==x-1,不表示数到x;只有当“(cnt==x-1)”并且“加1条件”有效时,才表示数到x。

10. 计数器规则10:设计步骤,先写计数器的always段,条件用名字代替;然后用assign写出加1条件;最后用assign写出结束条件。

11. 计数器规则11:加1条件必须与计数器严格对齐。其他信号向计数器对齐。

12. 计数器规则12:命名必须符号规范;

13. 计数器规则13:减1计数器暂时不用。

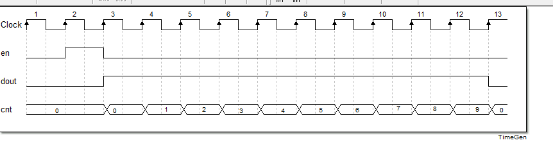

根据练习题目,用TimeGen实现的波形,计数从0~9。

代码实现如下:

module(

clk,

rst_n,

en,

dout

);

input clk;

input rst_n;

input en;

output dout;

wire clk;

wire en;

reg dout;

reg[1:0] cnt;

assign add_cnt =(dout ==1);

assign end_cnt =(cnt == 9)&&add_cnt;

always @(posedge clk or negedge rst_n)begin

if(rst_n == 1'b0)begin

cnt <= 1'b0;

end

else if(add_cnt) begin

if(end_cnt)

cnt <= 0;

else

cnt <= cnt+1;

end

end

always @(posedge clk or negedge rst_n )begin

if(rst_n==1'b0)begin

dout <= 1'b0;

end

else begin

if(en==1'b1)begin

dout <= 1'b1;

end

else begin

if(end_cnt)

dout <= 0;

else

dout <= dout;

end

end

end

endmodule