1、FPGA学习之蜂鸣器

0赞

发表于 4/24/2016 10:15:27 PM

阅读(3109)

将自己学习的一些东西记录下来。

module lianxi2 ( clk, rst_n, fm ); input clk; //板子时钟,50MHz input rst_n; //复位,低电平有效 output reg fm; //fm在赋值左边,需要定义为reg型 reg [20:0]cnt; //21位计数器,最大计数2的21次方 always@(posedge clk or negedge rst_n) if(!rst_n) cnt <= 21'd0; else if(cnt < 21'd1_999_999)//从0开始,共计数2_000_000次,即40ms cnt <= cnt + 1'b1; else cnt <= 21'd0; always@(posedge clk or negedge rst_n) if(!rst_n) fm <= 1'b0; else if(cnt < 21'd1_000_000)//从0开始,共计数1_000_000次,即前一半时间fm高电平,后一半时间fm低电平,即占空比为50%的PWM信号 fm <= 1'b1; else fm <= 1'b0; endmodule

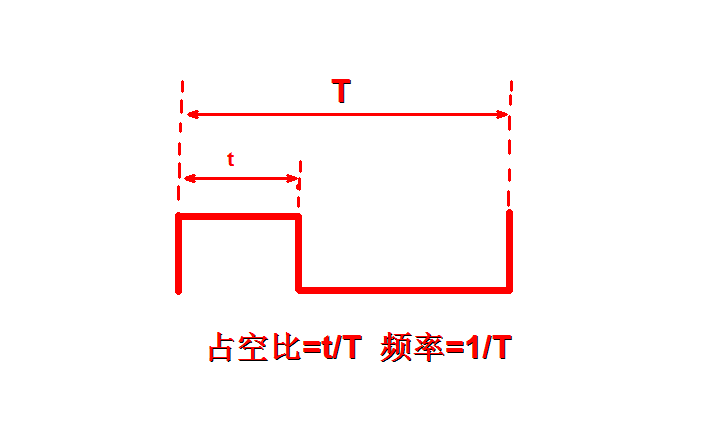

上图为PWM模型

可以修改T(cnt < 21'd1_999_999)或者t(cnt < 21'd1_000_000)来获得不同的模型

下面为测试文件testbench

`timescale 1ns/1ns `define clk_period 20 //定义时钟周期为20ns module lianxi2_tb; reg clk; //将.v文件中的端口复制过来,input修改为reg,output修改为wire reg rst_n; wire fm; lianxi2 lianxi2 //将.v文件中的端口复制过来,加个例化名字,加个.,加个例化的端口 ( .clk(clk), .rst_n(rst_n), .fm(fm) ); initial clk = 1; //初始化时钟clk always #(`clk_period/2) clk = ~clk; initial begin rst_n = 1'b0; #(`clk_period*20) //初始rst_n为低电平,延时400ns后复位 rst_n = 1'b1; #(`clk_period*4000000) //程序继续进行4_000_000*20ns = 80ms $stop; end endmodule

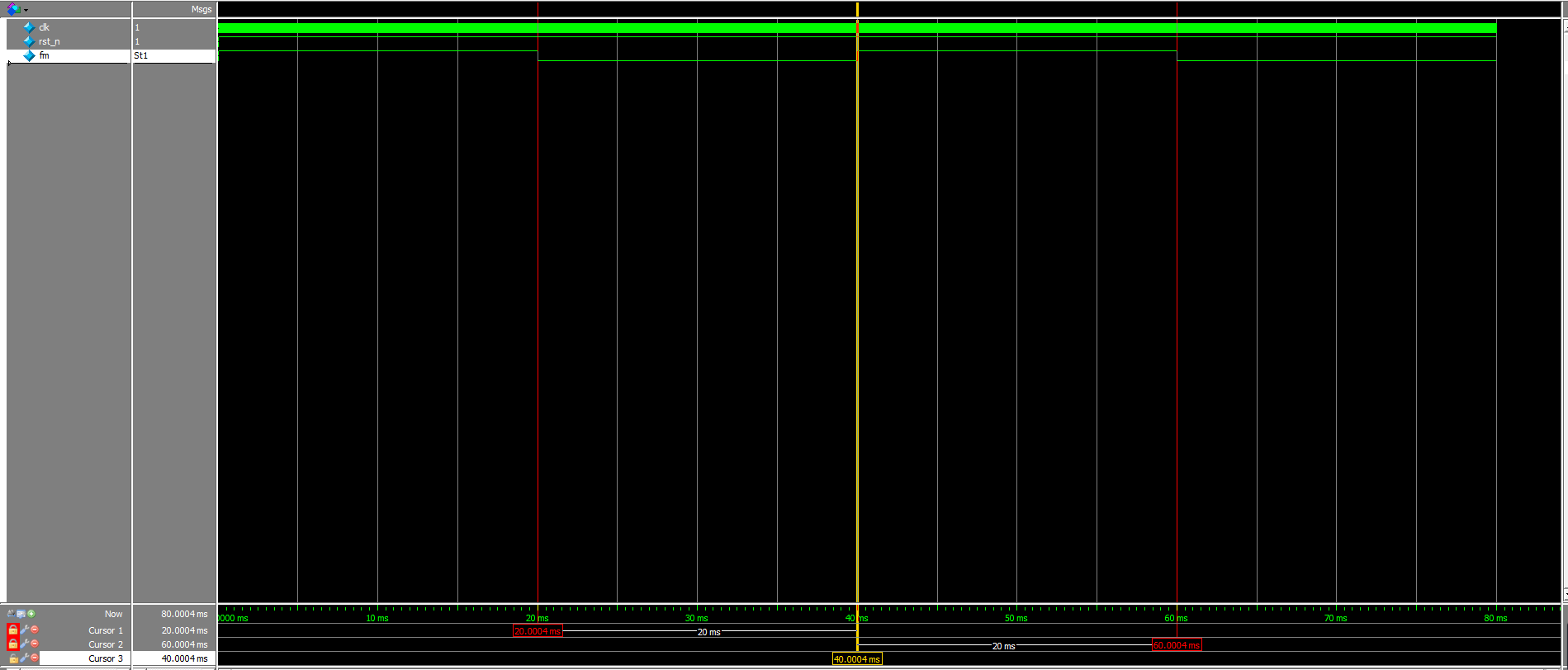

得到的波形如下

可以看到得到的fm波形,周期是40ms,占空比为50%。