FPGA教学——用FPGA来给FPGA EDA加速?

0赞众所周知,目前的FPGA EDA设计软件大都运行在x86的CPU上,而在很多领域,FPGA加速器又可以作为CPU的协处理器进行计算加速。那么,FPGA本身是否可以用来对FPGA EDA,比如综合、布局、布线的过程进行加速呢?

前阵子在Reddit上看到了这个问题,引发了很多思考,后来查了些资料,还真有这么一本书在一定程度上系统解答了这个问题:

这本书研究了加速EDA算法的硬件平台,如ASIC,FPGA和GPU。覆盖范围包括讨论在何种条件下使用一个平台优于另一个平台,例如,当EDA问题具有高度的数据并行性时,GPU通常是首选平台,而当问题具有更多的控制因素时,FPGA可能是首选的。书里还给出了几种EDA算法(故障仿真、故障表生成、SPICE模型卡评估、基于蒙特卡洛的统计静态时序分析、布尔可满足性)的加速结果,与这些算法的单核实现相比,可将运行速度提高800倍以上。

该书作在如何最好地利用并行性来加速EDA算法方面给出了很有价值的参考。书中还提出了一种在一组约束条件下,从常规单处理器代码中自动提取SIMD(单指令多数据流)并行性的方法。使用这种方法,这种单处理器代码可以自动转换为GPU代码,实现显著加速。这种方法特别有用,因为不同的GPU通常有不同的规格,在这种情况下手工生成GPU代码变得不太现实。

该书提供了在加速特定EDA算法时使用ASIC、GPU还是FPGA的指导方针,并用在这些平台上实现的一个具体示例(布尔可满足性)验证了这些建议;通过介绍可供读者使用的示例算法来帮助读者确定如何最好地加速其EDA算法;讨论一种自动生成GPU代码的方法(给出一定约束下的常规单处理器代码的条件下)。

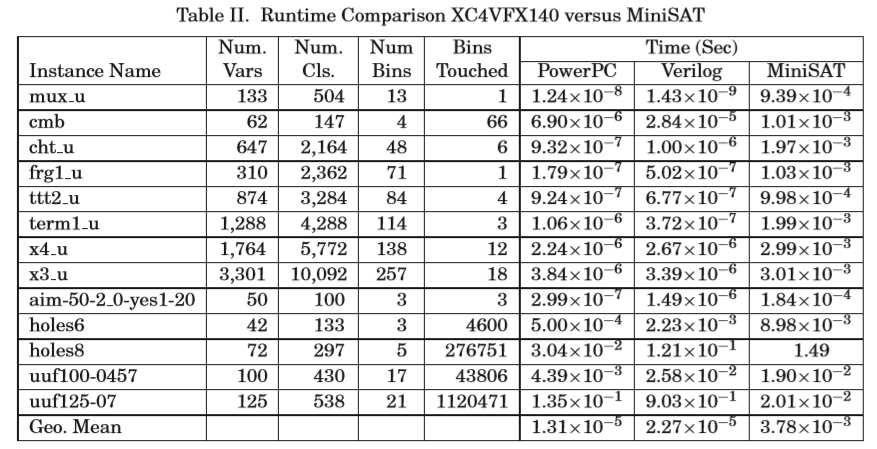

其中在该书的第五章唯一提到了FPGA平台加速,也就是Accelerating Boolean Satisfiability on an FPGA章节,提出了一种基于FPGA的SAT方法,在该方法中,Implication Graph的遍历和Conflict Clause的生成是在硬件中并行执行的,并且Clause Literal存储在FPGA Slice单元里,为了解决复杂的SAT问题,启发式地将clause划分为许多“bin”,每个bin都可以fit进FPGA中,最后得到结论,在使用了Virtex-4 (XC4VFX140) FPGA 之后,可以比MiniSAT(纯软件最好的算法)快90倍。但以上这些也仅仅涉及到综合中的一部分,对于布局布线等其他EDA流程没有深入研究,而且全书也没有特别针对FPGA EDA算法,而是对几个一般性EDA问题做了探讨。

也许未来会有有人出一本专门讲FPGA EDA加速平台的书,再或许,有人会做一款专门用于FPGA EDA加速的SoC出来呢?:)

更多信息可以来这里获取==>>电子技术应用-AET<<