1.2 Low latency(低延时)-1.3Timing(时序)

0赞一 延时对系统频率的关系

FPGA或者说时序电路设计中,主要限制时序速度提高的因素便是延时。这里的延时指的是两个边沿触发器之间的信号传输延时或者说为了完成信号传输所需要的时间。所以需要的传输时间越长,那么这部分的时钟信号也就越慢。

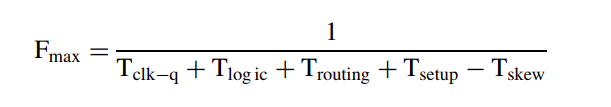

系统最大频率的计算公式如下:

Tclk-q : 指时钟信号从时钟源输出端到触发器Q(时钟输入端)的时间;

Tlogic : 指信号在两个触发器之间的逻辑传输时间,在FPGA里对应的也就是组合逻辑(与、非等逻辑门传输 不需要时钟信号)。所以这里也可以理解为信号通过两触发器之间的逻辑门电路所需要的时间。

Trouting : 指信号在两个触发器之间的导线的传输所需时间。

Tsetup :指信号到达后级触发器,信号在后级触发器数据稳定(有效)所以的时间。

Tshew :指时钟信号抖动

以上的各种时间购成了完成信号传输是所需要的时间。

二 减少延时的各种方法

从一中可知延时的组成因素,针对实际系统Tsetup是器件固有参数,无法修改。时钟Tshew则是时钟源以级布线的相关影响。所以也主要讨论如何减少Tclk_q,Tlogic,Tsetup来减少触发器之间延时。

书中从5个方面来讲解减少延时的方法。

2.1 增加寄存器层次结构

添加寄存器的思路是将两个触发器之间的路径划分开,从而减少了单个周期内的信号延时。

2.2 并行结构与平行化逻辑设计

主体思想是将从逻辑编码设计时,将串行处理结构分解为并行处理逻辑。在设计过程中有两点:

实现并行结构编码;

减少不必要的优先级编码(if…else…)结构。

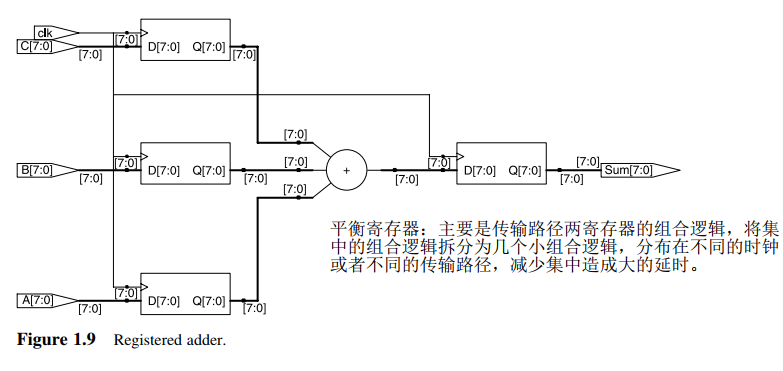

2.3 平衡寄存器

系统的速度主要限制在延时最大的触发器之间。

主体思想是将两触发器之间的大量逻辑重新分割为几个触发器之间,而实现寄存器(触发器)之间的延时的平衡。

举个例子:

这个是三个数进行加法计算,形成两级流水。在两级触发器之间进行加法逻辑进行运算。

下图进行了寄存器平衡之后的逻辑电路,将其中两个数的加法调整到触发器之前,减少了原来触发器之间的延时。

2.4 规划传输路径

对时序要求严格的部分应该分配最短的传输路径。

三 总结

在以速度优先的FPGA的设计过程中,主要便是减少延时来进行设计。这里减少延时的方式便是通过时钟的层级来进行设计,同时为了照顾部分敏感线路而特别设计以保证时序。

这些也是用面积换速度的方法也是较好理解。

注,大米同学知道了如何上传附件便将看的资料也附带上传,里面也又相关的部分笔记。

同时,资料内也有排版错误希望看的各位也细细品味,以免导致错误理解。

![]() Advanced FPGA Design - Architecture, Implementation, and Optimization.pdf

Advanced FPGA Design - Architecture, Implementation, and Optimization.pdf