spartan6 SERDES中原语“BUFPLL”的使用问题

0赞 最近使用Spartan6 的serdes接口,调试一个传输数据的小项目,需求如下:

如图中所示,把板卡A中的数据,通过一对差分线,传输给另一个板卡B,要求数据能完全传输正确,不能有误码、不能丢失数据。经过一个多星期的努力,终于搞定了。在没有随路时钟的条件下,通过使用数据编码和解码(8B/10B编解码)、动态相位调整、循环冗余检测(CRC)码生成器、CRC检测器、数据字节对齐功能、同步丢失状态机等技术,在FPGA中使用纯逻辑,完成了该功能。

在开发过程中,用到了原语“BUFPLL”,这个玩意第一次用到,一些注意事项写出来,供大家参考一下,有不对的,欢迎指正哈。

该原语如图中箭头所指的地方。

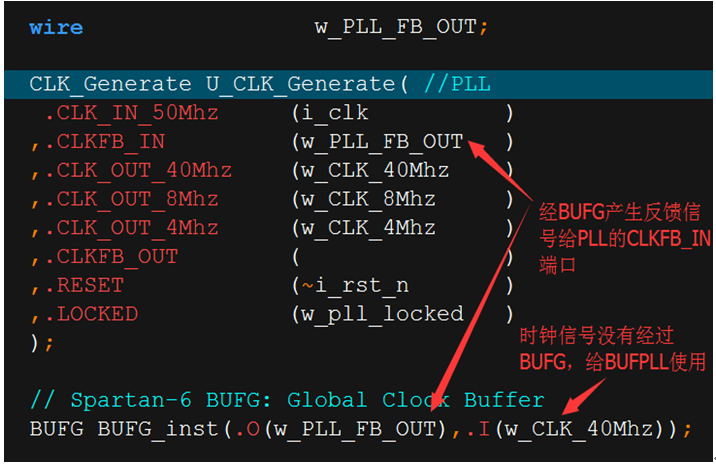

由图中的连接关系可知,经PLL产生的时钟,输入到BUFPLL时没有经过BUFG。如果经过了BUFG,程序编译不过去,有兴趣的同学可以试试。

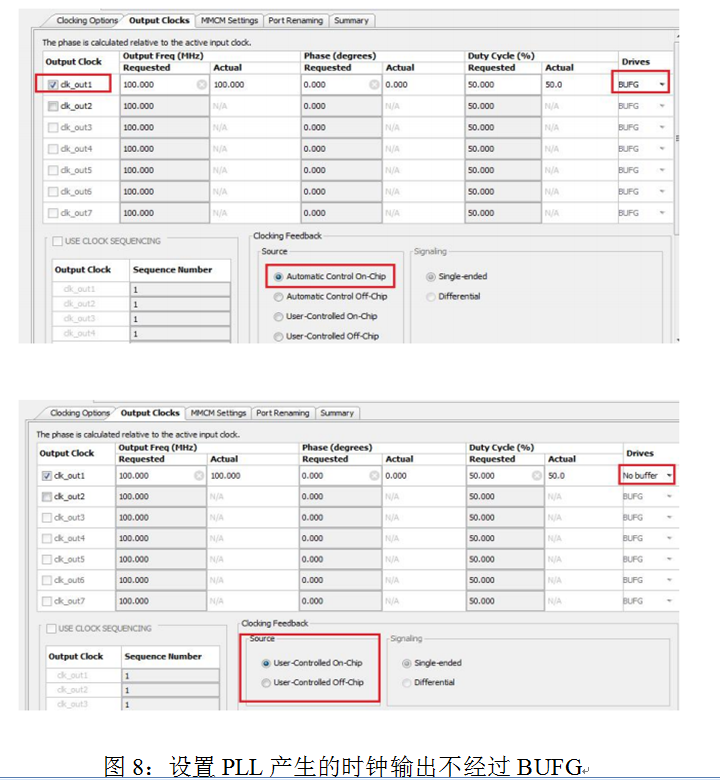

设置PLL产生的时钟不经过BUFG,可参考下图中的步骤,在ISE的IP核中做一些设置:

当设置PLL的输出时钟经过BUFG时,PLL的时钟反馈控制信号会自动添加,如图中显示的“Automatic Control On Chip”。如果PLL输出的时钟没有经过BUFG,那么需要自己给PLL添加反馈信号,如图中显示的选项“User Controlled On-Chip”。

自己添加PLL的反馈信号,可参考如下:

参考资料:1、xapp1064_Source Synchronous Serialization and Deserialization.pdf

2、时序分析约束——Xilinx时钟资源 & ISE时序分析器.pdf

3、AR# 61775 Vivado - Critical warning [Timing 38-1] DLL output pin(s) used on clock modifying cell clk_gen_i0clk_core_i0instmmcm_adv_inst without a feedback net CLKOUT0 CLKOUT1.pdf。

My QQ:2935270450 ,有疑问可以Q我哈!

PS:基于FPGA的视频编解码QQ群:623495899 ,有兴趣的可以进来交流学习哈。