RJIBI-FACE-ZU:基于FPGA的SOC高性能计算平台

0赞

FACE(FPGA Algorithm aCceleration Engine)FPGA算法加速开发引擎是基于FPGA可编程器件构建的一系列算法加速开发引擎平台。其旨在通过借助FPGA与ARM灵活的软硬件全可编程能力、并行算法实现以及动态可重构的特性搭配外围大容量DDR3/DDR4存储以及PCIe、QSFP、SATA等高速接口,助力高校和科研院所相关科研项目的算法开发与部署。

FACE-ZU-15EG是FACE系列中的一员,FACE-ZU平台同时搭载16nm工艺的ZYNQ UltraScale 器件以及28nm的ZYNQ-7000 全可编程器件。

FACE-ZU-15EG平台的主要特征如下:

FACE-ZU 平台

搭载FPGA主器件为:XCZU15EG-2FFVB1156I

板载FPGA协处理器件为:XC7Z015-2CLG485I;

主要接口外设

ZU侧所挂外设(XCZU15EG-2FFVB1156I):

PS DDR4 SODIMM插槽,搭载8GB DDR4 2400Mhz内存条;

PS 千兆以太网

PS USB 3.0接口

PS USB 2.0 x4 接口

PS EMMC 8GB存储器

PS QSPI Flash 512MB存储器

PS Micro-SD卡槽

PS USB-UART接口

PS USB-JTAG接口

PS PCIe(M.2)接口

PL SFP+ 4个光接口

PL FMC扩展连接器 5个

FMC-A:4对GTH,6对LVDS

FMC-B:4对GTH,34对LVDS

FMC-C:4对GTH,34对LVDS

FMC-D:4对GTH,34对LVDS

FMC-E:4对GTH,34对LVDS

Z7侧所挂外设(XC7Z015-2CLG485I):

PS DDR3 1024MB存储器;

PS QSPI Flash 256MB存储器

PS 千兆以太网

PS EMMC 8GB存储器

PS Micro-SD卡槽

PS CAN接口2个

PS USB-UART接口

PS USB-JTAG接口

PL FMC扩展连接器1个:4对GTH,34对LVDS

典型参考案例:

• 硬件平台介绍

• 硬件模块

• 快速上手

• 开发流程介绍

• 开发框架

• 环境搭建

• Vivado流程

• HSI流程

• PetaLinux流程

• 部署

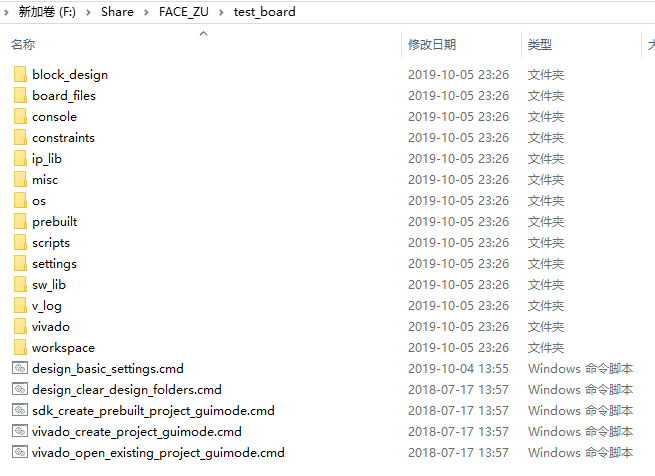

开发流程介绍-开发框架

• TE开发框架

• 支持一键创建Vivado设计

• 支持一键打开工程

• 支持一键编译HSI软件工程

• 支持一键生成配置文件

• 开发框架安装

• 解压框架安装包至PC目录

• Vivado开发环境安装

• 安装Vivado 2018.2 系统版本

• PetaLinux开发环境安装

• 安装PetaLinux 2018.2版本

• 需Linux OS下安装,推荐Ubuntu16.04版本

• 开发框架安装

• 解压框架安装包至PC目录

• 开发框架配置

• 使用文本编辑器打开开发框架下的:design_basic_settings.cmd

• 指定Xilinx环境安装路径与版本信息

• (可选)指定7z.exe工具安装路径

• Petalinux安装

• 参考Petalinux安装手册

• 安装必备库

• 安装Petalinux

•不得使用root用户安装

• 将Petalinux编译结果copy至开发框架对应目录下

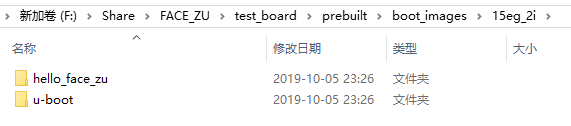

• 在prebuild目录boot_images下,HSI已将对应软件(helloworld、uboot)编译结果导出(BOOT.BIN文件)

• 将BOOT.BIN文件copy至SD卡即可启动对应软件

• 若启动Petalinux则还需将上述Petalinux编译结果一同copy至SD卡根目录

• 将SD卡插入ZU Micro-SD卡槽

• 打开开关上电

• 接入USB公对公线缆至PC,启动串口终端软件

• 即可进入ZU Linuix系统

用户手册目录

3.1 Zynq UltraScale+ XCZU15EG MPSoC 8

获取详细资料请联系我们

联系方式:022-58066188,18611717427,

邮箱:Sales@rjibi.com、andrew.li@rjibi.com

阿吉毕科技