PCIe从入门到精通之七:PCIe设备的配置空间简介

0赞0,引言

在上一篇文章《PCIe从入门到精通之六:PCIe数据包packet的神奇之旅》中,我们介绍了PCIe数据包如何在各层中传输的。在这一篇文章中我们继续介绍PCIe设备的配置空间。

所有PCIe主题的文章都会收录在《深入浅出聊PCIe》合集里,欢迎评阅。

需要下载PCIe学习资料标准的朋友(pdf格式),请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载链接。

一,PCIe设备内的组件(温故而知新)

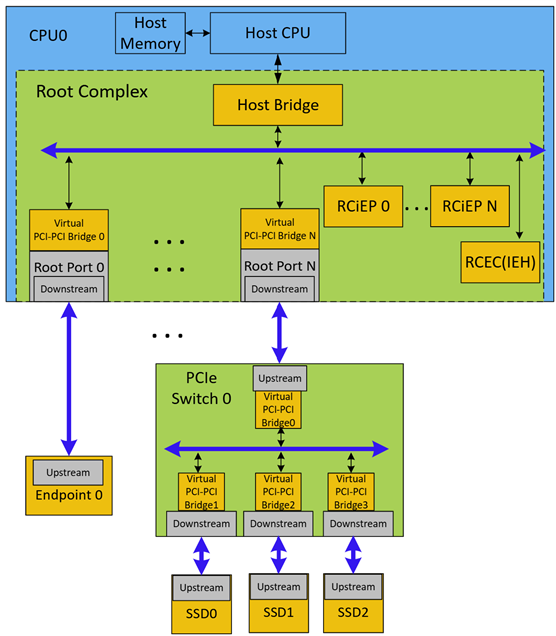

下图是我们在前面的章节里面用到的PCIe体系内的组件图。我们再次把它拿出来重新温习一遍。

如下图所示,PCIe体系有三大devices,分别是Root Complex,switch和endpoint。Root Complex里面还有host bridge, PCI-PCI bridge, Root Port,RCiEP和RCEC。Switch里面含有PCI-PCI bridge, upstream port和downstream port。 PCIe endpoint device里面含有upstream port。

每个 PCIe link都源自一个逻辑的 PCI-PCI bridge,并被映射到配置空间中,作为该PCI-PCI bridge的secondary bus,如下图中的蓝色箭头。

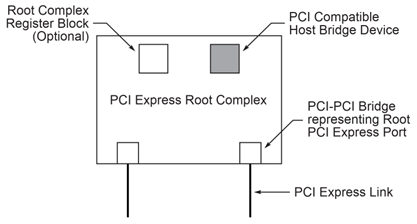

如下图所示,Root port是一种 PCI-PCI 桥接器结构,它从 PCI Express Root complex产生一条 PCIe link。

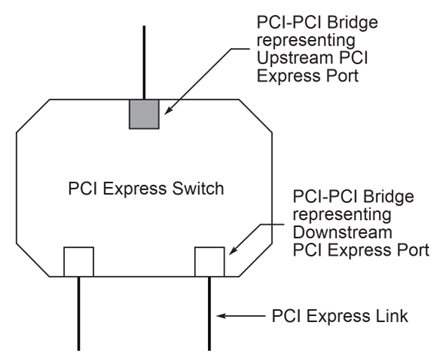

如下图所示,PCIe Switch由多个的 PCI-PCI bridge组成,这些PCI-PCI bridge将PCEe link连接到Switch的Internal logic PCIe bus。Switch上游端口是一种 PCI-PCI bridge,该PCI-PCI bridge的secondary bus代表Switch的内部路由逻辑。交换机下游端口也是一个PCI-PCI bridge,这个PCI-PCI bridge负责将Switch的Internal logic PCIe bus连接外部的PCIe Bus上。只有代表Switch下游端口的 PCI-PCI bridge才可能出现在internal bus上。

二,哪些PCIe组件有配置空间(Configuration Space)?

为了与 PCI 软件配置机制保持兼容性,所有 PCIe组件都具有与 PCI 兼容的配置空间(256字节)之外,还具有PCIe device特有的扩展配置空间。下面的PCIe device的组件都有PCIe配置空间。

Root Complex:Host bridge, RCiEP, RCEC和PCI-PCI bridge with root port

Switch:PCI-PCI bridge with Upstream port和PCI-PCI bridge with downstream port

Endpoint: Upstream port(Endpoint device可能包含多达8个function,每个function都有一个PCIe配置空间)。

三,PCIe配置空间(Configuration Space)的结构

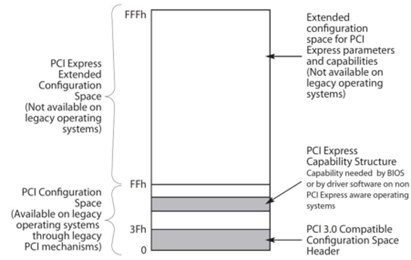

PCI Express 配置空间被划分为一个与PCI兼容的配置空间(PCI Compatible Configuration Space)和一个PCIe扩展配置空间(PCIe Extended Configuration Space)。如下图所示,PCI兼容的配置空间由前 256 字节组成(Byte 0h~FFh); PCI Express 将每个function的配置空间扩展到了 4096 字节(4KB,FFFh), 而PCIe扩展配置空间则由除PCI兼容的配置空间外剩余的配置空间组成(Byte 100h~FFFh).

在PCI兼容的配置空间里,前0h~3Fh存放的是PCI header(device基本信息),后面的40h~FFh存放的是PCIe Capability Structure(device都有哪些本领)。

在扩展配置空间里(Byte 100h~FFFh),全部存放的是PCIe Extended Parameters and Capability Structure。

Capability Structure占有配置空间的大部分size,device通过Capability Structure告诉Host它有哪些本领,它有多牛X,以便以后为Host工作时多要些筹码、多加点工资。

四,如何访问PCIe配置空间?

· PCI-compatible Configuration Access Mechanism (CAM)

在PCI Local Bus Specification Revision 3.0规范中,章节3.2.2.3.2. Software Generation of Configuration Transactions介绍了通过IO port CONFIG_ADDRESS(CF8h)和CONFIG_DATA(CFCh)访问PCI 兼容的配置空间(00h~ffh)。但是这种方式不能用来访问PCI Express 扩展配置空间(Byte 100h~FFFh)。

· PCI Express Enhanced Configuration Access Mechanism (ECAM)

所有的PCIe配置空间的寄存器都会被map到标准的memory空间里(flat memory-mapped address space),我们只要找到它们在memory空间里的address,我们就可以通过对memory空间的直接访问进而转化成对PCIe配置空间的访问。

ECAM 采用了一个平坦的内存映射地址空间来访问设备配置寄存器。在这种情况下,内存地址决定了所访问的配置寄存器,而内存数据(对于写入操作)会进行更新,或者(对于读取操作)会返回所访问寄存器的内容。

ECAM既可以对PCI 兼容的配置空间进行访问,又可以对PCIe扩展配置空间进行访问。

这两种访问PCIe配置空间的方式将在后面的专门章节详细介绍。

五,总结

每个PCI-PCI bridge的下游都连接一个PCIe Bus。每个PCIe组件都是位于特定的PCIe bus上,并都有自己的PCIe配置空间。PCIe配置空间的访问可以有PCI-compatible Configuration Mechanism和PCI Express Enhanced Configuration Access Mechanism (ECAM)两种。

PCIe设备的配置空间都一模一样,它们都被映射到内存空间(Memory Space)。那么软件是怎么区分访问的内存是哪个设备或者软件需要访问某个设备时是怎么指向这个特定的设备?下一章我们将详细讲解PCIe设备的身份证ID。

敬请关注下一篇:《PCIe从入门到精通之八:PCIe设备的身份证ID》

需要以下参考文献(PCIe标准)的朋友,请关注本微信公众号“硬件工程师宝典”,在对话框内回复“PCIe”,将获取标准下载连接。

百度网盘分享的文件