高速存储传输系统之数据缓存控制器设计2

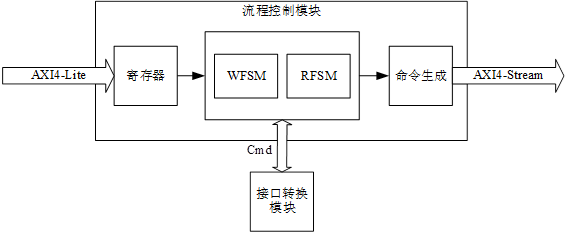

0赞流程控制模块的框图如图1所示,该模块主要由寄存器、读状态机、写状态机和命令生成模块组成。

图1 流程控制框图

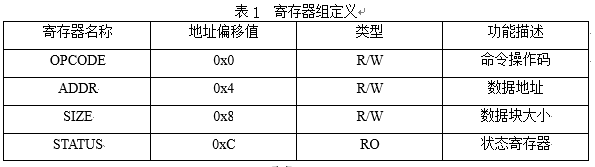

流程控制模块的工作首先从配置模块中的寄存器组开始,由于只需要配置四个寄存器,因此使用资源占用较小的AXI_Lite总线接口来实现。表1所示为流程控制模块内寄存器的类型与功能描述等信息。

表1中的操作码寄存器(OPCODE)用于表示命令类型,流程控制模块通过操作码寄存器不同的值来组装相应的NVMe命令,本设计主要实现了NVMe协议中常用的识别、读、写、SMART、FLUSH以及关机命令。数据地址寄存器(ADDR)用于指定要读取的数据块的起始地址。数据块大小寄存器(SIZE)用于指定要读取的数据块的大小。状态寄存器(STATUS)为只读状态,用来指示当前控制器的状态信息。

为了提升系统性能,将读写划分为两个传输通道,每个通道可独立工作。因此需要通过两个状态机来实现了读写控制。同时,采用乒乓操作的方式进行读写,通过A和B两个缓存区之间的切换来使输入输出数据可以无间断地进行传输,并减小NVMe命令执行过程中产生的延迟。

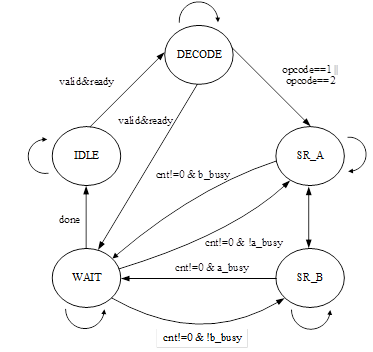

读状态机跳转图如图2所示。

图2 读状态机跳转图

IDLE:空闲状态,该状态为该模块上电后的初始化状态,在该状态下等待用户配置完最后一个寄存器SIZE后,状态跳转至DECOE状态,否则维持在IDLE状态。

DECODE:命令解析状态,在该状态下首先需要判断用户逻辑发起的命令请求是否为读取命令,若为读取命令,则根据配置的ADDR寄存器和SIZE寄存器的值以及设置的缓冲区大小来计算出需要切换多少次缓存区,并将切换次数记录在buf_cnt寄存器中,接着下一个状态跳转至SR_A状态。若不是读取命令,则在该状态下组装相应的NVMe命令并发送至NVMe Host控制器,发送完成后,状态跳转至WAIT状态,等待指令执行完成。

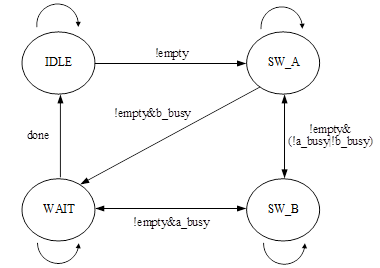

写状态机跳转图如图3所示。

图3 写状态机跳转图

其中

IDLE:空闲状态,该状态为该模块上电后的初始化状态,在该状态下等待接口转换模块输入的empty信号为低电平时,表示有数据输入,状态跳转至SW_A状态,否则维持在IDLE状态。

SW_A:发送A区域写命令状态,该状态下等待缓存区域A存满后,控制命令生成模块组装区域A的NVMe写命令并通过AXI4_Stream接口发送给NVMe Host控制器。发送完成后若b_busy信号有效且empty信号为低电平时,状态跳转至WAIT,若b_busy信号为低电平且empty信号为低电平时,状态跳转至SC_B状态,此外,在设计中还添加了超时检测机制,通过计数器实现,当长时间无数据输入时,则控制命令生成模块组装相应大小的NVMe写命令,发送至NVMe Host控制器。

SW_B:发送B区域写命令状态,该状态下根据接口转换模块输入的转换数据量信息生成相应的NVMe写命令并通过AXI4_Stream接口发送给NVMe Host控制器。发送完成后若a_busy信号有效且empty信号为低电平时,状态跳转至WAIT,若a_busy信号为低电平且empty信号为低电平时,状态跳转至SC_A状态,该状态下同样使用超时检测。