异步复位,同步释放

0赞观《深入浅出玩转FPGA》之异步复位,同步释放

一 异步复位与同步复位

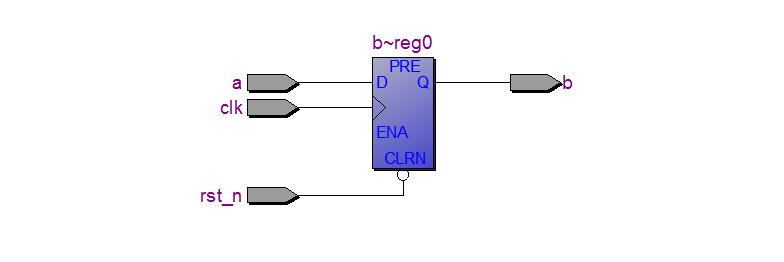

异步复位--代码--RTL及仿真波形

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

b<= 1'b0;

else

b<= a;

异步复位--代码--RTL

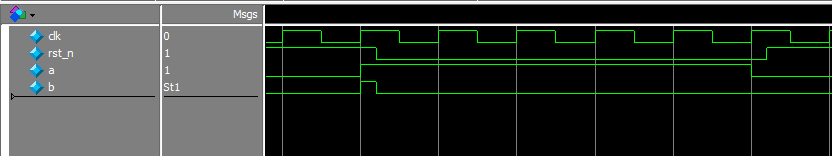

always@(posedge clk )begin

if(!rst_n)

b<= 1'b0;

else

b<= a;

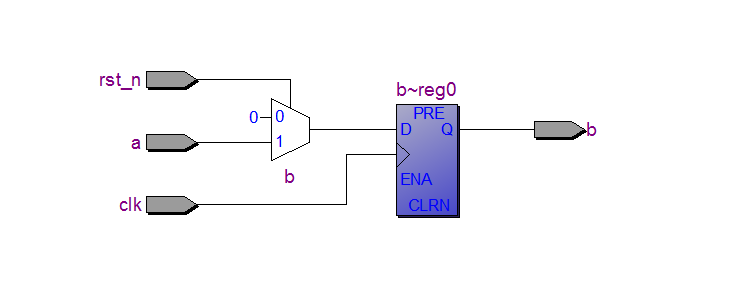

二 异步复位,同步释放

异步复位会影响寄存器的recovery时间,引起设计的稳定性问题,尤其对于状态机的无意识复位,将导致进入不确定的状态,同步复位也存在类似的问题,而且对于不带同步复位专用端口的器件将会增加额外的逻辑资源

异步复位的同步化,应用边沿检测的部分思维,用最高时钟打慢几排,便实现了与最高时钟的同步。

//-------------------------------------------------

`timescale 1ns/1ns

module synchronism_design(

clk,

rst_n,

rst_nr2//异步复位,同步释放

);

inputclk;

inputrst_n;

output rst_nr2;

//两级层叠复位电路,低电平复位

reg rst_nr1,rst_nr2;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr1 <=1'b0;

end

else

begin

rst_nr1 <=1'b1;

end

end

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

rst_nr2 <= 1'b0;

end

else

begin

rst_nr2 <=rst_nr1;

end

end

endmodule

//---------------------------------------------------------------------------------------------------------

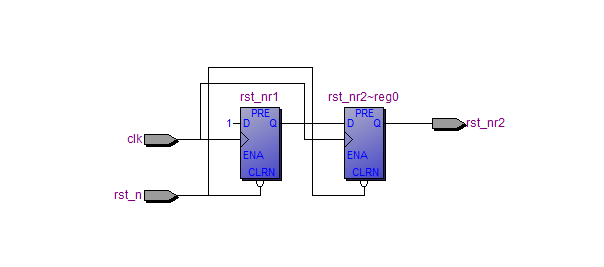

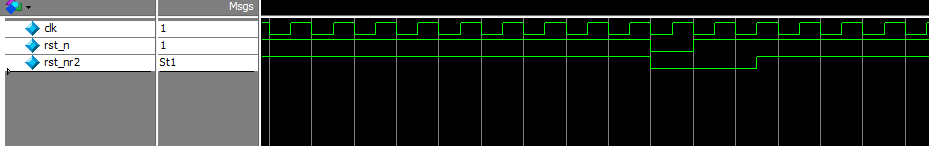

仿真波形如下:

// rst_n没到来时,rst_n2保持为1的状态;当rst_n有效时,rst_nr2输出两个时钟周期的低电平