转 FPGA 内部双口块RAM 读写实现

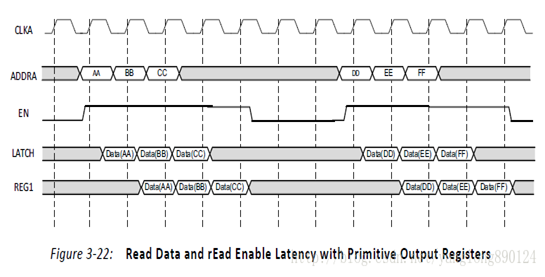

0赞FPGA 内部块RAM 的读时序如下图:

可知,块RAM的读延时为两个时钟周期。

FPGA 内部块RAM 的写时序如下图:

可知,块RAM 的写延时为0,但是RAM 中的内容是在写的下一个时钟改变。

在ISE下实现对FPGA内部块RAM 的读写代码:

1. module TOP(

2. input USER_CLK

3. );

4.

5. `define DLY #1

6. reg FPGA_Enable=0;

7. reg[3:0] FPGA_Write_Enable=4'h0;

8. reg[31:0] FPGA_Address=0;

9. reg[31:0] FPGA_Write_Data=0;

10. reg[31:0] FPGA_Read_Data_reg=0;

11. wire[31:0] FPGA_Read_Data;

12.

13. reg[10:0] count=0;

14. always @ (posedge USER_CLK)

15. begin

16. count <= count + 1;

17. if(count<=100)

18. begin

19. FPGA_Enable <= 0;

20. FPGA_Write_Enable <= 4'h0;

21. end

22. else if((count <= 105)&&(count >100))

23. begin

24. FPGA_Enable <= 1;

25. FPGA_Write_Enable <= 4'hf;

26. FPGA_Address <= FPGA_Address + 4;

27. FPGA_Write_Data <= FPGA_Write_Data + 1;

28. end

29. else if((count <= 110)&&(count >105))

30. begin

31. FPGA_Enable <= 0;

32. FPGA_Write_Enable <= 4'h0;

33. FPGA_Address <= 0;

34. FPGA_Write_Data <= 0;

35. end

36. else if((count <= 117)&&(count >110))

37. begin

38. FPGA_Enable <= 1;

39. FPGA_Write_Enable <= 4'h0;

40. FPGA_Read_Data_reg <= FPGA_Read_Data;

41. FPGA_Address <= FPGA_Address + 4;

42. end

43. else if(count == 118)

44. begin

45. FPGA_Enable <= 0;

46. count <= count;

47.

48. end

49. end

50.

51. BBBB your_instance_name (

52. .clka(USER_CLK), // input clka

53. .ena(FPGA_Enable), // input ena

54. .wea(FPGA_Write_Enable), // input [3 : 0] wea

55. .addra(FPGA_Address), // input [31 : 0] addra

56. .dina(FPGA_Write_Data), // input [31 : 0] dina

57. .douta(FPGA_Read_Data), // output [31 : 0] douta

58.

59.

60. .clkb(clkb), // input clkb

61. .enb(enb), // input enb

62. .web(web), // input [3 : 0] web

63. .addrb(addrb), // input [31 : 0] addrb

64. .dinb(dinb), // input [31 : 0] dinb

65. .doutb(doutb) // output [31 : 0] doutb

66. );

67. endmodule

效果图:

从上图可以看出,在地址4~20里面写入了1-5的数,数据读出的时候对应地址的数据都延时了两个时钟周期才输出。