Atlys 视频监控 基于双摄像头的HDMI视频系统(一)

0赞

系统通过FPGA的通用逻辑实现了一个MicroBlaze软核处理器,来完成对系统各个模块进行管理和任务调度。而视频采集板卡、DDR2存储芯片、HDMI显示接口等均采用IP核的设计,设计生成相应的控制IP

核,用以直接实现相应功能以及对其进行控制。

软件:XILINX ISE 13.2

硬件:Atlys Vmodcam VHDCI线

Atlys

Atlys开发板是一块基于Xilinx Spartan 6 LX45 FPGA的完整易用的数字电路开发平台。其板载高端外围接口涵盖了千兆以太网、HDMI视频输入输出、128MByte DDR2存储阵列、音频及USB接口。因此Atlys对基于嵌入式处理器(如Xilinx的MicroBlaze)构建的完整数字系统来说是个理想的选 择。Atlys完全支持Xilinx CAD工具,包括ChipScope, EDK以及免费的WebPack版本。所以,就避免了设计中的额外成本。

● Spartan-6 LX45对高性能逻辑电路设计进行了优化,并提供:

● 6,822单元,每个包含四个6输出LUT以及8个触发器

● 2.1MBits快速块存储器

● 4 个时钟模块(包括8个DCM以及4个PLL)

● 6 个锁相环

● 58 个DSP单元

● 支持500MHz以上时钟速度

VMODCAM

● 两个独立的 Aptina MT9D112 两百万像素CMOS数字图像传感器

● 最大分辨率1600x1200,15帧每秒

● 63mm相机间距(立体基线)

● 10位原色深度

● I2C控制总线

● Bayer, RGB, YCrCb 输出格式

● 自动曝光, 增益及白色平衡

● 强大的图像修正算法

● 图像缩放

● FIFO输出

● 68管脚female VHDCI 连接器

VmodCAM板卡通过VHDCI连接器为任何Digilent的FPGA系统提供了数字图像处理能力。它的特色是两个Aptina MT9D112 两百万像素的CMOS数字图像传感器。传感器能提供的最大帧数是15帧每秒,帧频取决于分辨率。

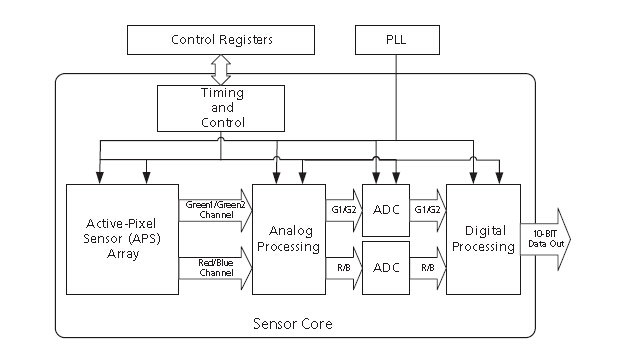

VmodCAM板卡的片上系统设计集成了一个图像流处理器并能够选择输出的格式,缩放大小和特殊效果。集成的PLL(锁相环)和微处理器提供了一个灵活的串行控制接口。输出的数据输送到并行总线上,数据格式有YCrCb,RGB,或者原始Bayer格式。

可以独立地控制两个MT9D112相机,并获得两个分离的,同步的图像内容。通过一个双线接口来控制它们。每个相机都有一个两百万像素的传感器阵列,使用Bayer滤色矩阵的方式排列。传感器的读出数据是10位的,并支持行或列的跳跃和装仓。

MT9D112的内部结构

摄像头系统在工作前,必须要正确配置。这不但包括设置图像参数,比如分辨率和输出格式,还包括PLL配置和微处理器的处理顺序。

在这些操作序列中,首先设置启动顺序和复位顺序,然后理解控制接口,这些接口用于配置摄像头。

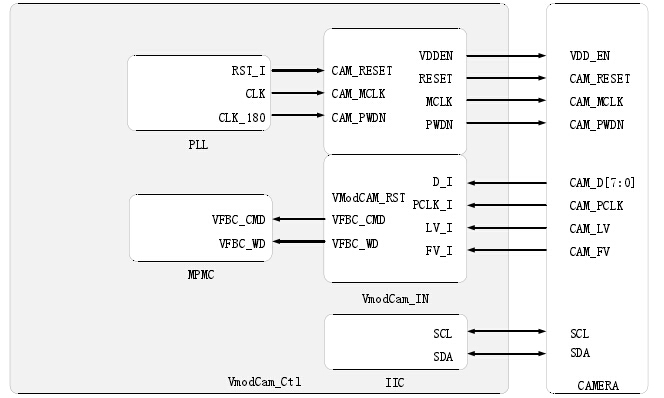

视频数据的采集主要由VmodCam_IN, IIC, xps_pll等三个IP核协同完成,xps_pll主要为视频采集板卡提供主时钟、复位信号;IIC控制器则用于对视频采集板卡视频输出模式进行配置;

VmodCam_ IN IP核是Digilent开发完成的IP核,主要完成对摄像头采集的视频数据进行接收、初步缓存,并通过VFBC接口写入DDR2内存。

给出FPGA与视频采集模块中单个摄像头的端口映射图,FPGA可独立的对每个摄像头进行控制及视频数据的采集。FPGA与每个摄像头有十个端口连接:其中有4个输入端口、4个输出端口、2个双向端口。通过这些端口 FPGA完成对摄像头的控制、视频数据接收、参数配置等操作。

FPGA对摄像头的控制操作,主要通过4个输出端口来进行,包括:使能信号VEN、复位信号RST、准备信号PDN、为其提供的主时钟信号MCLK等;这些信号由PLL核来提供;

FPGA对摄像头的参数配置,是通过两个双向端口、护C总线(SDA, SCL信号)来进行;

FPGA对摄像头视频数据的接收,则是通过4个输入端口来完成,包括:数据信号DATA、像素时钟PCLK、行同步LV、场同步FV;根据摄像头配置方案的不同,输出参数产生相应的变化。在完成视频数据接收并缓存后,通过VFBC送入DDR2存储部分进行存储。