【再说FPGA】彰显性能和生产优势,Altera展示28nm全线产品

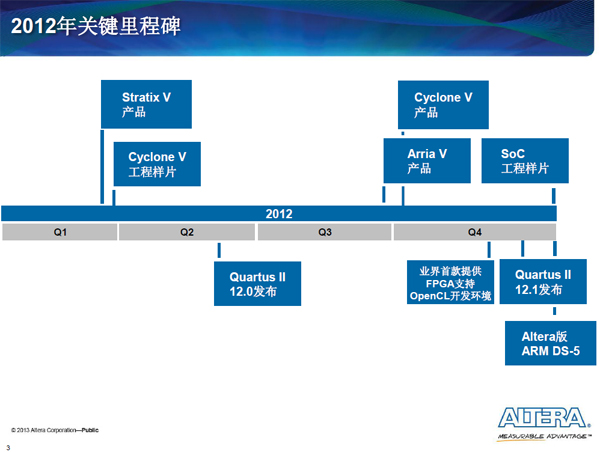

0赞这次的发布会,Altera可以说是煞费苦心,不同产品线的工程师在Jennifer的带领下全线出击,现场产品演示与交流,突出Altera 28nm产品的几大亮点,为2012年做了一个全面的总结。

高中低三系列全面出击 自有收发器技术保持领先

Stratix V作为Altera的旗舰产品,于2011年4月提供工程样片,2012年的第一季度进入量产阶段,现所有系列型号都已投产。Altera是唯一一家公开了基于批量产品的特征报告,提供基于批量硅片和电路板的背板特征数据。Stratix V增强了EyeQ特性支持管芯仪表,在2-D均衡后提供眼图监视,显示设计是否够完善,是否还有设计余量,以便工程师后续工作。

Altera亚太区产品市场经理 刘斌演示14.1Gb/s背板收发器

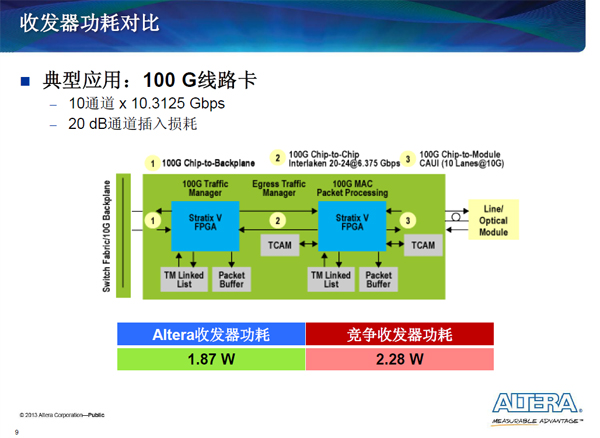

芯片的功耗由以下几个组成部分:芯片的静态功耗主要由芯片规模和工艺水平决定;内核的动态功耗由查找表、寄存器工作产生、I\O功耗、收发器功耗。

在有限通信领域,特别100Gb/s、40Gb/s,400Gb/s高速通信领域,收发器的功耗就尤为重要。

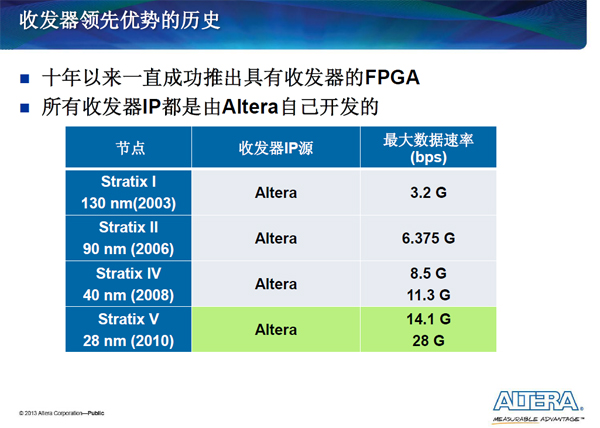

从2003年,Altera在Stratix I 集成3.2Gb/s收发器以来,Altera的所有收发器IP都是自己开发的,Altera通过架构设计专门对收发器功耗做了改进,取得了丰硕的成果。在Stratix V具有28GGb/s芯片至芯片收发器,支持新的CFP2 100GGb/s光模块连接,支持14.1GGb/s背板收发器,应用扩展到数据中心、存储器市场、网络搜索、网络安全领域。

Arria V产品系列从2012年8月开始量产,目前已有70%以上的系列型号投产。Arria V兼顾性能、成本和功耗,填补了中端应用向高端应用转移的空隙。主要应用在广播,无线射频系统,基带等领域。2013年上半年Arria V将全部量产。Arria V也将推出SoC FPGA。

Cyclone系列产品在市场上广受欢迎,成本最低,功耗最低。Cyclone V从工程样片到量产只用了6个月的时间,主要应用在远端射频模块、工业领域等。

Cyclone V SoC FPGA

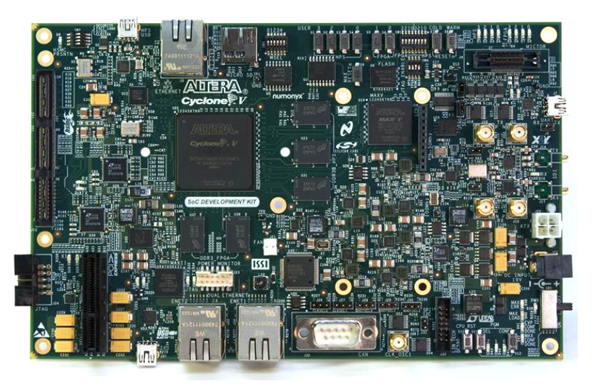

Cyclone V SoC FPGA是大家期待已久的,目前已提供工程样片。SoC FPGA集成32位ECC保证了数据完整性和信号可靠性;具有灵活的启动能力,可以先启动ARM也可以先启动FPGA;集成PCIe硬核,用于数据互联。

针对SoC FPGA设计的虚拟目标平台是一个嵌入式软件开发工具。让工程师在硬件没拿到前,就可以开始嵌入式软件的开发仿真,节省数月的开发时间加快产品上市时间。通过虚拟目标平台帮助客户讲应用软件导入到SoC中,与真实的芯片可做到寄存器兼容,二进制兼容。

ARM针对Altera SoC FPGA提供业界第一款也是唯一一款FPGA自适应嵌入式软件工具包。SoC FPGA的推出虽然比对手晚了些,但有ARM特制工具包的支持,也可以后来居上。呵呵!

Altera自制的基于SoC FPGA的开发板,资源应该比Zedboard丰富很多

通过与工程师面对面的交流了解到,QSys通过协议转换,可以把以前基于Avalon、Nios的设计转换到AXI,通过IP形式应用到SoC FPGA。这对广大工程师来说是一个福音,以前的项目资源可以好好的继承。

据悉,Altera稍后还会推出Arria V SoC FPGA。

OpenCL与AutoESL

笔者一直疑惑OpenCL和X公司的AutoESL的区别,这次通过与工程师的交流总算闹了个明白。

AutoESL解决的是输入的问题,OpenCL解决的是系统的问题。AutoESL类似Altera以前的“C to H”。OpenCL解决的是如何利用硬件的空间并行性,让算法并行展开的问题。

OpenCL实际上定义了一个接口,定义了主处理器与加速器的一个接口,是一个架构的解决方案。Altera目前推出的OpenCL 平台支持X86+Altera FPGA,FPGA担任协处理器的角色。OpenCL是FPGA向新领域等扩展的一个有利武器,如云计算、数据挖掘、海量数据处理。按照官方说法是加速了FPGA在异构系统中的算法实现。这一点,老莫的博客有比较多的论述(http://blog.chinaaet.com/molf)。