简易数字信号传输性能分析仪

0赞摘 要

NWX8899

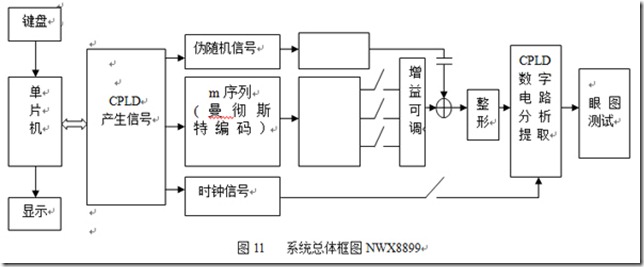

本作品设计一个简易数字信号传输性能分析仪,通过对个个方案的论证,最终选择两片CPLD做为核心器件。首先通过单片机控制时钟的分频,使用可编程逻辑器件CPLD以方便的产生不同数据率的伪随机信号,同时用12864液晶显示数据率及峰峰值。为了滤去整流输出电压中的纹波。通过二阶巴特沃斯滤波器滤波同时产生高增益的滤波信号。然后叠加伪随机信号用示波器显示眼图。对于产生的m序列是否采用曼彻斯特编码,则使用开关控制单片机来选择。通过数字分析电路与CPLD提取同步信号,再次用示波器显示眼图。本系统结构清晰,经过测试基本完成题目要求。

关键词:CPLD 伪随机信号 巴特沃斯滤波器 同步信号 眼图

Abstract

The work to design a simple digital signal transmission performance analyzer, through a program of demonstration, finally choice two CPLD devices as the core of system.The design of the first chip to control the clock by the frequency, the use of programmable logic device CPLD to easily generate different pseudo-random signal data rate, and liquid crystal display with 12864 and the peak data rate. To filter the rectifier output voltage ripple. Through second-order Butterworth filter with the filter while producing high-gain signal. Then superimposed pseudo-random signal with an oscilloscope display eye. For m-sequences are generated using Manchester coding is used to select single-chip switch control. Through statistical analysis to extract synchronization signals and CPLD circuits, once again shows the eye diagram with an oscilloscope.The system structure is clear, after the basic completion of the test question.

Key words:CPLD Pseudo-random signal Butterworth filter Sync Eye diagram

简易数字信号传输性能分析仪(E题)

【本科组】

1系统方案

本系统主要由滤波模块、数字信号(m序列)产生模块、同步信号提取模块、眼图显示方式组成。下面分别论证这几个模块的选择。

1.1低通滤波电路的论证与选择

方案一:采用切比雪夫滤波器。其采用的是切比雪夫传递函数,也有高通、低通、带通、高阻、带阻等多种滤波器类型。切比雪夫滤波器的过渡带很窄,但内部的幅频特性却很不稳定。

方案二:采用一阶巴特沃斯滤波器。巴特沃斯滤波器的特点是通频带内的频率响应曲线最大限度平坦,没有起伏,而在阻频带则逐渐下降为零。一阶巴特沃斯滤波器的衰减率为每倍频6分贝,每十倍频20分贝。幅频特性效果不好,而且达不到题目要求。

方案三:采用二阶巴特沃斯滤波器。二阶巴特沃斯滤波器的衰减率为每倍频12分贝、 三阶巴特沃斯滤波器的衰减率为每倍频18分贝、如此类推。巴特沃斯滤波器的振幅对角频率单调下降,并且也是唯一的无论阶数,振幅对角频率曲线都保持同样的形状的滤波器。只不过滤波器阶数越高,在阻频带振幅衰减速度越快。其他滤波器高阶的振幅对角频率图和低级数的振幅对角频率有不同的形状。

综合以上三种方案,选择方案三。

1.2数字信号(m序列)产生模块的论证与选择

方案一:采用D触发器74ls74产生。其特点是产生序列速度可以很快,但由于硬件电路固有的不便修改性,该方法仅仅对一些特殊的本原多项式有效。

图1 D触发器产生m序列

方案二:采用单片机产生。采用AT89S52来实现。该8位单片机有256B的内部RAM和8KB的![]() PROM 。m序列通过P0口输出至外部设备。在m序列产生模块子程序中,m序列发生器实际上是用其反馈移位寄存器(FSR,feedback shift register )。为了便于操作,该FSR应该位于AT89S52的位地址空间。选择片内20H地址单元为其起始地址,其中定义单元的最低位为

PROM 。m序列通过P0口输出至外部设备。在m序列产生模块子程序中,m序列发生器实际上是用其反馈移位寄存器(FSR,feedback shift register )。为了便于操作,该FSR应该位于AT89S52的位地址空间。选择片内20H地址单元为其起始地址,其中定义单元的最低位为![]() (即第n级寄存器),则FSR的

(即第n级寄存器),则FSR的![]() (即第一位寄存器)依据级数n的大小位于片内20H~2FH单元的某一位。该方法用单片机的数据查询方式,取出相应的存储在EPROM中的某一固定级数n的伪码信号,简化的求解反馈函数值的计算,速度较快。但是不易精确产生波特率步进可调的序列。

(即第一位寄存器)依据级数n的大小位于片内20H~2FH单元的某一位。该方法用单片机的数据查询方式,取出相应的存储在EPROM中的某一固定级数n的伪码信号,简化的求解反馈函数值的计算,速度较快。但是不易精确产生波特率步进可调的序列。

方案三:采用CPLD产生。采用行为描述方式用VHDL语言对该逻辑进行硬件描述。设计的系统具有体积小、重量轻、功耗小、速度快、价格低、可靠性高、设计周期短等优点。为产生信号![]() 为

为![]() 的m序列,我们采用Altera公司的Quartus ║软件,使用硬件描述语言VHDL对CPLD进行编程。

的m序列,我们采用Altera公司的Quartus ║软件,使用硬件描述语言VHDL对CPLD进行编程。

综合以上三种方案,选择方案三。

1.3 同步信号提取的论证与选择

方案一:数字锁相环提取位同步信号。由于数字锁相环的输入是经过微分和全波整流后的信号, 电路由码型变换器、鉴相器、控制调节器组成。电路复杂。

方案二:采用CPLD快速提取位同步信号。利用CPLD内部丰富的资源来提取同步为信号。

综合考虑采用方案二。

1.4 眼图显示方式的论证与选择

方案一:采用X通道触发Y通道显示。把时钟信号接入X通道,m序列信号接入Y通道。在每个时钟的上升沿使m序列信号发生跳变。

方案二:采用外触发方式显示。将时钟信号接入外触发端,调节示波器触发模式即可。

综合以上两种方案,选择方案二。

2系统理论分析与计算

2.1 低通滤波电路的分析与计算

2.1.1 滤波分析

经典滤波的概念,是根据富立叶分析和变换提出的一个工程概念。根据高等数学理论,任何一个满足一定条件的信号,都可以被看成是由无限个正弦波叠加而成。换句话说,就是工程信号是不同频率的正弦波线性叠加而成的,组成信号的不同频率的正弦波叫做信号的频率成分或叫做谐波成分。只允许一定频率范围内的信号成分正常通过,而阻止另一部分频率成分通过的电路,叫做经典滤波器。

2.1.2 低通滤波电路的计算

在分析有源滤波电路时,一般都通过”拉氏变换”,将电压与电流变换成“象函数“U(s)和I(s),因而电阻的R(s)=R,电容的![]() (s)=1/sC,电感的

(s)=1/sC,电感的![]() (s)=sL,输出量与输入量之比称为传递函数,即

(s)=sL,输出量与输入量之比称为传递函数,即 ![]()

将电压电阻值代入公式f=1/2![]()

![]() ,根据频率100K,200K,500K算出相应的电阻和电容值。

,根据频率100K,200K,500K算出相应的电阻和电容值。

2.2 m序列产生的分析

2.2.1 m序列

由线性反馈移位寄存器产生的周期最长的二进制数字序列称为最大长度反馈移位寄存器序列,通常称为m序列。

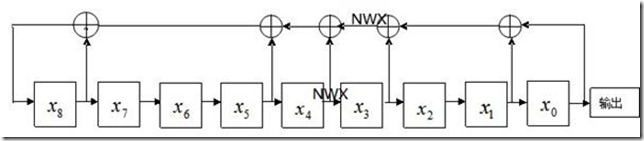

2.2.2 m序列产生原理

移位寄存器是由n个串接的双态存储器(寄存器)和一个移位时钟发生器以及一个由模2加法器组成的反馈逻辑线路组成,每个双态存储器称为移存器的级,每一级只能有两种不同状态分别用0和1表示。移位时钟到来时使每一级的存数(即状态)向下一级移动,成为下一级的新存数。

图2 线性反馈移位寄存器原理方框图

2.2.3 误差的计算与分析

由于采用的是20M晶振,要产生数据率为10~100kpbs步进10kpbs的信号 。分频倍数如表1所示。而对于10Mbps的伪随机信号 则不需分频。

表1 信号 的分频倍数及误差值

|

数据率 Kbps |

10 |

20 |

30 |

40 |

50 |

60 |

70 |

80 |

90 |

100 |

|

时钟频率 KHz |

20 |

40 |

60 |

80 |

100 |

120 |

140 |

160 |

180 |

200 |

|

分频倍数 |

500 |

250 |

167 |

125 |

100 |

83 |

71 |

62 |

56 |

50 |

|

误差 % |

0 |

0 |

0.6 |

0 |

0 |

0.36 |

0.6 |

0.5 |

0.8 |

0 |

对于30、60、70、80、90Kbps数据率的分频时由于计数值的舍入会产生的误差小于0.8%,符合题目要求。

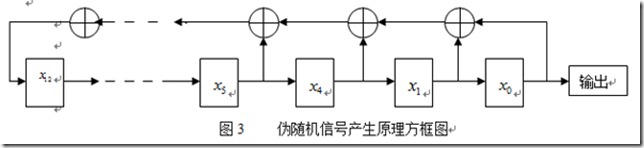

2.3 伪随机序列产生的分析

2.3.1 伪随机信号

伪随机序列发生器的VHDL实现。CLK为时钟脉冲,RESET为清零信号,OE为输出使能端,当RESET和OE都为高电平时,序列跟随着CLK的节拍一位一位的从DOUT端输出。除此之外,该伪随机序列发生器最大的特点在于,他能根据SEL端的选择信号产生不同长度的m序列。基本能够满足各种情况对不同长度伪随机信号的需要。 根据伪随机序列产生的原理,采用行为描述方式用VHDL语言对该逻辑进行硬件描述。

图3 伪随机信号产生原理方框图

2.4 曼彻斯特编码的分析

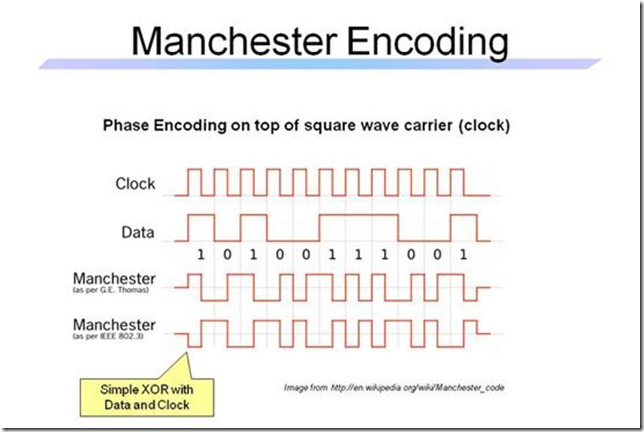

曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,曼彻斯特编码的解释为:从低电平到高电平的转换表示 1,从高电平到低电平的转换表示0。原理图4所示。

图4 曼彻斯特编码原理图

2.5 同步信号提取的分析

2.5.1 同步信号提取方框图

2.5.1 同步信号提取方框图

图5 同步信号提取方框图

2.5.2 同步信号提取原理分析

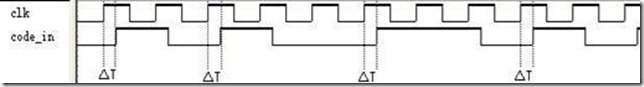

从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部数据流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非是超前和滞后两种情况,如图5、6所示,从数据流上跳沿的角度来看,若将数据流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明数据流滞后于本地时钟,若为“0”则说明数据流超前于本地时钟。

|

图6 数据流滞后于本地时钟△T

图7 数据流超前于本地时钟△T

根据以上原理,本设计中的鉴相器作用是鉴别出数据流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。控制计数器的计数输出用来控制相位调整选择模块的选择端。 相位调整选择模块由相位调整和相位选择功能。

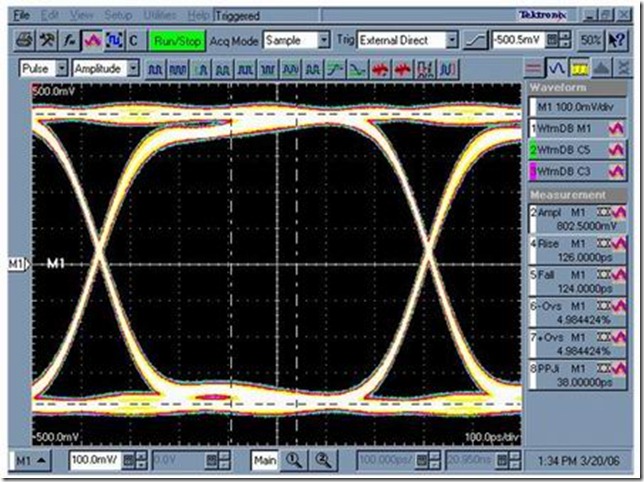

2.6 眼图显示的分析

2.6.1 眼图

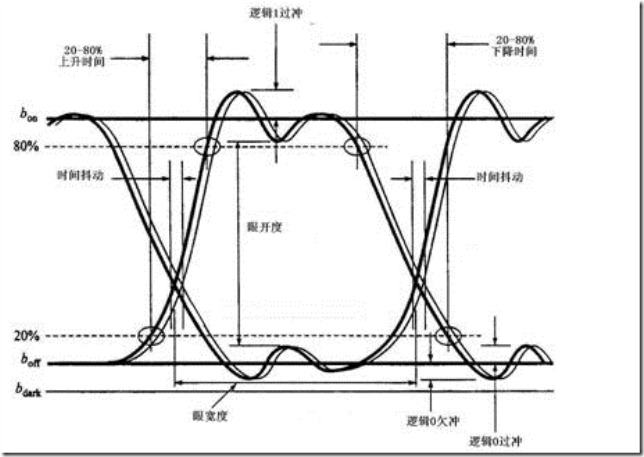

眼图的成因:由于示波器的余辉作用,扫描所得的每一个码元波形将重叠在一起,从而形成眼图。

眼图是指利用实验的方法估计和改善(通过调整)传输系统性能时在示波器上观察到的一种图形。观察眼图的方法是:用一个示波器跨接在接收滤波器的输出端,然后调整示波器扫描周期,使示波器水平扫描周期与接收码元的周期同步,这时示波器屏幕上看到的图形像人的眼睛,故称为眼图。

2.6.2 眼图的分析

从眼图上可以观察出码间串扰和噪声的影响,从而估计系统优劣程度。另外也可以用此图形对接收滤波器的特性加以调整,以减小码间串扰和改善系统的传输性能

接收信号的最佳取样时间是纵向眼开度最大的时刻t1。理想情况下V2- V1=0,纵向眼开度为1。由横向眼开度确定的时间宽度定义了不会由于码间干扰产生误码的时间范围Δt。眼开度受噪声和码间干扰的影响,从眼图的张开度可以估计出码间干扰的大小,判决时刻过门限失真量的大小以及定时抖动等。

图8 3比特非归零码的8种组合

图9 8种组合同时叠加形成的眼图

图10 简化的眼图

数字信号系统的幅度噪声会使眼开度减小,纵向眼开度的高度Ymax与最大信号电平V2定义了最大的幅度畸变。眼闭合度越大(纵向眼开度越小),说明正确判断信号中“1”与“0”越困难。在最佳取样时间t1处的眼开度的大小定义了系统的噪声容限。

取样时间改变时,眼图边线的斜率定义了系统时间误差的灵敏度:当斜率较小时,时间误差的概率增加。在光纤系统中由于接收机噪声和光纤的脉冲畸变,会产生时间抖动。如果取样时间正好在信号电平与判断阈值水平相交的时刻的中点,则判断阈值电平处失真量ΔT表示了时间抖动大小,用百分率表示为:

式中Tb是一个比特的时间间隔。

用示波器对伪随机数字序列进行观察时,示波器的扫描周期应取为Tb或Tb的整数倍,即扫描频率取为1/Tb或1/NTb 。当示波器扫描频率和信号速率的比改变时,并列的眼睛可以多些或少些。当扫描周期为Tb时,示波器的扫描图形与一只人眼相似,当扫描周期取为NTb时,并列的眼睛为N个。

。

3电路与程序设计

3.1电路的设计

3.1.1系统总体框图

系统总体框图如图5所示

图11 系统总体框图NWX8899

3.1.2 m序列产生子系统框图与电路原理图

1、m序列产生子系统框图

|

图12 m序列产生子系统框图

2、m序列产生子系统电路

图10 m序列产生子系统电路

3.1.3 滤波子系统框图与电路原理图

1、3路滤波子系统电路

图11 滤波子系统电路

3.1.4 幅值调节子系统电路

图9 100mV幅值调节子系统电路

3.1.5 加法器子系统电路

图10 加法器子系统电路

3.1.6 滤噪子系统电路

图11 滤噪子系统电路

3.2程序的设计

3.2.1程序功能描述与设计思路

1、程序功能描述

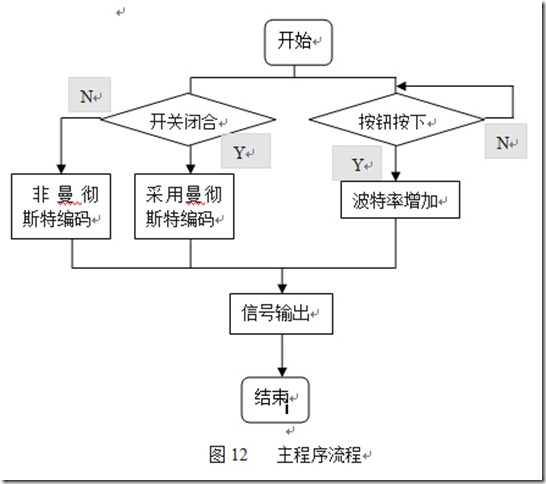

根据题目要求软件部分主要实现产生步进可调的m序列(包括采用曼彻斯特编码)。

2、程序设计思路

1)通过开关控制单片机选择是否采用曼彻斯特编码。

2)通过按钮控制单片机产生不同波特率的m序列,并用12864同步显示。

3.2.2程序流程图

1、主程序流程图

|

|

图12 主程序流程

2、数字分析电路流程图

图13 数字分析电路流程图

4测试方案与测试结果

4.1测试方案

1、软件仿真测试

3、硬件软件联调

经检查测试硬件电路完整,联调成功。

4.2 测试条件与仪器

测试条件:检查多次,仿真电路和硬件电路必须与系统原理图完全相同,并且检查无误,硬件电路保证无虚焊。

测试仪器:高精度数字示波器,数字万用表。

4.3 测试结果及分析

4.3.1测试结果(数据)

表2:测得三个滤波器的截止频率f误差

|

输入频率(KHz) |

10 |

80 |

90 |

100 |

110 |

130 |

180 |

200 |

|

输出幅度(V) |

1.00 |

0.92 |

0.82 |

0.75 |

0.55 |

0.5 |

0.45 |

0.43 |

误差分析:![]() =0.707f0观察上述表格可知,输入截止频率在95K处其输出幅度也是0.707V,故其截止频率误差为

=0.707f0观察上述表格可知,输入截止频率在95K处其输出幅度也是0.707V,故其截止频率误差为![]() %=5%符合题目中绝对误差不大于10%的要求。

%=5%符合题目中绝对误差不大于10%的要求。

同理可测得,截止频率位200K,500K使得绝对误差均符合题目的要求。

附录1:电路原理图

附录2:源程序

1. 主控制系统程序

#include <AT89X52.h>

#include <intrins.h>

sbit sj=P1^0;

sbit man=P1^1;

sbit mman=P1^2;

sbit rs=P1^4;

sbit rw=P1^5;

sbit e=P1^6;

#define uchar unsigned char

#define uint unsigned int

uchar code addr_tab[]={

0x80,0x81,0x82,0x83,0x84,0x85,0x86,0x87,//第一行汉字位 置

0x90,0x91,0x92,0x93,0x94,0x95,0x96,0x97,//第二行汉字位置

0x88,0x89,0x8a,0x8b,0x8c,0x8d,0x8e,0x8f,//第三行汉字位置

0x98,0x99,0x9a,0x9b,0x9c,0x9d,0x9e,0x9f,//第四行汉字位置

};

uint csj;

uint cmman;

uchar code shuju[10][10]={": 10kbps",": 20kbps",": 30kbps",": 40kbps",": 50kbps",

": 60kbps",": 70kbps",": 80kbps",": 90kbps",":100kbps",} ;

//uchar code jzplc[3][10]={": 100khz",": 200khz",": 500khz"} ;

//延时约2us

void delayus()

{

_nop_();

_nop_();

}

//延时 a * 1ms

void delayms(uint a)

{

uint i, j;

for(i = a; i > 0; i--)

for(j = 100; j > 0; j--);

}

void write_12864com(uchar com)

{

rs=0;

rw=0;

e=0;

delayus();

P0=com;

delayus();

delayus();

e=1;

delayus();

delayus();

e=0;

}

void write_12864dat(uchar dat)

{

rs=1;

rw=0;

e=0;

delayus();

P0=dat;

delayus();

delayus();

e=1;

delayus();

delayus();

e=0;

}

void display(uchar x,uchar y,uchar *s)

{

write_12864com(addr_tab[8*x+y]);

while(*s >0)

{

write_12864dat(*s); //写数据

s++;

}

}

void init(void)

{

write_12864com(0x38);

delayms(10);

write_12864com(0x0c);

delayms(10);

write_12864com(0x06);

delayms(10);

write_12864com(0x01);

delayms(10);

}

void scanf()

{

if(sj==0)

{

delayms(50);

if(sj==0)

{if(csj>8)

csj=0;

else

csj++;

}

while(!sj);

delayms(50);

while(!sj);

}

if(man==0)

{delayms(50);

if(man==0)

{ if(mman==0)

mman=1;

else

mman=0;

}

while(!man);

delayms(50);

while(!man);

}

/*if(dj==0)

{

delayms(50);

if(dj==0)

{if(cdj>9)

cdj=1;

else

cdj++;

}

while(!dj);

delayms(50);

while(!dj);

} */

}

void main()

{ csj=0;

P2=0x00;

// cjzpl=0;

mman=0;

init();

display(0,2,"E 分析仪");

display(1,0,"数据率");

display(2,0,"峰峰值");

//display(3,0,"截止频率");

while(1)

{

scanf();

display(1,4,*shuju+10*csj);

//display(3,4,*jzplc+10*cjzpl);

if(mman)

display(3,0," Manchester");

else

display(3,0,"非manchester");

P2=0x00+csj+1;

}

}

2. 数字信号产生程序

//mcu_interface//

library IEEE;

use IEEE.Std_logic_1164.all;

entity mcu_interface is

port(mcu_data : in std_logic_vector(7 downto 0);

wr : in std_logic;

count : out integer range 0 to 511);

end mcu_interface ;

architecture mcu_interface_arch of mcu_interface is

begin

with mcu_data select

count <= 500 when "00000001", --1 10k

250 when "00000010", --2 20k

167 when "00000011", --3 30k

125 when "00000100", --4 40k

100 when "00000101", --5 50k

83 when "00000110", --6 60k

71 when "00000111", --7 70k

62 when "00001000", --8 80k

56 when "00001001", --9 90k

50 when "00001010", --10 100k

500 when others;

end mcu_interface_arch ;

//f_freq//

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity f_freq is

port( count : in std_logic_vector(8 downto 0);

f_in : in std_logic;

f_out : out std_logic);

end f_freq;

architecture behav of f_freq is

signal f : std_logic;

signal count1 : std_logic_vector(8 downto 0);

--signal count1 : integer range 0 to 4294967295;

begin

process(f_in)

begin

if f_in='1' and f_in'event then

if count1<(count-1) then

count1<=count1+1;

else count1<="000000000";

f<=not f;

end if;

end if;

f_out<=f;

end process;

end behav;