【再说FPGA】ALTERA ECO使用问题

0赞

发表于 1/24/2013 2:45:01 PM

阅读(7614)

Altera的QuartusII软件支持用户手动修改设计,一般在设计调试阶段需要更改很小部分的时候可以利用QII里的工具ECO来进行手动修改,修改后不需要进行全编译。

笔者在进行基于FPGA的TDC设计时,利用ECO更改PLL以及ALM,大大方便了TDC在调试阶段设计更改。不过最近遇到一个关于ECO的小问题,虽然没有阻碍整个项目设计的进程,但是没有弄明白,记录与此。

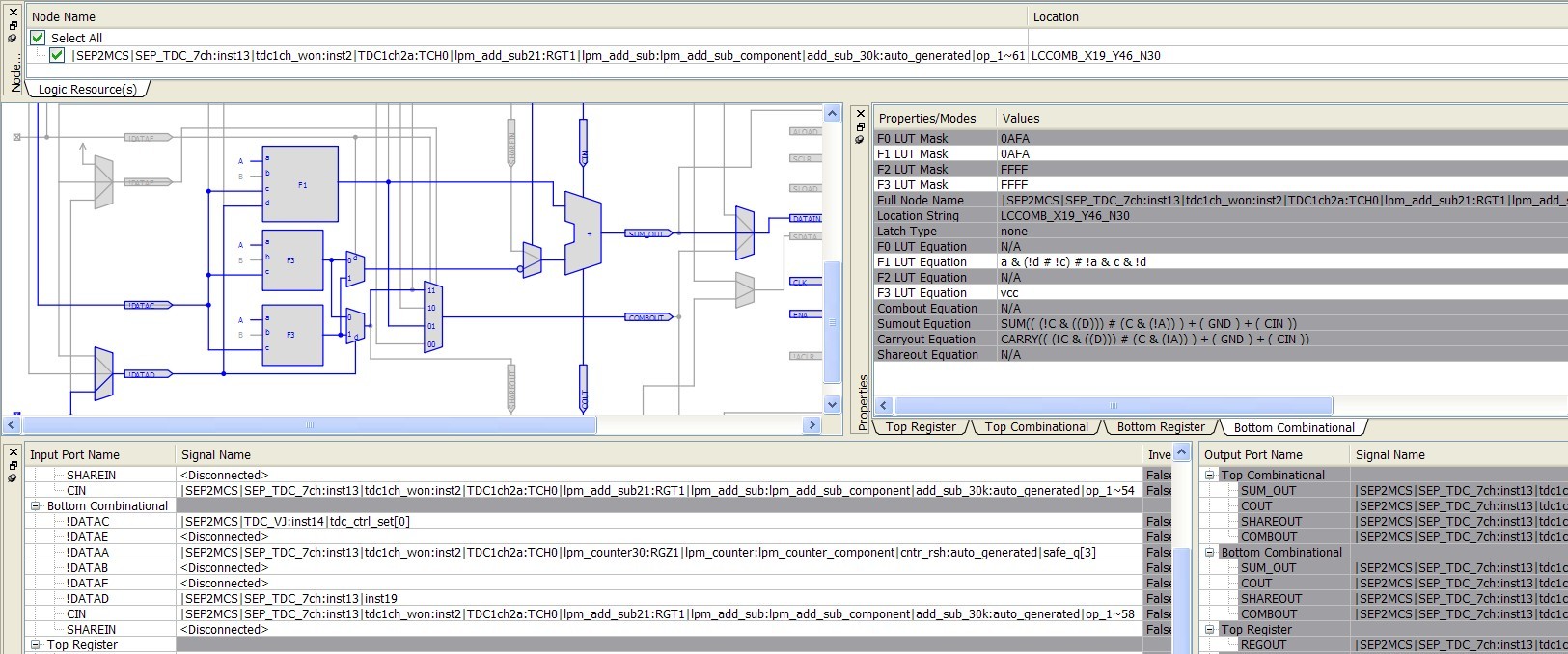

如下图所示,如果将ALUT数据输入端口DATAD的输入信号(*:inst13|inst19)改接到DATAF上,那么F1 LUT Equation应该怎么修改才能保证逻辑功能不变呢?

即:我只是修改某个信号feed进ALUT的路径,但不改变实际逻辑功能。

图1:ALM属性编辑器

其实我的问题是当DATAD端口上的信号转移到DATAF上以后(注意:转移以后需要删除端口DATAD上的信号),如何修改上图右侧的F1 LUT的掩码或者F1 LUT等式(这二者修改一个相互自动更新另一个)才能是原来的逻辑功能不发生改变。

我们知道上述图1中Carryout等式为:“CARRY(((!C&((D)))#(C&(!A)))+(GND)+(CIN))”,

那么经过ECO修改后,该等式应该为:“CARRY(((!C&((F)))#(C&(!A)))+(GND)+(CIN))”,即D被

F替换。因为只有这样才能保证逻辑功能不发生改变。

而ECO不支持直接修改Carryout等式,所以必须通过修改LUT掩码或者LUT等式来间接达到上述目的。这就是我的问题所在。

其实上述问题还比较简单,经过尝试只需将F1

LUT等式中的“!D”改成“D”,那么SUMOUT和CARRYOUT等式就会自动将其中的“D”更换成“F”。因为LUT等式中的“D”是对应

Carryout等式中“F”,如图2所示,而LUT等式中的“!D”对应Carryout等式中的“!F”,如图3所示,F2

LUT等式中的D对应Carryout等式中的F。

图2:LUT等式中“D”对应Carryout等式中的“F”

图3:LUT等式中“!D”对应Carryout等式中的“!F”

而更复杂的应用是ALUT的输入端口上,DATAF和DATAD上都有信号,也即Carryout和sumout等式中同时包含D/!D和F/!F时LUT等式应该如何表示?或者可能这种情况是不是不存在,即不支持?!!!