【红色飓风Nano二代测评】Xilinx DCM PLL输出时钟的ODD2法则

0赞Xilinx DCM PLL输出时钟的ODD2法则

—CrazyBingo

—20140507

一个具有MCB接口的Spartan,不搞图像,怎么能够承受。。。。

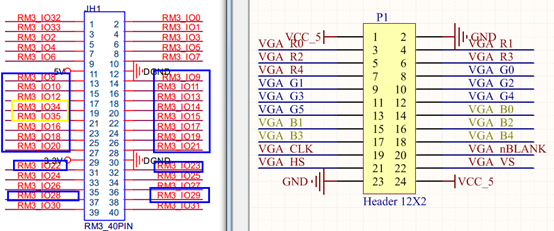

一个准备做FPGA视频图像算法的CB,不搞摄像头,不要VGA显示怎么承受的了呢。。。由于Nano2没有VGA接口,蛋疼的很,幸亏当年做过一个RGB565的VGA模块。。。。不知道可不可以拿来直接用。。。。

我擦,。。Nano2的接口竟然跟Terasic的接口一模一样。。。这个很有爱。。不过我的VGA口。。如下所示:

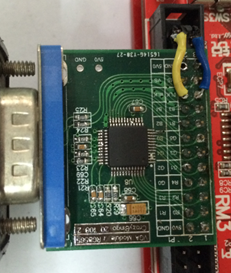

于是死磕。。NND VGA_CLK与VGA_nBlank用2根跳线,搞定。。。蛋疼了弄错了路次。。用疯抢吹了3次。。最后终于焊接好了,如下:

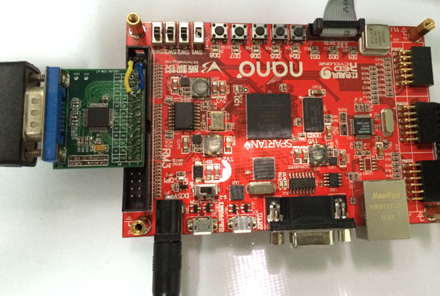

最后连接的图,如下所示,呵呵 开工:

话说玩了5年VGA,写过无数VGA开发的博客。。。这方面简直都没啥特别的感觉了,所以就不多说了。。直接移植VGA驱动电路。。PLL为25MHz时钟输出。。开开心心的点编译,结果崩溃了,。。。。

由于ADV7123需要一个DCLK时钟,而这里DCLK直接由PLL输出,因此原先本人这样描述,在Altera FPGA中完全没有问题:

assign lcd_dclk = ~clk;

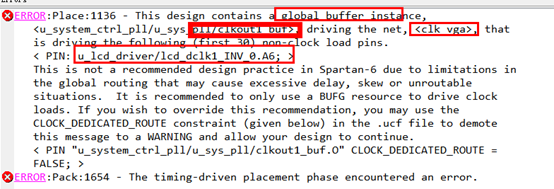

但是崩溃的是,在Xilinx的FPGA中,这样行不通,错误警告如下图所示:

意思就是说从PLL的Buffer输出的时钟,不能直接输出到外部。。由于VGA的lcd_dclk是直接输出到外部的。。。。。而引脚直接输出PLL输出的时钟,并不是Spartan-6的推荐设计,由于全局布线的局限,这将会过多的延迟,抖动,甚至无法布线的情况。推荐只用一个BUFG源来驱动时钟。如果你想推荐这个推荐,你得使用CLOCK_DEDICATED_ROUTE约束来将警告将至,持续设计。

一般不推荐直接从PLL输出时钟到PIN。但必须这样做,也有解决方案,只有将PLL输出时钟定义为非全局时钟,或者通过ODDR2方式输出。但如果该时钟必须为全局时钟,那只能通过PLL→BUFG→ODDR2→OBUF的模式。且不管这种方式的优劣,先解决问题。

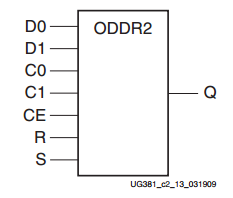

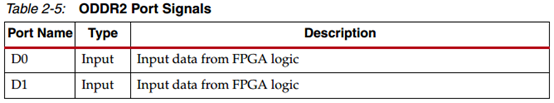

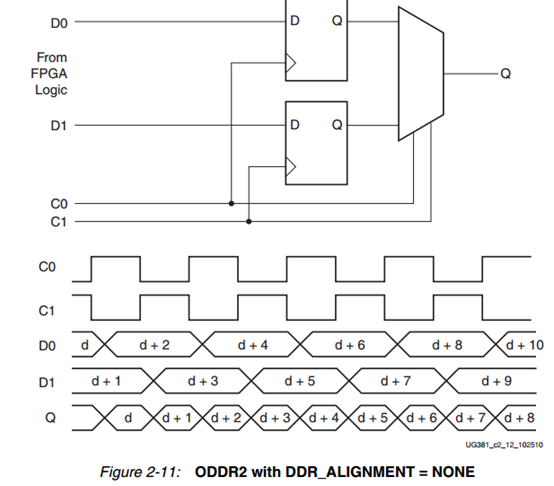

与ODDR2类似的是IDDR2,前者将差分转成单端,后者将单端转成差分。ODDR2的接口,如下所示:

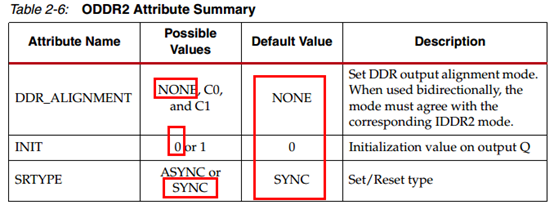

其中C0、C1为输入的,相位差为180度的信号,D0、D1为输入的2个数据。。CE为时钟使能,R/S为模式,。。Q为最终的输出。模式的配置如下所示:

这里,我们采用默认的模式,此时的波形图如下所示:

这里我们将D0输入1,D1输入0。由于在C0上升沿读取D0为1,在C1上升沿读取D1为0,因此输出将于C0同步的一个时钟。。例化的ODDR2原语,如下所示:

//-----------------------------------

//Output the clock via ODDR2

//LCELL LCELL(.in(clk),.out(lcd_dclk));

assign lcd_dclk = ~clk;

ODDR2

#(

.DDR_ALIGNMENT ("NONE"),

.INIT (1'b0),

.SRTYPE ("SYNC")

)

u_ODDR2

(

.C0 (clk),

.C1 (~clk),

.Q (lcd_dclk),

.CE (1'b1),

.D0 (1'b1),

.D1 (1'b0),

.R (1'b0),

.S (1'b0)

);

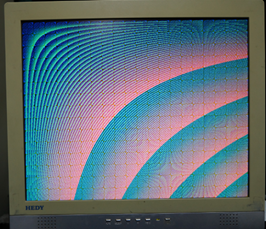

这样,就是先了lcd_dclk时钟的输出,实质上它将与clk,即C0输入一样。当然由于DFF不可避免的几ns延时,这个是木有办法的。。。。但至少,再次编译后OK了,Nano2 VGA驱动搞定,甚至移植到1280*1024,很happy的搞定了哈哈,给出640*480 与1280*1024的驱动,如下所示:

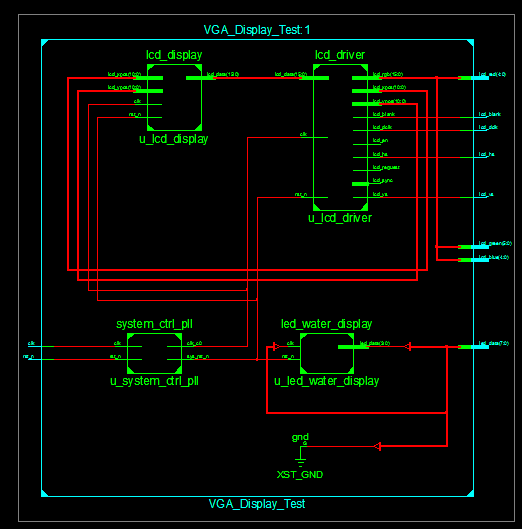

再回去看下RTL图,如下:

这里system_ctrl_pll为全局时钟控制模块、lcd_display为VGA显示模块、lcd_driver为VGA驱动模块,而lcd_water_display仅仅是LED的测试模块!ISEd RTL图看来来,视觉体验跟Quartus II的完全不一样 呵呵。。还没习惯,但至少还挺爽的 呵呵。。加油。、。

最后,分析一下PLL→BUFG→ODDR2→OBUF模式时钟输出的好坏。。。

(1) 因为ODDR2需要额外180度相位的clock,因此timing performance会受影响。

(2) 由于时序、组合逻辑将不可避免的延时,产生ns级别的相位差。

但是,如果PLL输出的引脚在当前PLL的时钟域,据说是可以直接将PLL输出到该IO的。关于clock region与pin 可以在PlanAhead中查看。

但如果这个时钟必须为全局时钟,又不能通过ODDR2方式输出,同时这个PLL还跟IO不在同一个clock region的时候,怎么办呢。。。。。崩溃了