【连载2】VIP Mini开发板资料介绍

0赞

2. VIP Mini开发板资料介绍

本章开始,不打算吹太多的牛,使劲搂住,忍一忍,再忍一忍……

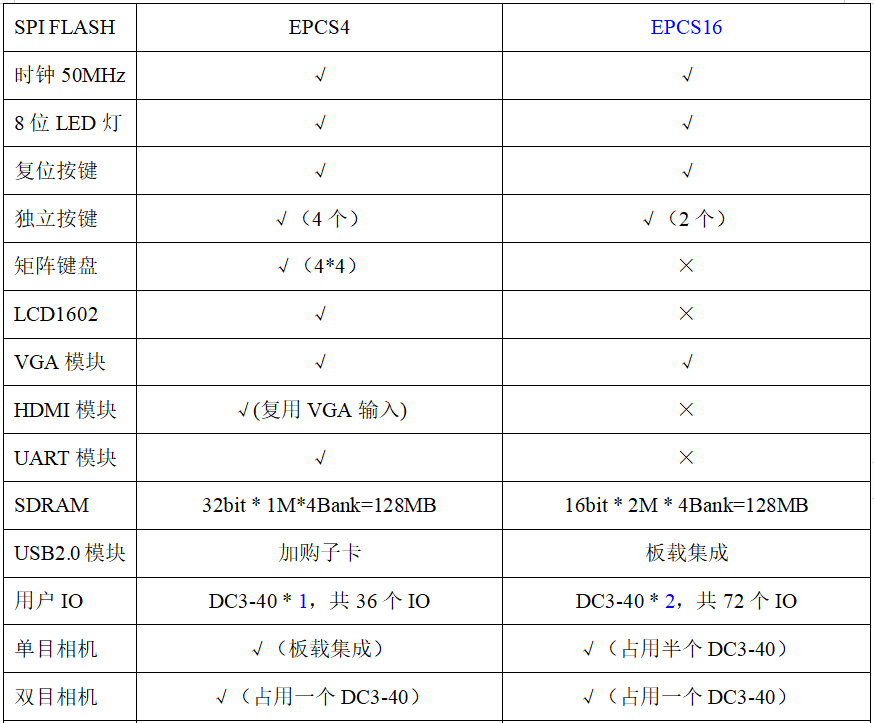

首先,开门见山地总结下,优化了那么多年,VIP Big和VIP Mini摄像头开发板的异同点是什么,FPGAer如何选择,简单的说,就是VIP Big适合从零开始入门,VIP Mini适合做图像处理并且接口丰富,但是两者都移植了我的所有图像算法,毕竟FPGA实现不依赖于平添。

然后还是努力用图表给大家对比一下这两者的性能参数,如下所示。谨记本教材的主角是右侧的:VIP Mini开发板,谢谢。

2.1. VIP Mini开发板套餐介绍

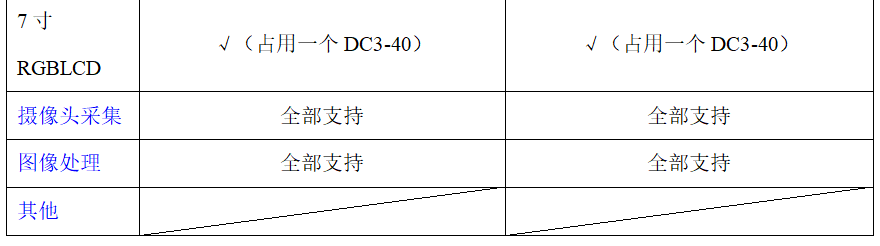

VIP Mini摄像头开发板主要包括了一个集成小梅哥的EP4CEE6 核心板(6可当作10用,一个Die),一根扁平的USB-Mini延长线,一个入门级别USB Blaster下载器,以及可选的OV7725/OV5640/MT9M001/MT9V034/AR0144等双目模组、7寸RGBLCD屏幕等。相关配置如下所示:

板卡安装好双目相机以及RGBLCD的效果图如下所示(以宽动态全局曝光的双目MT9V034为例):

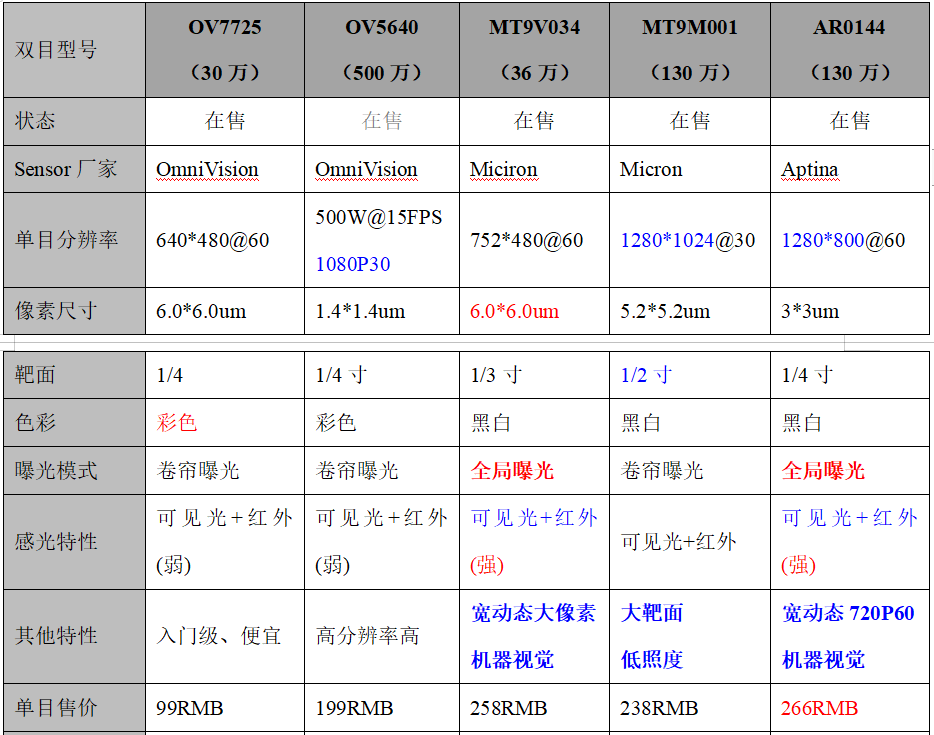

其中如上图所示,关于板卡配套可选的多款CMOS摄像头,均由CrazyBingo本人设计,其中关于这几块摄像头的选型参数对比,如下表格所示,用户可以按需所求,当然你如果是小白,不知道自己想要什么,那你可以默认标配或者等我有时间的时候回复您。

2.2. IP Mini开发板资料介绍

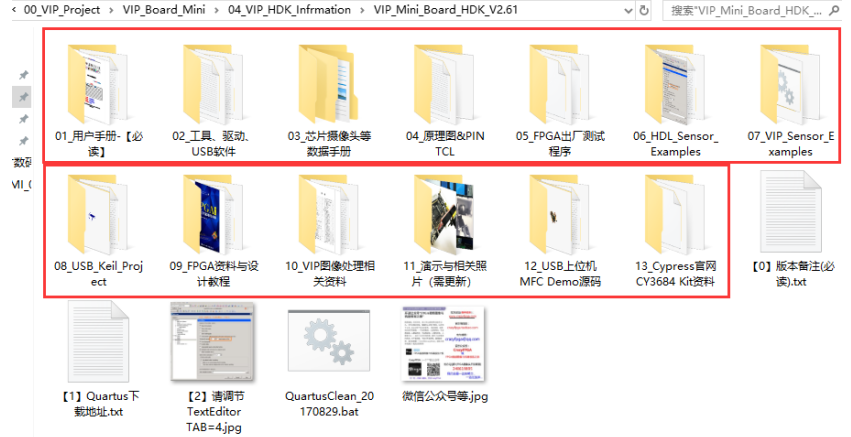

资料内容太丰富,跟板卡相关的无关的都有辣么多,不可能一一介绍。但是结构还是得说清楚,本开发板资料更新了几十个版本,目前基本上趋于成熟。当前最新版本2.61的文件结构,截屏如下所示:

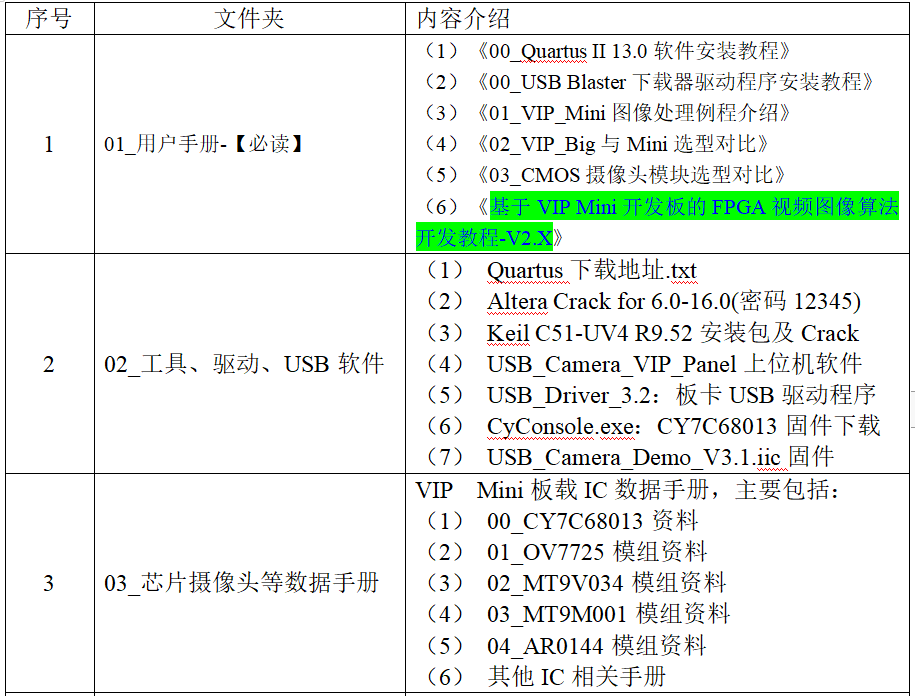

详细的介绍HDK(Hardware Develop Kit)资料包的文件目录,如下所示,其你给大家仔细阅读谢谢!

作为刚下载到VIP_Mini_Board_HDK_V2.X资料包的朋友,烦请仔细阅读01_用户手册,也即本手册的教程内容。巧妇难为无米之炊,仔细阅读完本手册的内容,势必能让你事半功倍的熟悉VIP Mini摄像头开发板,以至于在日后更加得心应手的进行开发(貌似你看到这里的时候,就是在阅读本文档了,多虑了哈哈)。

2.3. VIP Mini开发板例程介绍

申明:本开发板所有FPGA工程均在Quartus II 13.0下开发,为了避免出现一些不可预知的问题,推荐你安装13.0。由于我在图像处理算法部分(VIP)修改了软件生成的IP的宏定义内容,如果您非得用新版本,可得小心喽。

VIP Mini开发板的例程太丰富,但基本都是跟摄像头相关的例程,包括驱动/采集/显示/以及图像处理相关的几十个例程。

2.3.1. VIP_Mini基础外设例程

板载例程6个,涵盖除了基本外设的测试,如下:

2.3.2 . VIP_Mini摄像头开发例程

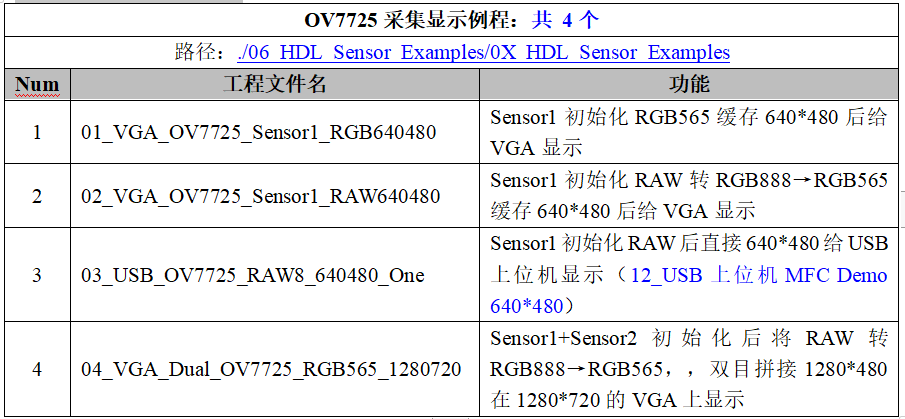

支持OV7725/MT9V034/MT9M001/AR0144等,这里以OV7725为例介绍例程规划,如下所示:

2.3.3. VIP Mini 7寸 RGBLCD开发例程

7寸RGBLCD,从GPIOB接入,支持OV7725/MT9V034/MT9M001/AR0144等相机,例程如下所示:

2.3.4. VIP_Mini图像处理例程

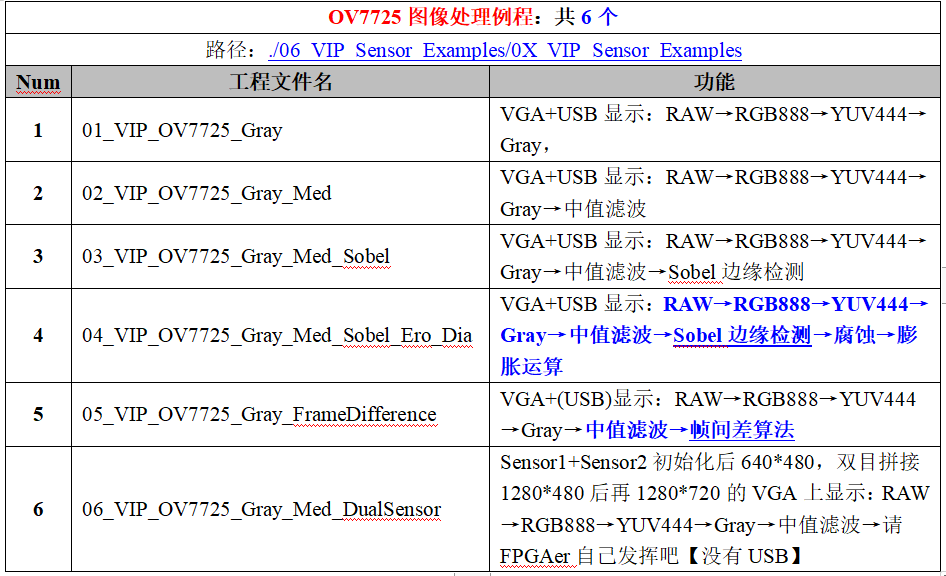

支持OV7725/MT9V034/MT9M001/AR0144等,这里以OV7725为例介绍例程规划:

特别注意:

(1)例程结构与OV7725整体类似;但其他摄像头,例如MT9V034裁剪到640*480进行显示处理,MT9M001/AR0144等支持1280*720分辨率的采集显示处理,双目分辨率分别拼接后720P与1080P中显示;

(2)彩色相机(OV7725/OV5640等)支持上表2的RAW2RGB例程,灰度相机(MT9V034 MT9M001 AR0144等)不需要去马赛色,直接灰度显示处理,因此没有RAW2RGB例程。

(3)提供了原始或处理后图像的VGA但双目显示,以及USB单目显示;USB双目显示由于担心影响到淘宝抄袭我的风气,暂时不开发/提供,请读者自己发挥,未来是你们的。

(4)FrameDifference实验中,由于MT9M001 AR0144等设置1280*720 VGA输出的相机,USB无法接受74.25MHz那么高的频率,因此如果要换成USB显示,则可以讲sys_pll2的74.25MHz修改为24Mhz即可(目前为了显示有图,接在了VIP之后的流了)。

2.4. VIP Mini开发板工程目录介绍

剪不断,理还乱,是离愁,别是一番滋味在心头。为了让你趁早认知Bingo的架构,这一节请读者必须好好看下!!!

FPGA工程设计中,包括了大量的代码,仿真测试,参考文档工程设置等内容,但是基本上都杂乱无章的放在了一起,绝对受不了看别人代码的时,那种莫名的痛苦了。所谓“人靠衣装,美靠亮装”,每一个完美主义者都无法承受杂乱无章的设计。因此一个Quartus II工程,也必须有一个完善的框架,来存放相应的资源、设计等,这在于方便自己查看的同时,也给团队内部人员移植、修改带来了极大的便利。当然这也没有确定的规定,由于灵活的设计,Bingo在此给出了自己多年来总结并且遵循的自成体系的框架,如下图所示:

每一个Quartus II的工程,被分为5个部分,一般dev自工程建立后不用再管,而core需要用户设计时注意将Quartus II IP核保存在这里。另外src是用户最需要关心的地方,每一个新建的Verilog HDL文件都被放在这里。Sim主要存放Modelsim仿真测试工程,也许一个工程中有好多个测试子模块,在sim里面继续分层。doc主要是关于设计的档案、参考等信息,这里作为版本修改、升级,以及团队合作必须要完善的部分。

当然类似的架构也可以利用在其他处理器的设计中,这里只是一个典型的应用于Quartus II的例子,实际上以上结构并不局限于Quartus II,你用ISE或者Vivado也一样。