【连载6.1】Board_Basic_Test例程

1赞

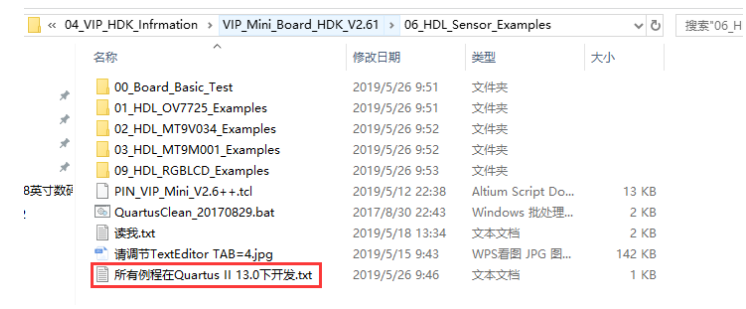

本章所有代码工程,均在../06_HDL_Logic_Examples目录下,请用户参照VIP Mini资料包,如下所示:

首先,VIP Mini的所有例程,均采用最经典的Quartus II 13.0,请安装当前版本,如果是其他版本,关于移植或者出现IP版本的问题,麻烦自行解决,谢谢(一般情况下直接用高版本编译综合也不会有问题,Altera对IP的延续性比Xilinx做的好)。

关于Qaurtus II安装教程,驱动的安装,以及仿真软件Modelsim的使用等,请参照本人写的《FPGA设计技巧与案例开发详解》一书,本教程不面向与初学者,在篇幅上不进行入门的阐述,谢谢!

本章主要介绍VIP Mini资料包的基本HDL例程,介绍架构以及接口功能,以及标配摄像头的采集显示等。

1.1. Board_Basic_Test例程

首先介绍资料提供的板卡基本接口测试例程,共有6个如下表所示:

(1) 00_KEY_595LED_Test:

板载PLL、复位按键、用户按键、基于74HC595的串转并8bit LED的测试,工程比较简单,但是代码非常成熟,请直接享用。

(2) 02-X_VGA_Display_Test_分辨率:

主要是不同分辨率的测试程序,包括了640*480@60,1280*720@50,1920*1080@60,这些分辨率在后续的摄像头采集工程中都用到了。关于分辨率主要修改的是lcd_para.v宏定义行场参数,以及分辨率匹配的扫描频率修改PLL,其他几乎都一样,由于比较简单,不展开讨论。

用户可以在lcd_display.v中修改宏定义,测试各类VGA显示图像,如下图所示:

(1)垂直彩条显示 (2)水平彩条显示 (3)分型图显示 (4)灰度渐变显示

(3) 03_SDRAM_VGA_Display_Test640480:

在VGA显示例程的基础上,增加了SDRAM控制器的驱动,从前端模拟数据,写入SDRAM,再从后端读取SDRAM数据,按照50/60给VGA刷新。这部分对于SDRAM的驱动开发非常重要,因为这事我们摄像头采集显示缓存的基础,也是后续做图像处理算法的缓存节制。

关于“不完全乒乓SDRAM控制器”的设计及使用,本人在《FPGA设计技巧与案例开发详解》一书中已经阐述的淋漓尽致,本教程就不再展开,老司机都不喜欢罗嗦,并且既然致力于搞算法,那这部分应该算是基础。