【连载7.2.2】RGB888转YCbCr的HDL实现

0赞新建并保存VIP_RGB888_YCbCr444.v 与src/Video_Image_Processor下,具体的算法的HDL实现过程如下:

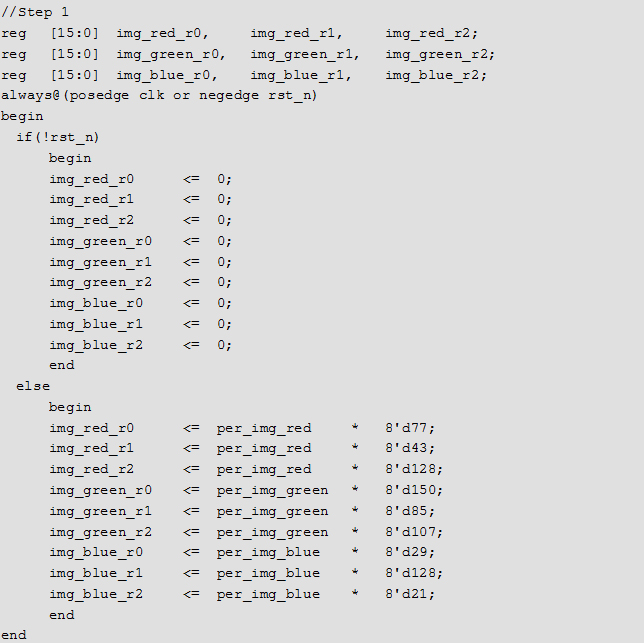

(1)第一步,分别计算出Y、Cb、Cr中每一个乘法的乘积,HDL如下:

(2)第二步,计算出Y、Cb、Cr括号内的值,HDL如下:

(3)第三步,右移8Bit。这里由于Step2计算结果为16Bit,因此提取高8Bit即可,HDL如下所示:

实际上从(1)~(3)的运算,均直接通过寄存器描述,没有考虑到行场有效信号等。但实际上的操作会有一个数据流上的先后顺序,同时(1)-(3)同时对连续数据进行处理,采用这种方式实现的硬件加速,我们称之为流水线设计技巧。在HDL-VIP中是一种非常重要而且常用的算法实现思维,是FPGA硬件加速的精髓之一。

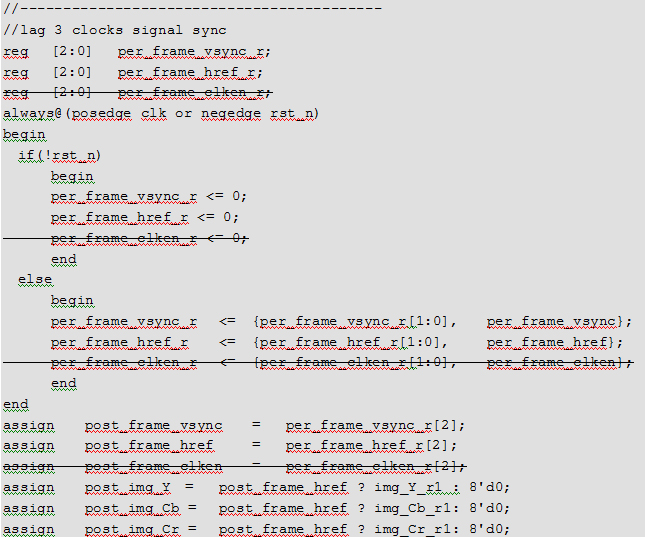

前面说过,VIP处理模块输入的数据接口时序,与输出完全一样。前面计算出Y、Cb、Cr我们消耗了(1)(2)(3)这三个时钟,因此需要将输入的行场信号、使能信号同步移动3个时钟,采用寄存器移位实现,代码所示:

此外,如上代码,输出的Y、Cb、Cr信号与输出的行有效信号进行了使能运算,保证了在post_frame_href无效时数据输出为0,吻合Bingo版的VIP时序约定。

至此,我们便简单的实现了RGB888转YCbCr444功能。由于这里Video_Image_Processor模块,我们只进行了RGB888转YCbCr功能,因此其Module信号列表与Video_Image_Processor完全保持一致(注意Y、Cb、Cr的定义)。Video_Image_Processor.v文件的列表与例化如下所示: