【原创】modelsim编译Xilinx器件库的另一种方法(节省时间)

0赞以前在用modelsim对Xilinx进行器件库编译时,我用的比较多的是直接在ISE中编译器件库,感觉很方便简单,就是编译时间有点长。自从前段时间,在自己电脑装MathType,360杀毒软件将它视为木马。我以为是360误报,直接将360安全卫士关闭了。后来,电脑上的软件一个接一个的出现问题,说是软件的某个文件被感染了。最后只能被迫重新装系统,装完后立刻装上ISE14.7,想着modelsim编译Xilinx器件库时间太久了,就不装了,先用ISE14.7自带的仿真工具ISIM。用了几天的ISIM,感觉实在不好用。这不,今天马上将modelsim10.2给装上了。也尝试了另外一种编译Xilinx器件库的方法,发现该方法好像编译时间更快了,全部编译完后,20分钟还不到。以前在ISE中直接编译大概需要半个小时到一个小时之间,不知道是不是错觉哈。现在,介绍下该编译器件库的方法。

(1)在开始菜单找到Xilinx Design Tools--->ISE Design Suite 14.7--->EDK--->Tools--->Compile Simulation Libraries,单击,如下所示:

(2)由于电脑上装的modelsim是SE版本的,故在选择仿真器那里选择ModelSim SE;此外,还要在下面选择modelsim执行文件的路径,其他参数默认,单击Next,如下所示:

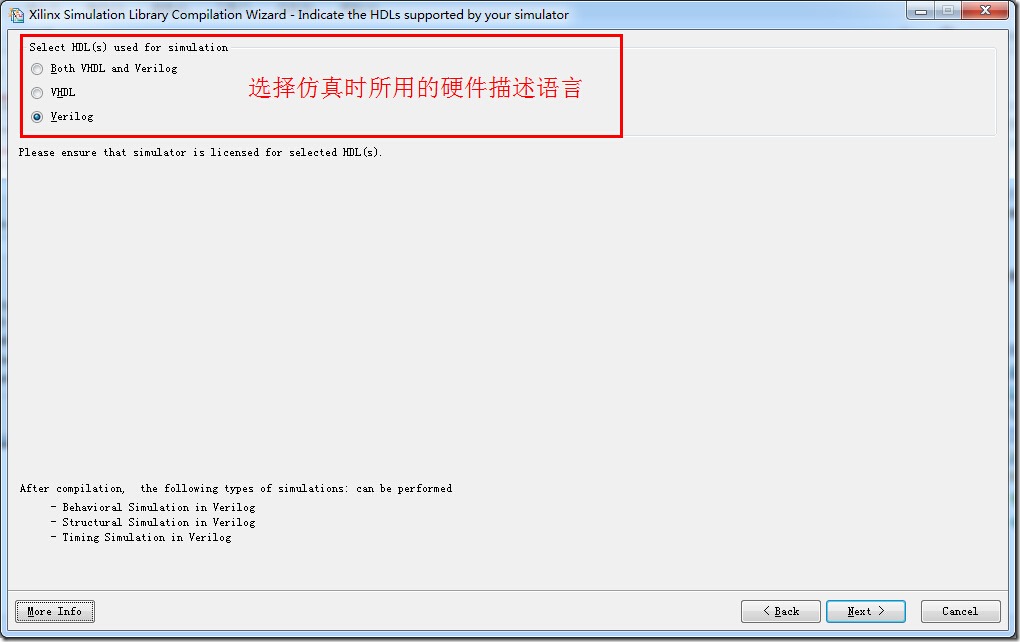

(3)在硬件描述语言中,由于我只学过Verilog HDL,也只用Verilog HDL进行设计和仿真,故在为仿真选择硬件描述语言时选择Verilog,Next,如下所示:

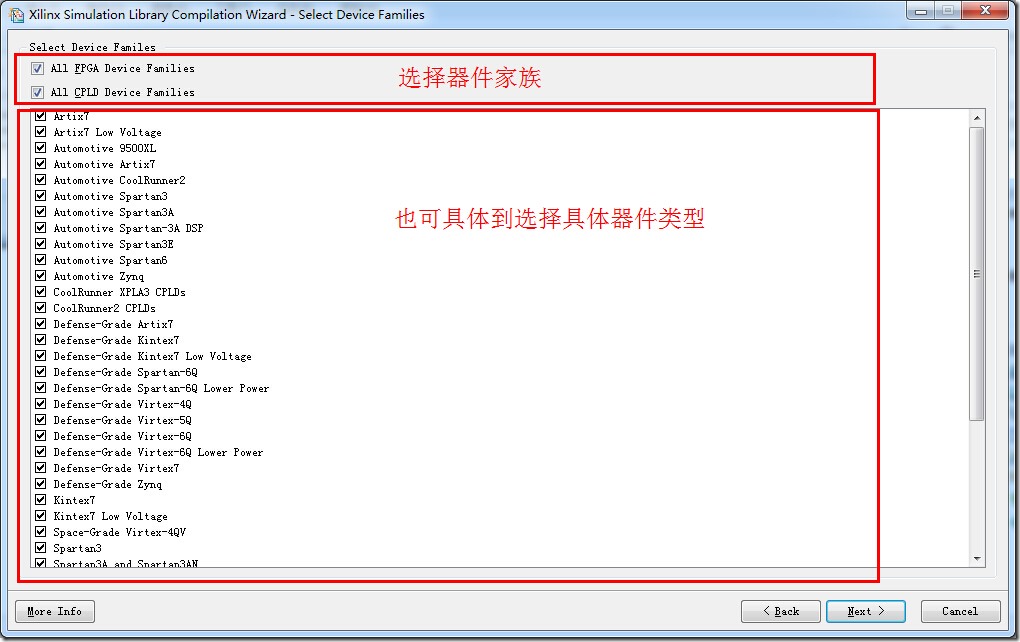

(4)这一步是选择要进行编译的器件库,可根据自己需求进行选择,这里就全选了,Next,如下所示:

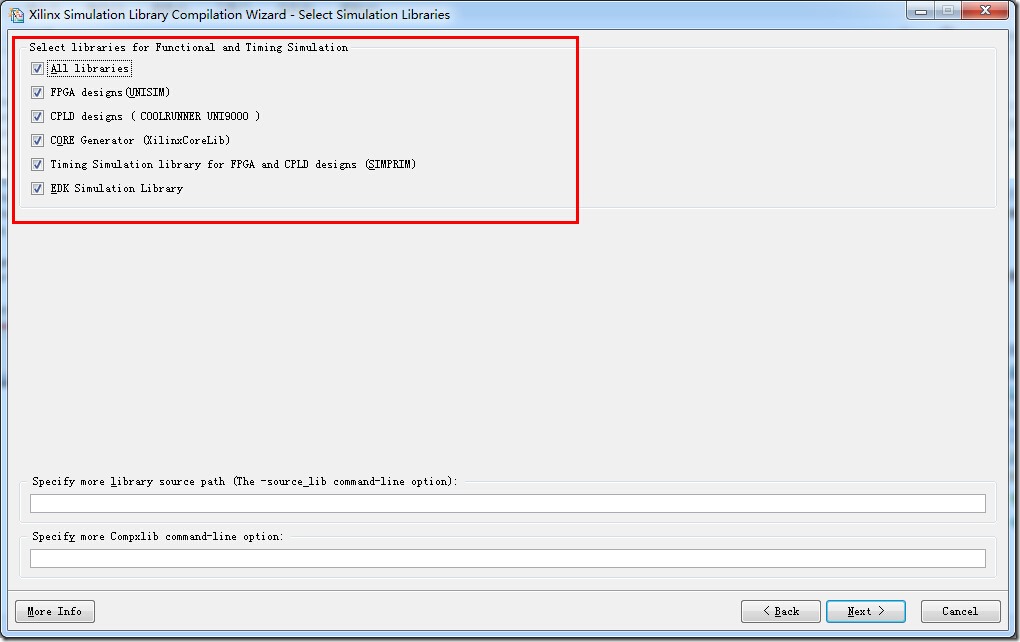

(5)为功能仿真和时序仿真选择库,这里把能选的都选上吧,其他两个空不用管,直接Next,如下所示:

(6)为生成的器件库选择存放的路径,这里在modelsim安装目录下新建xilinx_lib文件夹,并在下面的路径中指向这个文件夹,后面编译的器件库就放在这里了;其他参数默认;直接Launch Compile Process开始库的编译,如下所示:

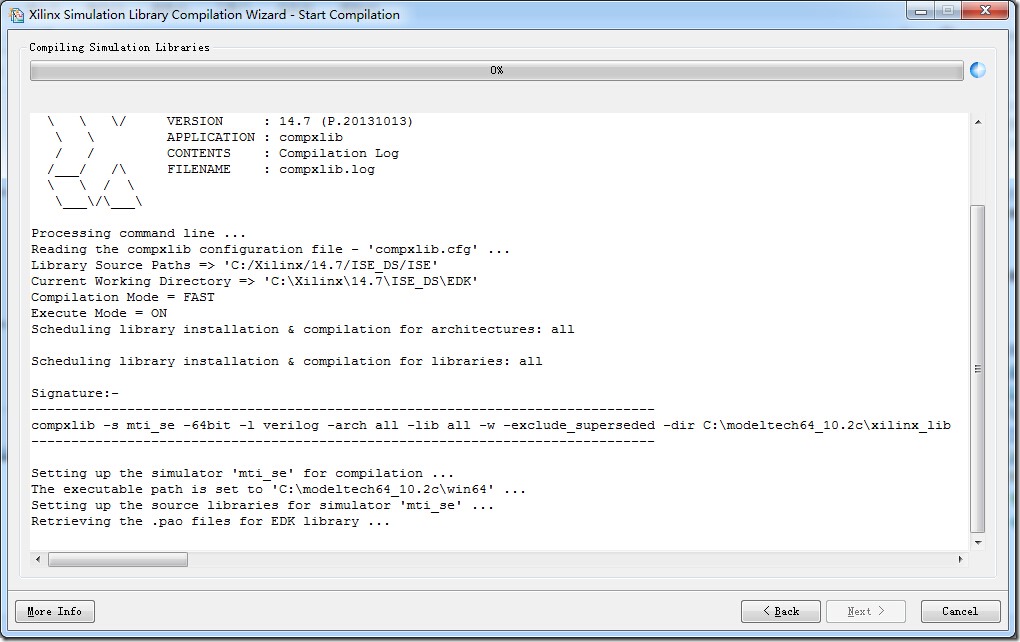

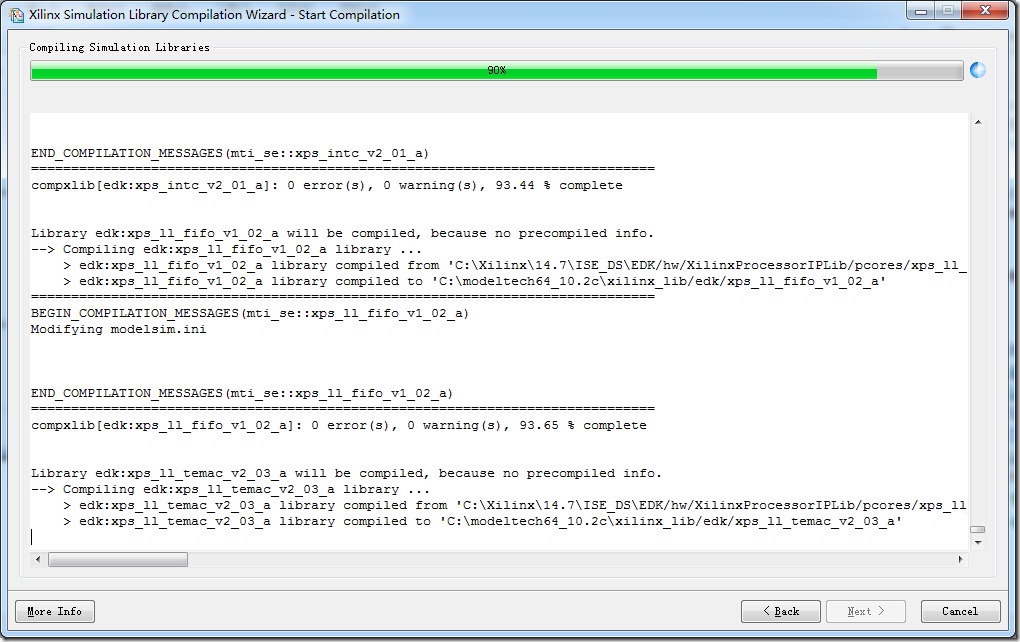

(7)正在编译库中,如下所示。。。统计了一下时间,从开始编译到编译完成总共花了16分钟,相比于直接在ISE中直接编译库快多了,太快了(我电脑是i3的,买了四年了)。

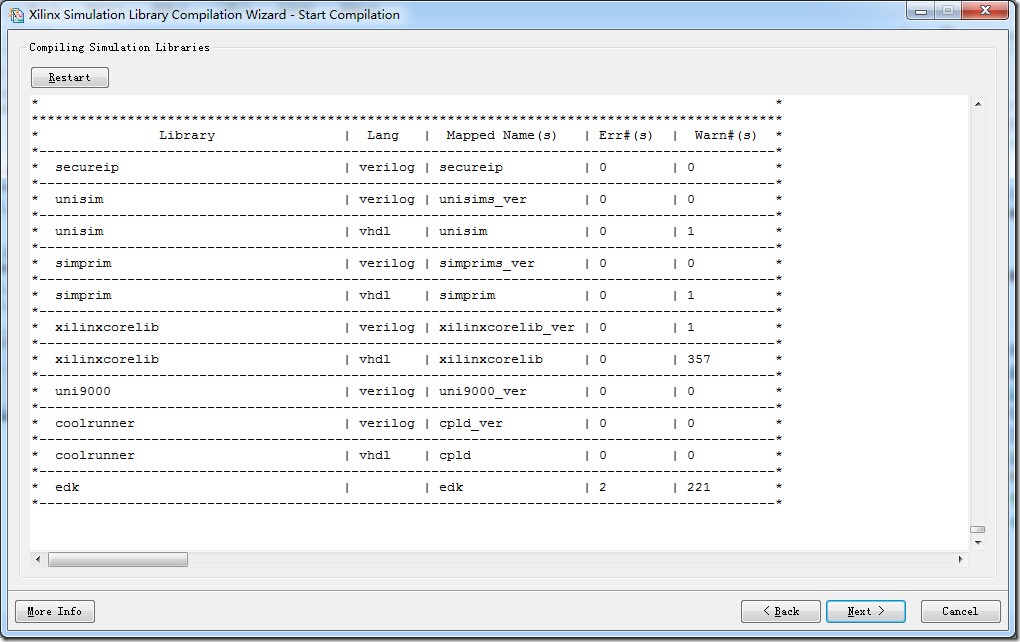

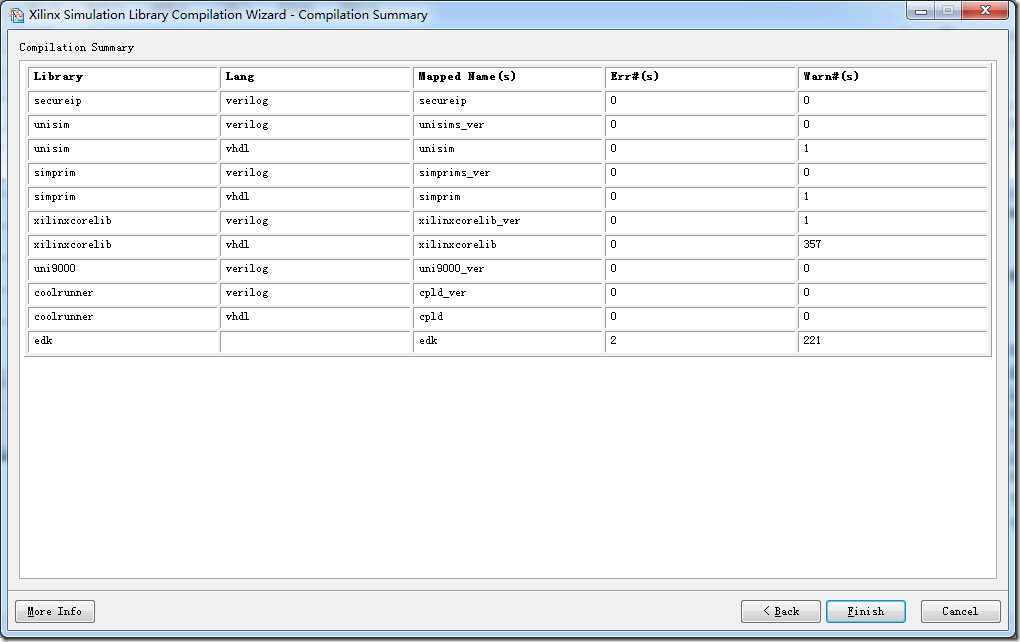

(8)器件库编译完成后,给出了下面的总结信息,可以看出哪个库编译出现了错误和警告。虽然在edk库的编译中出现2个错误,但没有关系,直接Next,然后finish。

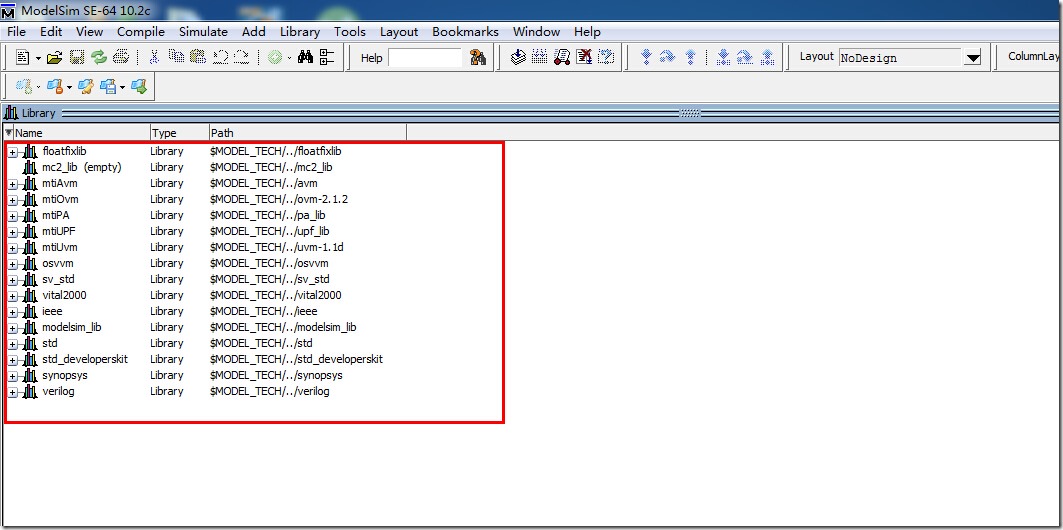

(9)但打开modelsim软件后并没有识别出刚刚编译好的器件库,如下所示:

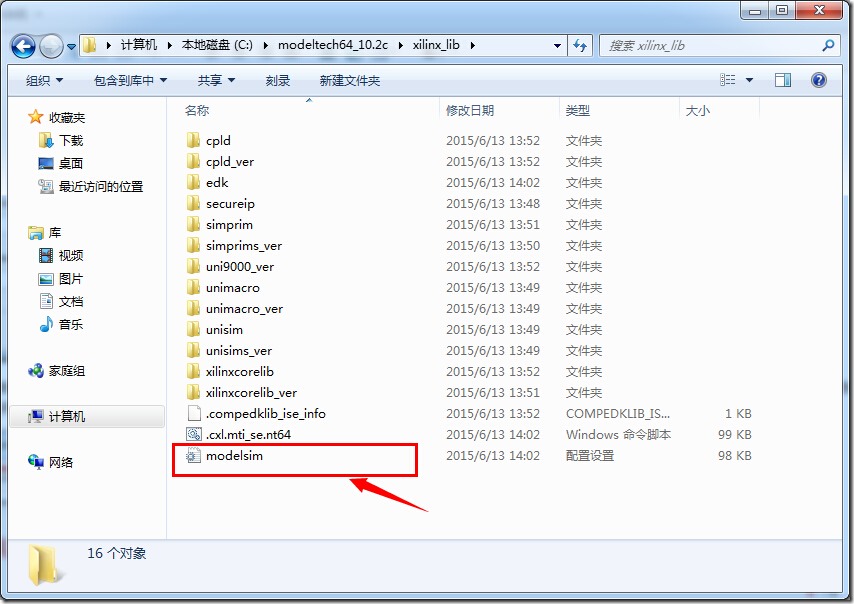

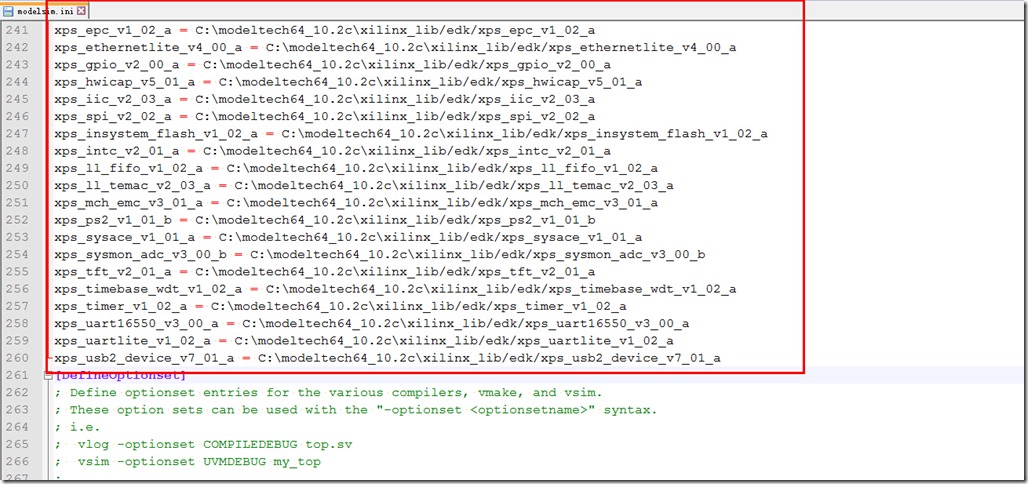

(10)为了使modelsim能够识别器件库,还要做一下处理。找到存放器件库路径的modelsim.ini文件并打开,将48行~260行的内容用CTRL+C复制到剪贴板中,如下所示:

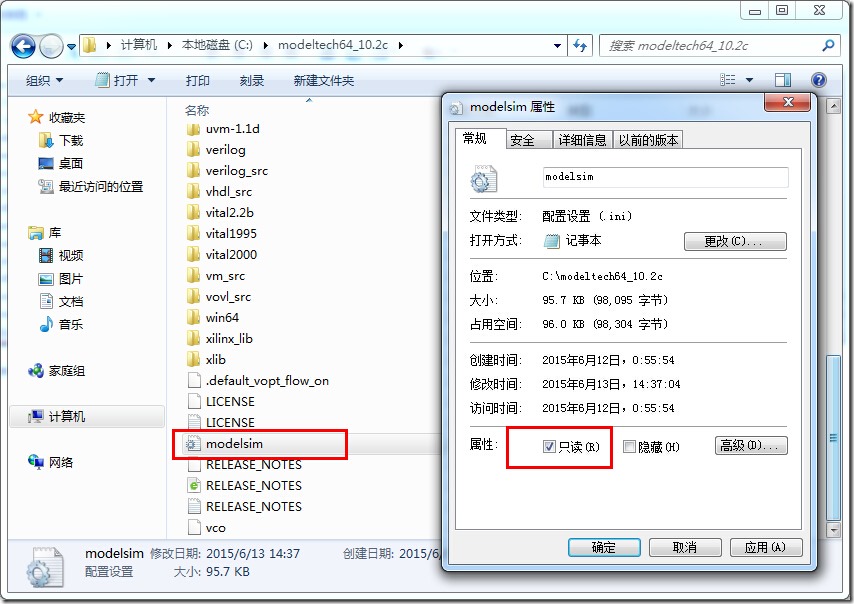

(11)然后再找到modelsim安装目录下自身的modelsim.ini文件,并去掉其只读属性(选中modelsim.ini文件,右键,属性),然后打开文件,将剪切板的内容复制到文件中去,接着关闭文件并将其只读属性勾上,如下所示:

(12)现在重新打开modelsim软件,发现器件库已经被识别了,如下所示:

至此,任务已完成!!!