【原创】第一次见到的Verilog HDL语法

0赞

发表于 7/19/2015 12:23:05 AM

阅读(7344)

最近在看代码的时候,不小心发现了在表示变量位宽范围时用到了+:、-:这样的符号。这种用法还是第一次见到的,也许是我太孤陋寡闻了。经过一番的查询,终于知道了它的用法和意义了。它的表示方法如下所示:

a[j+:k]; 或 a[j-:k];

其中,k必须是常数,代表位宽;j则是可变的,当用+:时,j作为变量的最低有效位,j+k-1作为变量的最高有效位,当用-:时,j作为变量的最高有效位,j-k+1作为变量的最低有效位。接下来,举个简单的例程来证明这个规则的正确性。假设有一个位宽为6的输入信号din,将它的每两位赋给位宽为2的输出变量即dout1=din[5:4]、dout2=din[3:2]、dout3=din[1:0]。

(1)对于[j+:k]这种情况的相应代码描述如下:

/**********************************************版权申明************************************************* ** 电子技术应用网站, CrazyBird ** http://www.chinaaet.com, http://blog.chinaaet.com/crazybird ** **--------------------------------------------文件信息-------------------------------------------------- ** 文件名: signal_test.v ** 创建者: CrazyBird ** 创建日期: 2015-7-18 ** 版本号: v1.0 ** 功能描述: 变量位宽表示中符号+:功能的验证 ** ********************************************************************************************************/ // synopsys translate_off `timescale 1 ns / 1 ps // synopsys translate_on module signal_test( rst_n, clk, din, dout1, dout2, dout3 ); //****************************************************************************** // 参数定义 //****************************************************************************** parameter DIN_WIDTH = 6; // 输入数据位宽 parameter DOUT_WIDTH = 2; // 输出数据位宽 parameter PAYLOAD_WIDTH = 2; // 加载数据位宽 //****************************************************************************** // 输入/输出端口声明 //****************************************************************************** input rst_n; input clk; input [DIN_WIDTH-1 :0] din; output reg [DOUT_WIDTH-1:0] dout1; output reg [DOUT_WIDTH-1:0] dout2; output reg [DOUT_WIDTH-1:0] dout3; //****************************************************************************** // 变量位宽表示中符号+:功能的验证 //****************************************************************************** always @(posedge clk or negedge rst_n) begin if(rst_n==1'b0) begin dout1 <= (0); dout2 <= (0); dout3 <= (0); end else begin dout1 <= din[0*PAYLOAD_WIDTH+:PAYLOAD_WIDTH]; dout2 <= din[1*PAYLOAD_WIDTH+:PAYLOAD_WIDTH]; dout3 <= din[2*PAYLOAD_WIDTH+:PAYLOAD_WIDTH]; end end //****************************************************************************** endmodule //*********************************************文件结束*****************************************************

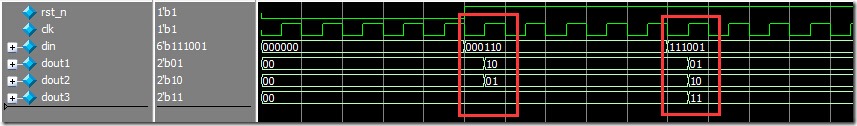

其modelsim仿真结果如下:

(2)对于[j-:k]这种情况的相应代码描述如下:

/**********************************************版权申明************************************************* ** 电子技术应用网站, CrazyBird ** http://www.chinaaet.com, http://blog.chinaaet.com/crazybird ** **--------------------------------------------文件信息-------------------------------------------------- ** 文件名: signal_test1.v ** 创建者: CrazyBird ** 创建日期: 2015-7-18 ** 版本号: v1.0 ** 功能描述: 变量位宽表示中符号-:功能的验证 ** ********************************************************************************************************/ // synopsys translate_off `timescale 1 ns / 1 ps // synopsys translate_on module signal_test1( rst_n, clk, din, dout1, dout2, dout3 ); //****************************************************************************** // 参数定义 //****************************************************************************** parameter DIN_WIDTH = 6; // 输入数据位宽 parameter DOUT_WIDTH = 2; // 输出数据位宽 parameter PAYLOAD_WIDTH = 2; // 加载数据位宽 //****************************************************************************** // 输入/输出端口声明 //****************************************************************************** input rst_n; input clk; input [DIN_WIDTH-1 :0] din; output reg [DOUT_WIDTH-1:0] dout1; output reg [DOUT_WIDTH-1:0] dout2; output reg [DOUT_WIDTH-1:0] dout3; //****************************************************************************** // 变量位宽表示中符号-:功能的验证 //****************************************************************************** always @(posedge clk or negedge rst_n) begin if(rst_n==1'b0) begin dout1 <= (0); dout2 <= (0); dout3 <= (0); end else begin dout1 <= din[1*PAYLOAD_WIDTH-1-:PAYLOAD_WIDTH]; dout2 <= din[2*PAYLOAD_WIDTH-1-:PAYLOAD_WIDTH]; dout3 <= din[3*PAYLOAD_WIDTH-1-:PAYLOAD_WIDTH]; end end //****************************************************************************** endmodule //*********************************************文件结束*****************************************************

其modelsim仿真结果如下:

通过观察仿真结果发现,已验证了+:和-:的上述规则。