【原创】慢时钟域对快时钟域脉冲信号的采集

3赞

发表于 4/19/2016 6:39:55 PM

阅读(11593)

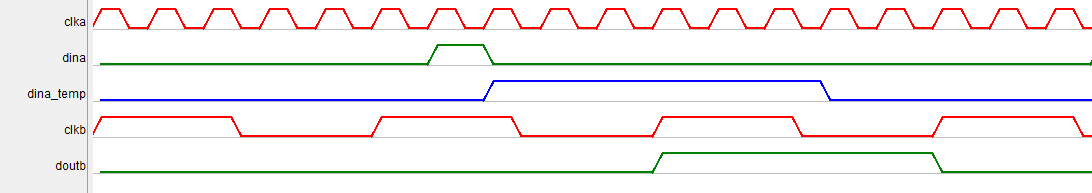

首先来看一幅时序图,如图1所示。快时钟域clka中有脉冲信号dina,如果慢时钟域clkb中直接对脉冲信号dina进行采样,将无法正确采集到该脉冲。

图1 直接跨时钟域采样脉冲信号

一般情况下,对于慢时钟域过渡到快时钟域,可以采用边沿检测技术完成信号的过渡;而对于快时钟域过渡到慢时钟域或两个时钟域的时钟相差不大时,可以用存储器完成信号的过渡,如双端口RAM、异步FIFO或外部存储器(SDRAM、DDR等)等等。不过,在这里我要介绍的一种方法是人为延长快时钟域的脉冲信号,使其可以被慢时钟域的时钟采集到,如图2所示。在快时钟域clka中,当脉冲信号dina到来时,对dina信号进行人为延长获得脉冲信号dina_temp,使得dina_temp的脉冲时间大于慢时钟域clkb的周期,即Tdina_temp > Tclkb。为了增加采样的稳定性,可以使dina_temp的脉冲时间大于慢时钟域clkb的周期的2倍,即Tdina_temp > 2*Tclkb。

图2 人为延长脉冲信号使其可以被正确采样

补充:对快时钟域clka中的脉冲信号延长后,就可以在时钟域clkb中采用边沿检测技术采集到输入的脉冲信号了。关于边沿检测,可以参考经过我修正后的博文:

http://blog.chinaaet.com/crazybird/p/5100000173 。

更详细的设计过程可以参考CB哥的博文:

http://www.cnblogs.com/crazybingo/archive/2011/07/26/2117149.html 。