【原创】Vivado设计实战 ——等精度频率计(完结篇)

0赞Vivado设计实战

——等精度频率计(设计篇)

硬件平台:ZedBoard

开发工具:Vivado 2014.1

1、PS寄存器功能划分

reg0:控制寄存器0(offset:0x00)

Bit | 功能 |

Bit31~bit2 | 保留 |

Bit1 | 闸门信号Tpr |

Bit0 | 复位/清零信号clr |

reg1:数据寄存器Nstd(offset:0x04)

Bit | 功能 |

Bit31~bit0 | 标准时钟计数值 |

reg2:数据寄存器Ntest(offset:0x08)

Bit | 功能 |

Bit31~bit0 | 待测信号计数值 |

reg3:OLED控制寄存器(offset:0x0c)

Bit | 功能 |

Bit31~bit6 | 保留 |

Bit5 | OLED_VDD |

Bit4 | OLED_VBAT |

Bit3 | OLED_SDIN |

Bit2 | OLED_SCLK |

Bit1 | OLED_RES |

Bit0 | OLED_DC |

2、具体实现

本文方案实现亦分为两部分,一是计数值的获取,该部分由测频控制模块(PL实现)完成;二是结果的计算及显示,该部分工作由PS完成。采用ZedBoard板载的100MHz时钟信号作为标准信号,可使测量的最大相对误差小于或等于10-8。

2.1 频率计主控模块

测频主要控制部分结构图在原理篇已经给出,该结构并不复杂,且所用元件较为常见。因此可以自行编码实现,也可以调用元件库实现。

这部分涉及到创建基于AXI总线的IP核,方法和之前《Vivado轻松实现IP封装》的流程类似,差别在于选择操作类型为“Create a new AXI4 peripheral”,按向导完成即可,此处不再详述,如果有人想要详细教程可以留言给我。

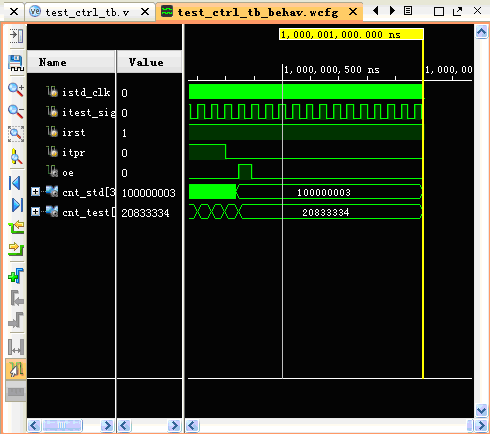

主控模块仿真结果:

图1 测频控制模块仿真结果

我们在Testbench中给出的待测信号为:

always #24 itest_sig = ~itest_sig; // T=48ns F= 20.8333MHz

测量时间:tpr=1s

结果分析:

标准时钟计数值cnt_std=100000003

待测信号计数值cnt_test=20833334

待测信号频率为Ftest=20833334*100MHz/100000003=20.833333375MHz

绝对误差为:Ftest-F=20833333.375-20833333.333Hz=0.042Hz

相对误差为:(Ftest-F)/F=0.042/20833333.333=2.016e-9

2.2 综合结果:

这个图质量不是太好,不是在自己电脑上做的,随手拍了一下,凑合看吧,从综合结果可以看出,实际产生的电路和我们设计的原理框图对应得很好。

2.3 结果的计算及其显示

计算很简单,就是一个除法,成功的关键在于AXI总线通信无误。

显示工作由OLED负责,之前做过OLED的驱动,此部分也不难,此处不予赘述,关于OLED请参考《一步步艰难搞定OLED》,若想移植到Vivado平台,遇到问题可以在本文提问。

4、测量结果及分析

实测数据:

| 测量结果1(Hz) | 测量结果2(Hz) |

Std_cnt | 99999965 | 99999978 |

Test_cnt | 30303042 | 30303042 |

待测信号频率:

F=30.303030

计算结果:

Ftest1=(30303042/99999965)*100MHz=30303052.60Hz

相对误差:22,绝对误差:7.26*10-7

Ftest2=(30303042/99999978)*100MHz=30303048.66Hz

绝对误差:18,相对误差:5.94*10-7

这个地方有点疑问,从之前的理论分析来看,相对误差应该小于10-8。实际测量的结果来看,相对误差远大于10-8,但是问题也不是太大,应该不是设计的问题,一个比较大的可能性是30.303030MHz的待测信号,这个30.303030MHz是ARM内核输出的信号,这个数值跟真正输出的频率应该是有差别的。另一个可能性是测量的闸门时间Tpr还不足1s,这里就不再多试了,精度也可以了。

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521