【Vivado】JTAG2AXI IP详细教程

0赞JTAG AXI IP详细教程

版权声明:

本文由博主“cuter”发布。欢迎转载,但不得擅自更改博文内容,也不得用于任何盈利目的。转载时不得删除作者简介和版权声明。如有盗用而不说明出处引起的版权纠纷,由盗用者自负。

博客官方地址:

ChinaAET:http://blog.chinaaet.com/cuter521

EDN China: http://bbs.ednchina.com/BLOG_cuter521_356737.HTM

1、前言

对于每个IP,Xilinx都提供了文档,对于喜欢自己研究的人而言,可以去看PG174,即该JTAG 2 AXI Mater IP的Product Guide,看完之后,相信应该可以自己完成本文的内容。

2、JTAG to AXI Master IP简介

JTAG to AXI Master IP是用户可定制的IP核,能够在FPGA内部进行AXI传输,驱动AXI信号。该IP能够驱动AXI4-Lite或AXI4 Memory Mapped从接口。AXI总线接口协议、AXI数据总线宽度都是可配置的,配置方法与其他IP核类似,在BD中双击IP核弹出的配置界面更改相应参数即可。需要指出的是,该IP不是用来仿真的,只有在使用Vivado逻辑分析仪Debug的时候,才能利用该IP进行动态实时交互,算是一种HIL(Hardware In Loop)仿真吧。

3、使用JTAG2AXI Master IP的好处

个人看来,最重要的好处有两点:

3.1、 加快硬件调试进度

有Zynq开发经验的朋友都知道,无论是ISE还是Vivado,一旦添加了PS硬核,编译时间是相当长的,我之前用8核64G内存的工作站开发一个不是很复杂的项目时,编译时间都将近20min。

传统的调试方法是PS+ChipScope架构的,即:利用PS发起总线读写命令,然后在ChipScope中观测到相应信号变化,根据反馈修改IP核逻辑代码。

由上文的分析可以看出,传统的调试方法是非常耗时的,因为修改逻辑之后,需要重新生成Bitstream才能进行下一轮测试。

如果使用JTAG2AXI Master代替PS完成总线读写控制,调试时花费在综合、实现上的时间就会少很多,我第一次使用该IP时,点了Generate Bitstream之后,本以为要等很久(我自己的电脑配置比工作站差远了:(),没想到10分钟左右就OK了,后来思考了一下,应该是PS的关系。

3.2、 可以将软硬件调试工作隔离开来

软硬件联合调试时会出现一种不可避免的问题:对错误进行准确定位。不知道你们有没有遇到过这种情况:软件工程师觉得问题在于硬件,硬件工程师觉得问题在于软件……好吧,说的难听点就是扯皮、推脱责任。

使用JTAG2AXI Master IP调试IP时,没有PS的份了,所以在一定程度上硬件工程师可以确保自己的逻辑是OK的,这样有助于Bug的定位。

4、调试AXI-Lite IP核

本小节,开始实战,利用JTAG2AXI Mster IP调试一个AXI-Lite IP,硬件平台为ZedBoard,软件环境为Vivado 2014.2。

AXI-Lite IP情况简述:

该IP有两个寄存器,一个Register用于测试AXI总线写操作,偏移地址为0x00,该寄存器低8位送至Zed上的8个Led;另一个Register用于测试AXI总线读操作,偏移地址为0x04,该寄存器低8位连接至Zed上的8个Switch开关。

IP核创建就不说了,参考前面的博文吧。上点图:

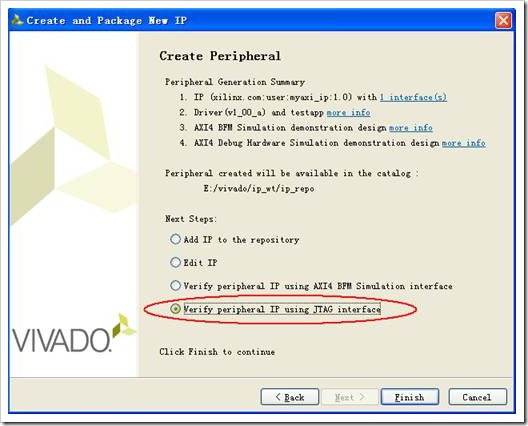

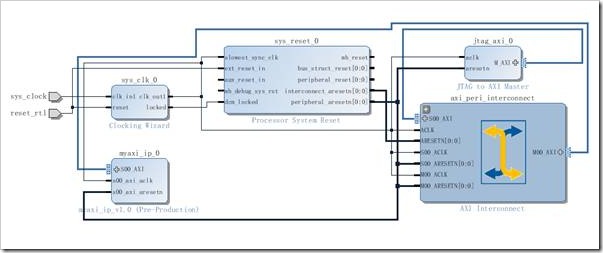

与前文有所不同的是,为了利用JTAG2AXI IP进行调试,在创建IP向导的最后一步,选择“Verify peripheral IP using JTAG interface”,点击Finish按钮后,Vivado会自动调用JTAG2AXI IP以及你所创建的IP核创建测试工程。创建完毕后的BD如下图所示:

利用向导创建的IP核是没有实际用处的,需要根据自己的需求修改IP核,修改后BD如下图所示:

下面到Logic Analyzer了,具体操作不说了,之前写过了,打开Hardware Manager,Program device,然后就可以在下面的Tcl Console输入调试命令了。

测试结果:

参考上一篇博文吧。

5、结束语

本来想在总结的时候说一下感受啊什么的,考虑了一下,把优点放前面了,给读者一个看下去的理由……这里就不重复了,好不好用,感受一下就知道了!