【VIP之旅】FPGA的“特权”流水操作,初步理解

0赞

发表于 6/16/2014 11:52:03 AM

阅读(4819)

module test_Pipelining ( input CLK, input RSTn, output reg [7:0]result ); reg [7:0]x,y; reg [3:0]i; always @(posedge CLK or negedge RSTn) if(!RSTn) begin x <= 8'd0; y <= 8'd0; i <= 4'd0; end else case(i) 0: begin x <= 8'd1; y <= 8'd1; i <= i + 1'b1; end 1: begin x <= 8'd2; y <= 8'd2; i <= i + 1'b1; end 2: begin x <= 8'd3; y <= 8'd3; i <= i + 1'b1; end 3: begin x <= 8'd0; y <= 8'd0; i <= i; end endcase reg [7:0]result0; always @(posedge CLK or negedge RSTn) if(!RSTn) begin result0 <= 8'd0; end else begin result0 <= x + y; end reg [7:0]result1; always @(posedge CLK or negedge RSTn) if(!RSTn) begin result1 <= 8'd0; end else begin result1 <= result0 * 8'd3; end always @(posedge CLK or negedge RSTn) if(!RSTn) begin result <= 8'd0; end else begin result <= result1 + 8'd5; end endmodule

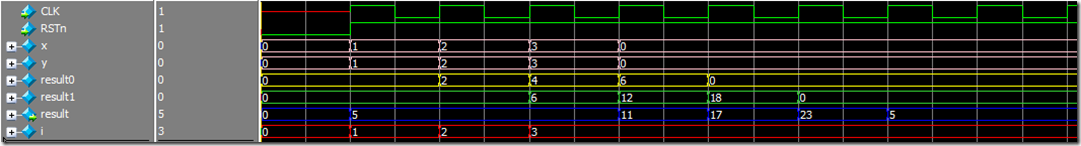

将公式(x + y) * 3 + 5,猜分成3个步骤

1、result0 <= x + y;

2、result1 <= result0 * 8'd3;

3、result <= result1 + 8'd5;

result0延时x,y一个周期;

result1延时result0一个周期;

result延时result1一个周期;

那么,result延时x,y 3个周期;且一一对应!!

因为x,y是源源不断的输入(每个周期改变一次)

所以 result在3个周期后,是源源不断的输出~~!!

总结:1、潜伏周期 = 步骤数。

2、最后一个数据的输入时刻 + 潜伏周期数(或者步骤数) 就是整个流水操作的完成时刻。

技术讨论欢迎加群~~电子技术协会 362584474