【原创】如何快速在Vivado IPI中使用HLS生成的IP

0赞我们在Vivado HLS中用高层次综合来快速地产生可综合的代码,最终的目的还是把它与其它的模块、IP等进行相连,以实现一个更加复杂的设计,所以在本博文中,我们就来学习一下,如何把Vivado集成开发环境的IPI中使用HLS中生成的IP。

首先,在Vivado HLS中新建工程,或者基于现有的工程,把代码综合为IP Catalog。

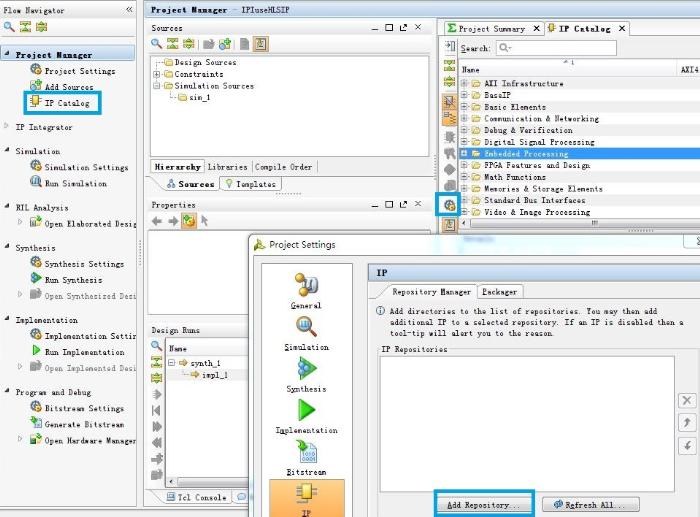

然后,新建一个Vivado的RTL工程,先不指定工程文件,并选择开发板为MicroZed。工程建立之后,选择工程管理器中点击IP Catalog,在弹出的IP Catalog中点击右键,或者直接点击齿轮形状的设置按钮,打开IP的设置,然后点击Add Repository,把我们自己建立的IP导入Vivado IPI的IP“仓库”中,如图1所示。

图1 添加IP

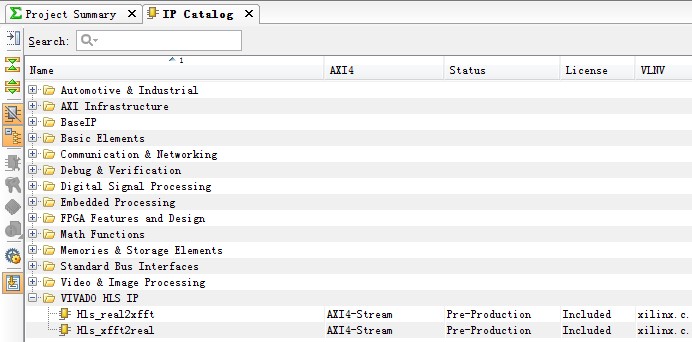

找到Vivado HLS在导出到IP Catalog后产生的.zip文件,点击确定,则在Vivado的IPI中就可以看到我们自定义的IP了,如图2所示。

图2 加入IPI“仓库”的IP

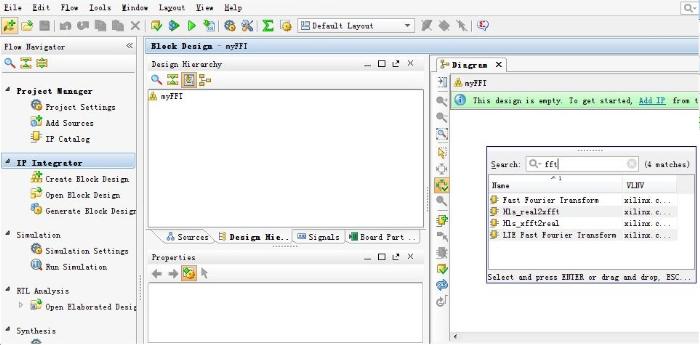

接下来,我们就可以在Vivado IPI中例化一个我们从HLS中生成的IP了。点击Vivado工程管理器中,IP Integrator下面的“Create Block Design”,然后点击ok,完成一个模块文件的设计。因为新的设计模块文件中还没有任何IP,所以Vivado会提醒我们添加IP。点击IP,并输入关键字FFT,此时包含FFT的IP被列举出来,如图3所示,其中,中间两个为我们在Vivado HLS中导出的IP。

图3 包含fft的IP

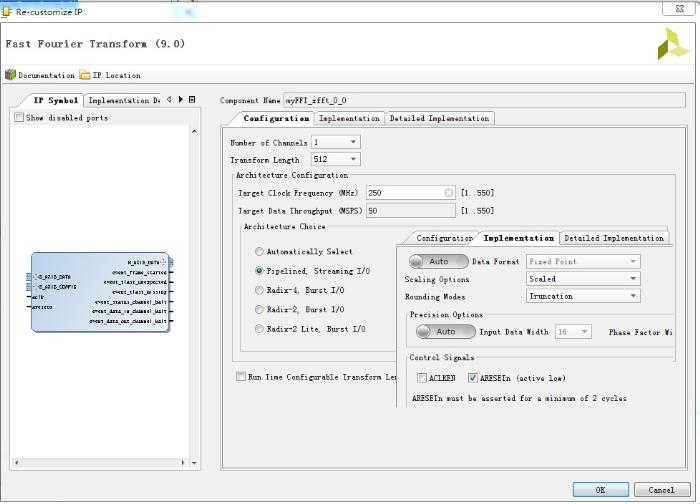

然后例化Vivado 自带的IP。双击图3中的Fast Fourier Transform,或者把它拖拽到模块文件的视图中,等待片刻之后,该IP的一个例化被加入到IP模块设计文件的视图中。然后双击例化之后的IP模块,打开它的配置,如图4所示。

图4 Vivado自带FFT IP的配置

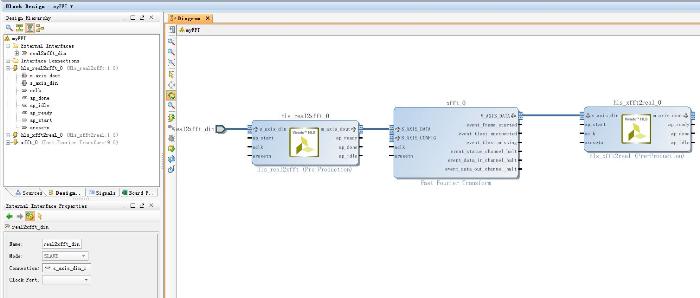

然后在图3 包含的fft的中,把我们自定义的两个IP也加入到模块文件中。在完成了以上3个IP的例化之后,把它们的AXI4数据端相连,如图5所示。

图5 IP之间的连线

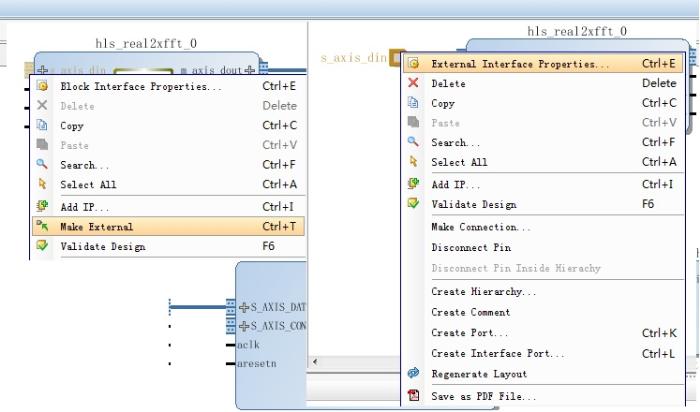

在第一个模块的s_axis_din上面点击右键,选择Make External,然后在生成的端口上点击右键,选择External Interface Property,更改它的名字, 如图6所示。

图6 更改IP的端口配置

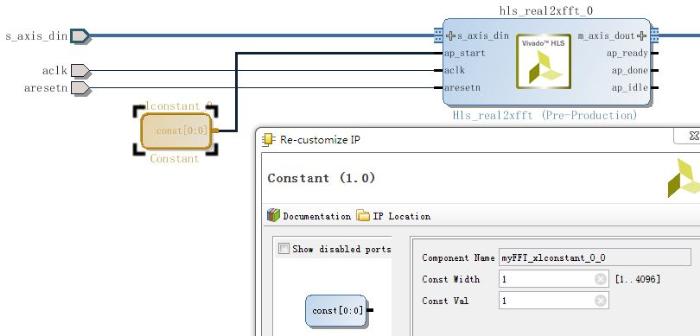

按照同样的方法,把Hls_real2xfftIP模块的aclk端口和aresetn端口都设为外部端口,在该IP的ap_start端口上则点击右键,选择Add IP,添加一个Constant IP,即接口信号为常数,如图7所示。

图7 添加常数IP到端口

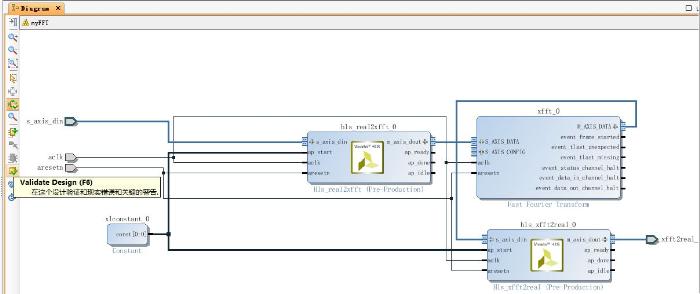

同理,把Hls_xfft2real模块的ap_start也连接到图7中创建的Constant模块上,并把FFT和Hls_xfft2real模块的aclk都连接到第一个IP的aclk连线上,它们的aresetn则都连接到第一个IP的aresetn连线上,最后则配置输出端口,把Hls_xfft2real的输出数据端口配置为外部连接端口,并重命名,最终的连续如图8所示。

图8 最终连线

然后点击图8中的Validate Design,让Vivado自动进行设计的有效性验证,无误之后点击Vivado菜单栏的File---Save Block Design,保存我们的模块设计文件。

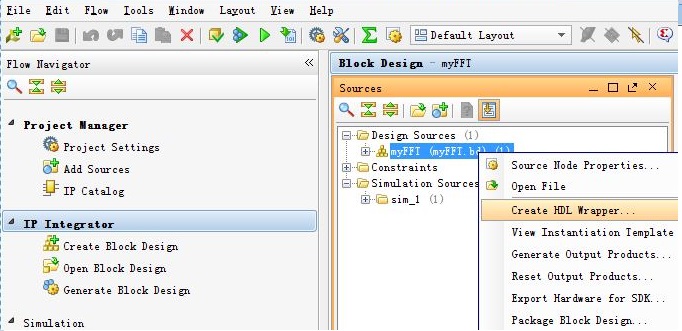

既然在Vivado IPI中的IP配置已经完成,接下来就可以产生HDL文件,让Vivado自动把相关的IP打包例化了。首先点击Vivado设计流程管理器中,IP Integrator下面的Generate Block Design,从而把图形化的IP设计文件导出为Vivado源程序,然后在生成的.bd文件上点击右键,选择Create HDL Wrapper,从而产生HDL打包文件,如图9所示。

图9 产生IP打包文件

至此,我们的IP已经被Vivado例化到HDL文件中了,接下来可以进行设计的仿真、硬件下载验证了。

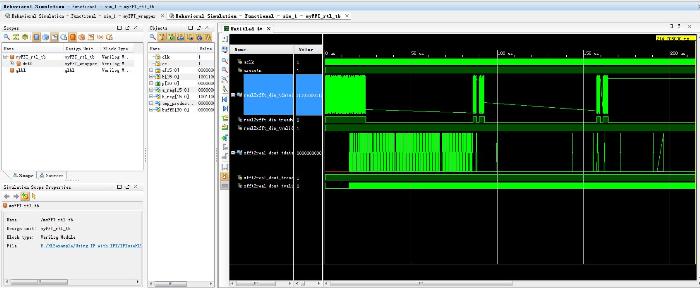

Vivado自带仿真工具Xsim的性能已经得到了极大地提高,使用6个CPU线程进行处理,很快就完成了仿真的编译、加载和运行,仿真结果如图10所示。

图10 仿真结果