手把手系列教程Basys3篇之四:用Verilog生成一个简单的时序电路(计数器)

2赞在这个设计实验中,我们将演示如何。此外,我们还将演示一个分层设计,使用一个独立的显示组件,将二进制的数值转换显示到七段显示器上。

工程中所使用的软件版本为Xilinx Vivado 2016.2,硬件是Basys3开发板。当然,你也可以用容易将它移植到Nexy4DDR开发板上。

建议在学习这一例程前,先完成较为简单的社区手把手系列教程Basys3篇之三:Basys3 FPGA 3-8译码器实现(http://www.digilent.com.cn/community/154.html),然后再来尝试这一实验。前一个例程,将教会你如何生成一个新的工程和添加设计源文件。

好了,下面让我们开始吧!

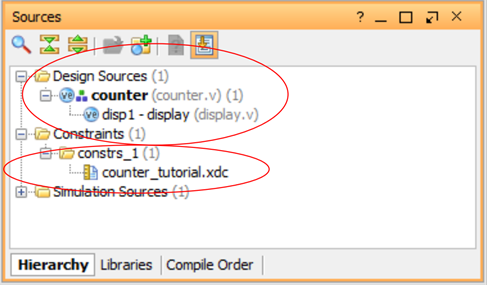

下面这一工程中使用了两个设计源文件和一个管脚约束文件。

顶层模块 counter 包含了一个从100MHz的FPGA时钟所生成的1Hz时钟代码,和一个在1hz的频率下工作的0到9计数器。

顶层模块同时也例化了一个低层次的显示模块副本。

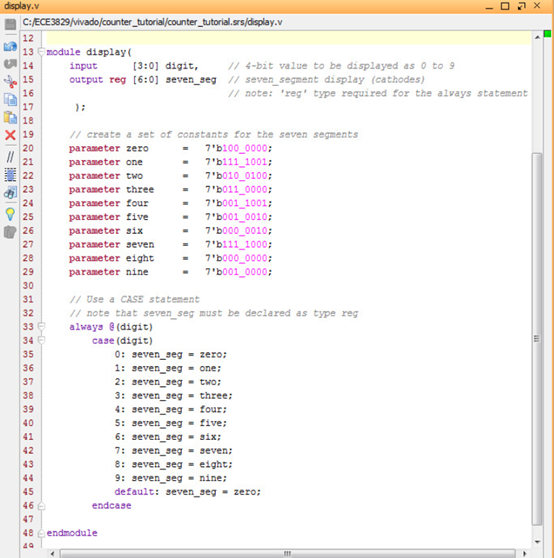

display 模块将0到9的值转换为七段字符。

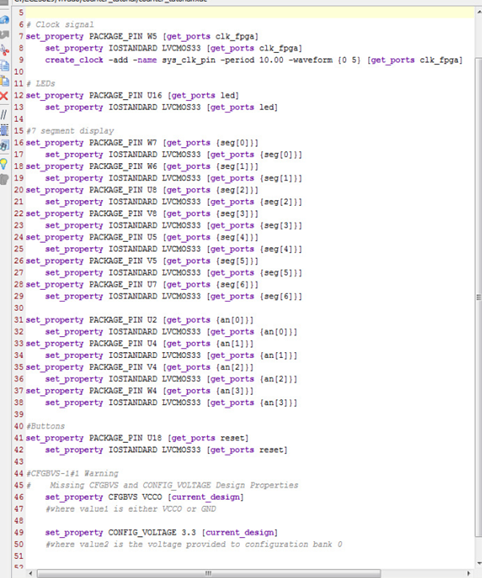

第三个是管脚约束文件,在工程使用的端口要指定FPGA对应的引脚,这个管脚约束文件专门针对Basys3开发板。

下面演示三个设计源文件

如果你已经在里工程添加好三个设计源文件,那么你可以一步步点击‘Run Synthesis’>=‘Implementation’>=‘Generate Bitstream’:

8个综合后的警告是由于设定的恒定值被用于驱动阳极七段的显示。这就是我们的设计目的,我们可以忽略这些警告。

如果比特流文件已经生成,那么你可以通过下载Hardware Manager下载到FPGA里了。(可以到Decoder设计指导查看更多的细节)。

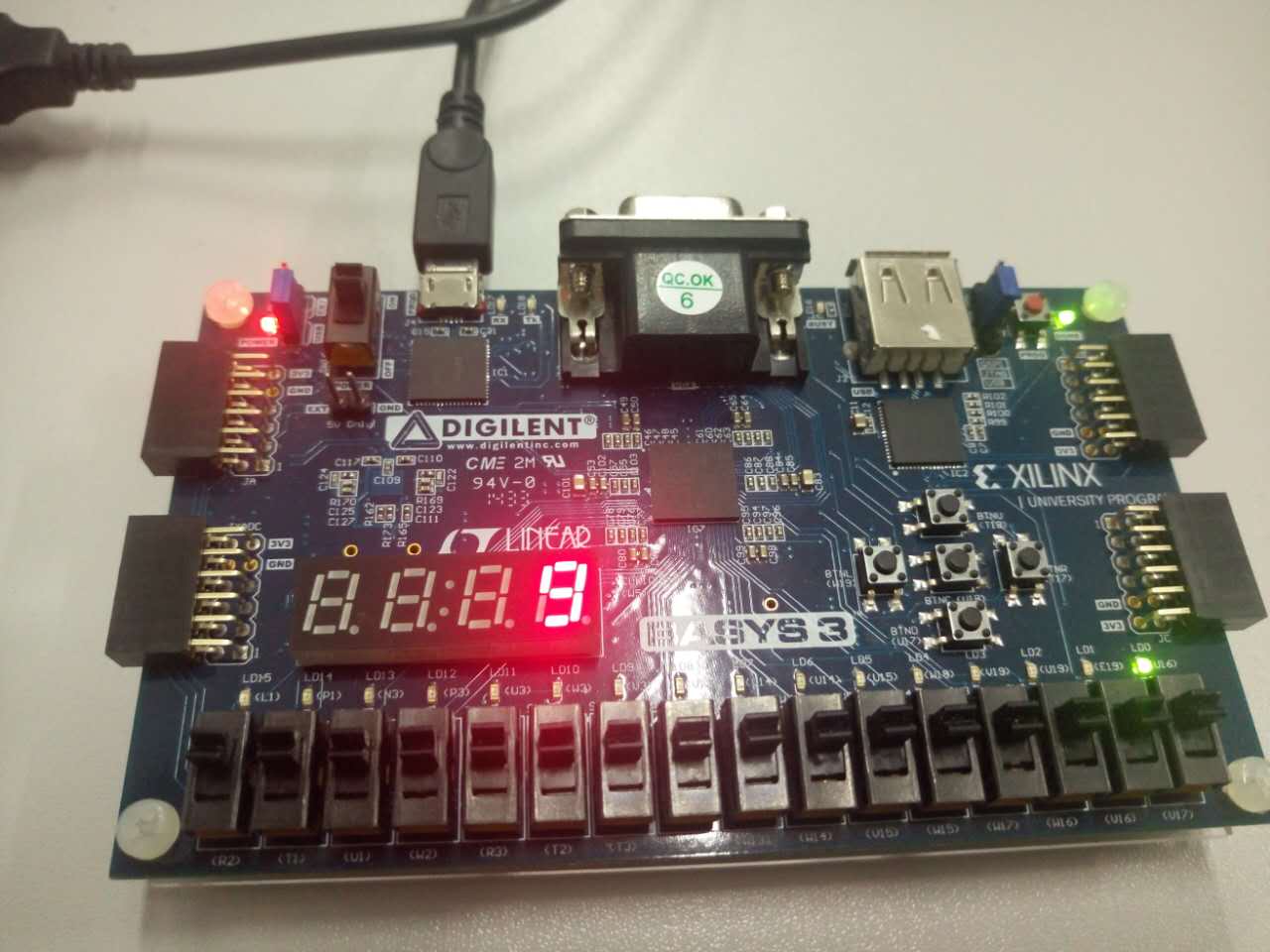

当下载完成后,你可以看到数码管每秒钟循环显示0到9的数值。当计数到9的时候led同时会亮起来。

其他有用的注释:

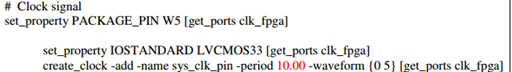

在约束文件里我们指定FPGA的时钟是100MHz(单次10ns的时间)。

这将需要的工具用来实现设计FPGA,所以它可以运行在这个速度上。

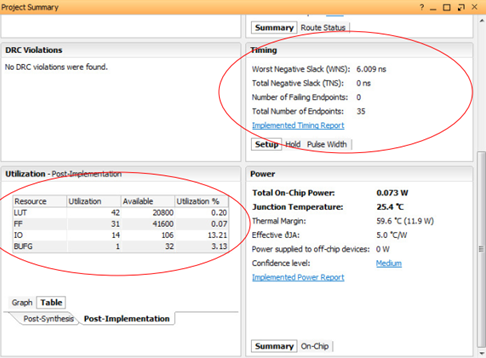

下面总结了这个工程设计的时序要求。

我们还可以看到FPGA实现设计所需的资源。一个使用了42个LUTs和31个FFs。LUT被用在实现设计的组合逻辑中,触发器被使用在实现时序逻辑电路中。31个触发器是需要实现1Hz时钟(27个触发器),和计数器(4个触发器)。

学习心得:

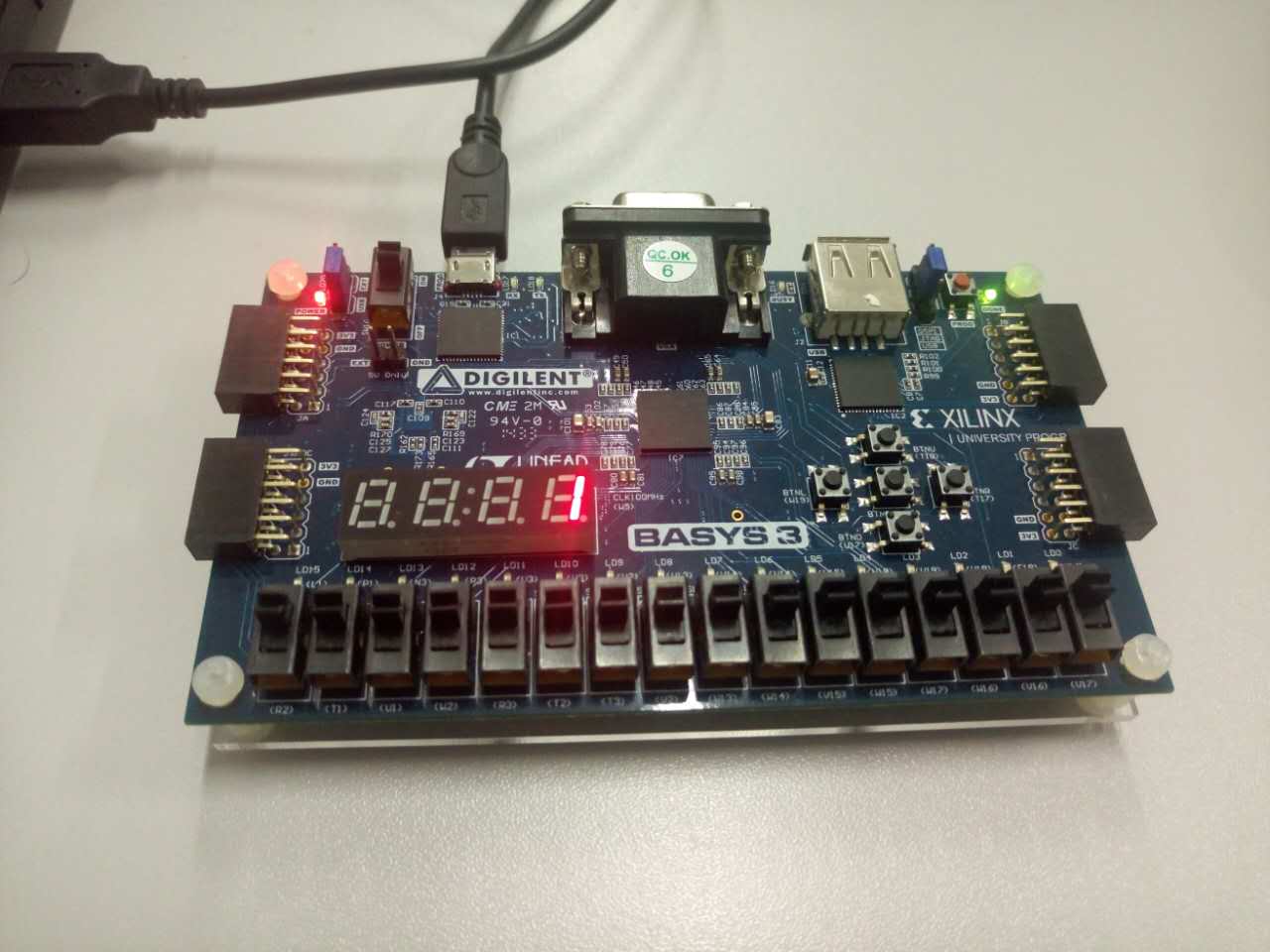

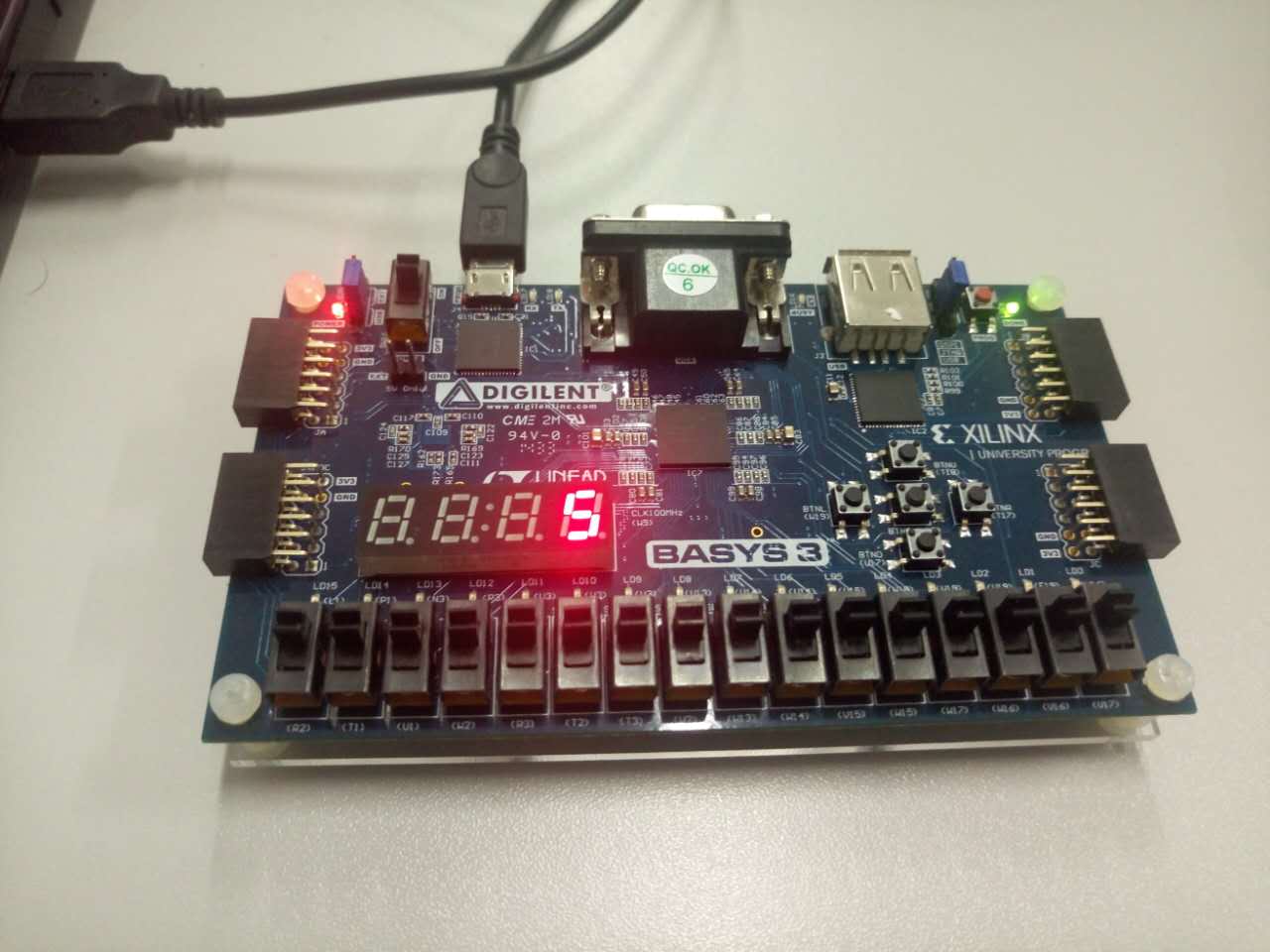

编辑好文档后马上就上板验证了,先来看看结果怎么样

当计数到9的时候led灯会亮起来哦

在经历过一次英文文档的翻译后,这次学习起来也开始有点上手了,学会了计数器的设计方法,一秒的计数器定时,还有数码管的显示,结合上一次的点灯实验,有进一步熟悉了vivado的简单操作流程,学习FPGA就是这样子不断积累经验的,相信自己接下来可以做的更好哦

下面还是有附件翻译文档和工程文件(⊙o⊙)哦