Vivado bug大揭秘——综合实现参数配置中的Bug及解决办法

0赞综合、实现是一个工程中必不可少的两个环节,是生成最终bit文件的两个必经步骤。在综合实现的配置选项中,有一些参数供用户选择配置,来指导工具的综合以及布局布线。这些参数的能够协调速度与面积、以及软件的运行速度等之间的关系,是设计中需要考虑的关键点之一。然而,在VIVADO中,一些参数的搭配不当,再加上一些工程中特殊的因素,导致Bug的出现。下面,我们首先简要介绍一下综合实现中的配置参数,然后针对某一特定工程,演示其中存在的Bug,并给出解决的方法。

一、综合实现中的选项

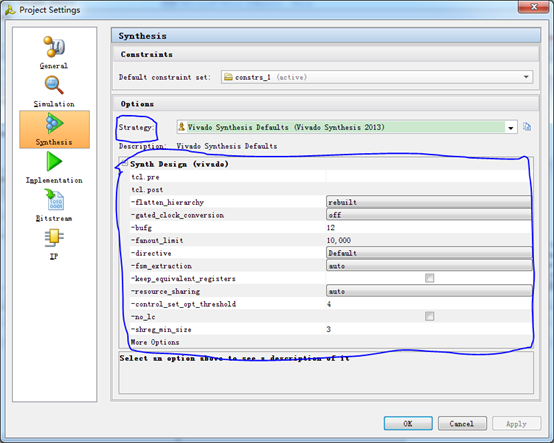

下图是VIVADO中综合的配置选项,其中有flatten_hierarchy、bufg、fanout_limit等等一些选项的配置,其意义可以参考VIVADO的UG文档。对于这些参数的配置,VIVADO提供了一些备选的策略,就是Strategy,用户可以选择Vivado Synthesis Default、Flow_RuntimeOptimised等,在选定了某种策略后,综合参数就会自动做相应的配置。当然,我们也可以创建自己的综合策略,然后保存下来。

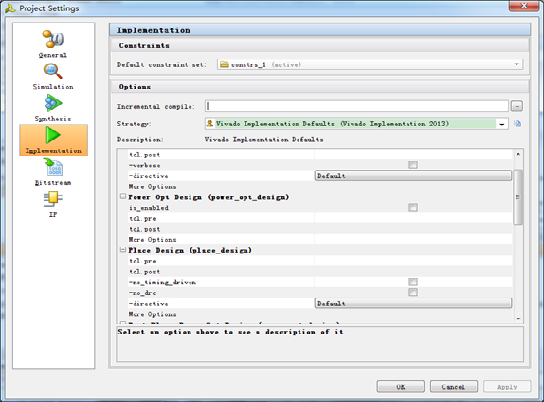

下图是实现的配置选项,使用方法同综合配置选项的相同,就是配置的参数较多,包括opt_design(优化的配置参数)、power opt design(功耗优化的参数)、place design(布局参数)、post-place power opt design(布局后功耗优化)、Phys opt design(物理优化)、route design(布线)、Write Bitstream(生成bit文件的参数)等。

一、存在的Bug及解决办法

问题描述:

这里首先做个解释,把下面的问题称之为Bug,可能有点牵强,因为这种问题不能在不同的工程中复现,然而在某些特定工程中确实是存在的,我们姑且称之为Bug吧。

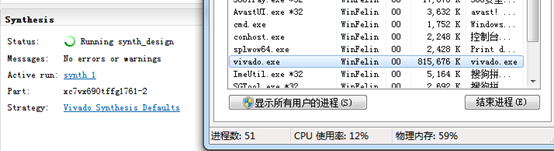

在某些工程中,对于综合的选项,我们采用默认的Strategy,并对其中的一些参数选项做修改,然后综合工程,我们会发现软件会在综合的某个阶段停滞不前,如下图所示,软件界面中一直显示的是正在综合,然而任务管理器中VIVADO的进行确实CPU利用率为0。

解决办法:

对于这样的问题,我们刚开始怀疑是工程中的某些参数配置不当,然而与正常的工程仔细对比,这些选项并没有差异。后来,我们摸索发现,如果综合采用软件中已有的Strategy,尽量不要再修改其综合选项的参数;如果要修改其中的某些参数,可以自己创建一个Strategy,将相应的参数配置好,如下图所示,创建自己的TD综合策略,此时,我们再重新综合,就不会有上述所说的卡死现象。

最后也希望大家多多支持,多投票点赞让我有信心继续写下去