FPGA实战演练逻辑篇52:基本时序路径

0赞基本时序路径

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

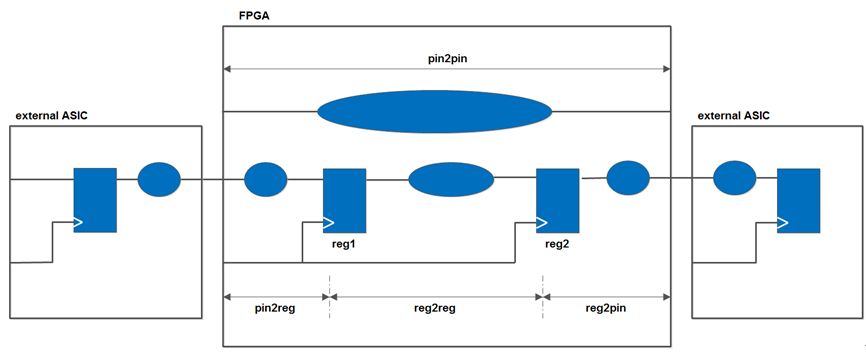

对于FPGA内部而言,通常有四大类的基本时序路径,即:

● 内部寄存器之间的时序路径,即reg2reg

● 输入引脚到内部寄存器的时序路径,即pin2reg

● 内部寄存器到输出引脚的时序路径,即reg2pin

● 输入引脚到输出引脚之间的时序路径(不通过寄存器),即pin2pin

前面三类是和FPGA内部的寄存器相关的,也是和时钟相关的,所以我们关注的重点还是数据信号和时钟锁存沿之间的建立时间和保持时间关系。而最后一类信号的传输通常不通过时钟,因此它的时序约束也相对直接,我们一般是直接约束pin2pin的延时值范围。这四类时序路径的基本模型如图8.13所示。(特权同学,版权所有)

图8.13 时序路径基本模型

我们逐个来看这四类基本路径所约束的具体时序路径。(特权同学,版权所有)

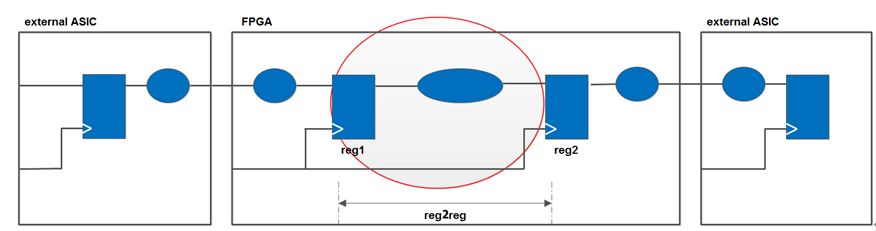

reg2reg路径约束的对象是路径起始的源寄存器以及最终结束的目的寄存器都在FPGAn内部的路径。如图8.14所示,FPGA内部圈起来的部分是从一个寄存器到另一个寄存器的路径,他们共用一个时钟(当然也有不共用一个时钟的reg2reg路径,这种路径的分析会复杂一些,这里不做深入讨论)。对于reg2reg路径,我们只要告诉FPGA的时序设计工具他们的时钟频率(或时钟周期),那么时序设计工具通常就“心领神会”的让这条reg2reg的路径延时符合这个固定时钟频率所要求的范围内(即它的建立时间和保持时间得到满足)。(特权同学,版权所有)

图8.14 reg2reg路径模型

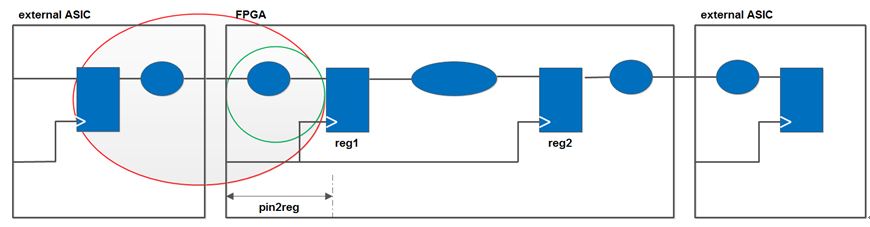

我们再来看pin2reg的路径模型,如图8.15所示。虽然和FPGA连接的外部芯片内部寄存器的状态我们无从知晓(一般芯片也不会给出这么详细的内部信息),但是一般芯片都会给出针对于这个芯片引脚的一些时序信息,如Tco(数据在芯片内部的路径延时)、Tsu(建立时间)和Th(保持时间)等,我们也可以用图示的这个模型来剖析一下芯片所给出的这些时序参数的具体路径。在这个模型中,画圈部分所覆盖的路径代表了和FPGA内部reg2reg分析一样的模型,pin2reg原则上只是reg2reg的一部分。FPGA内部的小圈部分则表示我们实际要告诉FPGA的pin2reg约束信息。或者可以这样说,我们能够进行路径控制的就是这段小圈所覆盖的路径。但是,我们还需要通过整个reg2reg路径的情况,即小圈以外、大圈以内这部分路径的延时情况去告诉FPGA内部pin2reg路径延时应该限制在什么样的范围内。(特权同学,版权所有)

图8.15 pin2reg路径模型

reg2pin的路径如图8.16所示。同样的,大圈部分覆盖了FPGA内部的源寄存器到FPGA外部芯片的目的寄存器为止的reg2reg的路径。外部芯片通常也不会给出详细的信息,而是通过相对它们的引脚给出一些时序的信息。而小圈所覆盖的路径则是我们需要去约束的reg2pin的延时。它的延时信息同样是需要通过大圈以内、小圈以外的路径情况来推测得出。(特权同学,版权所有)

图8.16 reg2pin路径模型

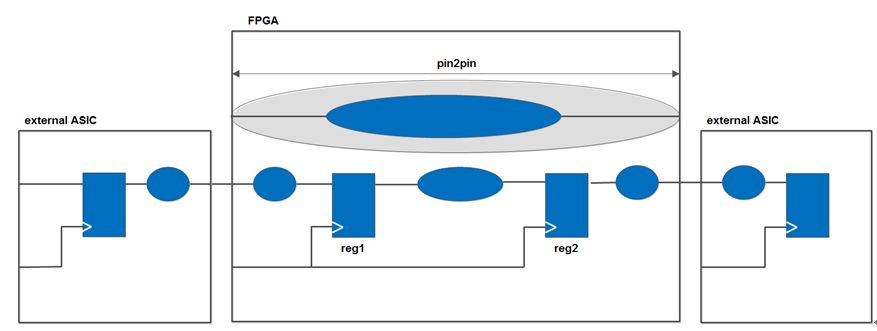

最后,我们再来看看pin2pin的路径。如图8.17所示,FPGA内部上方的大圈内路径是pin2pin的路径,即FPGA外部信号从FPGA的输入引脚到输出引脚所经过的整个路径延时,这个路径中不经过任何寄存器,它的整个路径延时基本上只是一些组合逻辑延时和走线延时。这类路径在纯组合逻辑电路中比较常见,也必须在时序分析中覆盖到。这类路径也没有所谓的建立时间和保持时间,设计者关心的是这条路径从输入到输出允许的延时时间范围,而在做时序设计时,设计者只需要把这样的最大和最小延时值传达给时序设计工具即可。(特权同学,版权所有)

图8.17 pin2pin路径模型