【原创】深入剖析Kinetis系列内部IO结构(内附详图)

1赞高铁模式继续开启,喝了一口凉白开,啃了口肯德基鸡腿,开始码字啦(这画面太美好了有木有…)。写到这,我突然感觉自己越来越有宅男的气质了。说起宅的话不得不提一下最近网络比较火的“御宅”一词,笔者刚看完最强大脑最新的一期,玩俄罗斯方块的日本天才,号称“御宅”一族,真是把我惊到了,人家真是宅出技术宅出境界来了啊,在拜服的同时又有点小小的得意自豪啊,俺这宅在高铁上也是宅呀,起码从这点上来看,俺跟这些天才还是站在一个高度上了,咳咳。。。

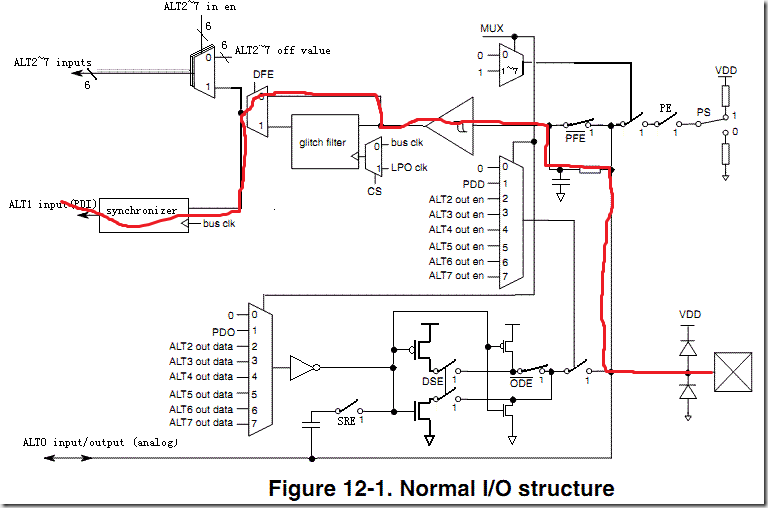

好了,聊完“宅”之后(聊宅?聊斋?咳咳,看来蒲松龄老人家估计也是宅的够呛)咱还是继续聊技术吧。本篇博文的题目俺之所以后加了个“内附祥图”这几个关键词实际上是有点小心机的,呵呵,就像大家看新闻头条都喜欢看带图片的一样。毕竟一提到要讲芯片的IO结构,估计好多人会觉着GPIO有啥好讲的没有啥技术含量,而我的目的就是把这些人也吸引进来,等到大家看完整篇文章之后就会明白俺的良苦用心了,我们之前使用IO都是知其然不知其所以然(配置个方向寄存器和输入输出寄存器就完了,却没有了解到芯片内部逻辑是怎么做到的),而我写这篇文章的目的就是想让大家知其所以然,在以后使用的过程中出现一些比较隐藏的问题时我们也可以有据可依,按图索骥找到问题的根本所在。下面我先上个飞思卡尔(NXP)ARM家族的Kinetis系列内部IO的结构框图(新鲜出炉哦)和其用户手册中的PORT管脚配置寄存器的内容,大家先看看图把图中的一些字符和寄存器的配置位对上号,然后下面我就列出几个平时大家都会用到几个问题,以及这些问题是如何通过下面IO结构框图来解释的,Ready。。。Go:

1. 在配置Kinetis某IO为其他外设功能时是否还可以通过GPIO输入寄存器读取外部IO状态:

这个问题实际上是比较奇怪的,有些人可能压根就没这样考虑过(不是因为我们工程师太单纯,而是大多数应用都比较单一的,某个IO固定为某个外设功能,没有必要再去读取该IO的高低电平状态),而有些人却对此问题打破砂锅问到底,为啥捏(俺东北话又不自觉的冒出来了,呵呵)。我举几个例子就明白了,在电动自行车带霍尔信号无刷电机的控制上就是比较典型的,三路霍尔脉冲信号U,V,W接到单片机的IO配置成输入捕捉功能来获取电机转速,同时又需要单片机同时读取这三个IO电平来判断当前电机转子所在的扇区,又比如做IO闭环控制即我在配置成输出功能的时候同时输出高电平,但是实际上对单片机来说是开环的即单片机不知道最后IO是否变成了高电平或者由于外部电容效应单片机不知道从我输出高电平逻辑到具体什么时候IO真正变成高电平,又比如在我们的IO配置成I2C时由于外部干扰造成I2C从机把I2C总线拉死,这个时候我需要在不关掉I2C总线的前提下周期性的读取下I2C总线电平是否长时间为低以判断是否总线被拉死,又比如。。。咳咳,我暂时就想这么多,大家如果还有类似的应用欢迎博客下面留言也让俺多涨涨见识,总之有这种需求的应用还是蛮多的。那问题来了,我们的Kinetis MCU(其他家的俺没有发言权哈,呵呵)支不支持呢,如下图红线标示,我们可以看到无论我们的Pinmux如何配置,这条通向ALT1 input(就是到GPIO输入寄存器GPIOx_PDI)的红色“丝绸之路”始终是畅通的(中间没有多选一逻辑),所以答案自然不用多说了,怎么样,是不是豁然开朗一目了然呢。不过在这里我多插一句,这条通路对Kinetis系列大多数系列是通用的唯独对飞思卡尔5v ARM Kinetis E系列是不适用的,因为KE系列是从飞思卡尔8位机迁移过去的,其结构是与8位机类似的,所以KE系列的IO在配置成外设时其输入寄存器是读不出IO状态的,需要切换一下,这个是比较麻烦的一个地方;

2. Kinetis的Drive Strength即驱动能力增强功能的原理是什么,其能增强多大的驱动能力?

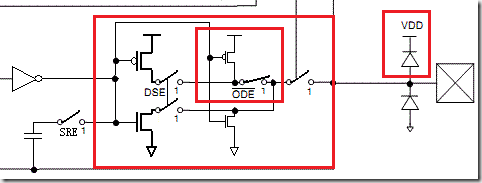

如下图1为PORT控制寄存器的Drive Strength使能位,在该位置1同时IO在配成成GPIO输出时可以增强驱动能力,那是如何增强的呢,见下图2,红色大框为Kinetis的IO配置成输出时的Push-Pull推挽结构,在默认DSE不使能的情况下右边的推挽结构是标准输出能力的,而如果DSE使能的话如小红框所示,则相当于在IO上并联了一个推挽结构从而使输出能力增强一倍,Clear?

3. Kinetis的IO是否可以配置成开漏输出,如果是开漏的话是真开漏还是伪开漏,伪开漏下其上拉电压的最大值是多少呢?

如下图1所示,ODE位是负责配置IO为开漏模式的,而这个开漏是如何实现的呢,实际上很简单。如下图2所示,在ODE为1时相当于推挽结构中的上桥臂MOS被remove掉了(注意此时DSE不能使能),只保留下部MOS构成开漏输出,同时见下图2中的右边小红框,由于IO端口的钳位二极管的存在(钳位到VDD,保护IO管脚),导致伪开漏的存在,所以在IO配置成开漏输出时其上拉的电压最大只能到VDD+钳位二极管的压降(一般为0.3v)即VDD+0.3v,当然上拉电压最低值只需要满足不低于单片机的逻辑1的上限即可,这个可在数据手册中查血得到。

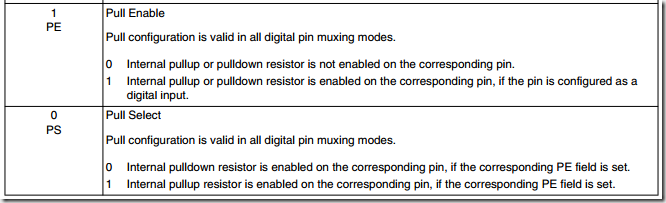

4. Kinetis的IO在配置成输入时默认是否是高阻态?其内部的上拉或者下拉电阻是怎么配置的?

Kinetis的GPIO在配置成IO输入时默认为高阻态,为啥捏?如下两图,即PE和PS两个上拉下拉使能位是关掉的同时如下图2最下面的小红框所示推挽输出开关也是关掉的,所以造成输入时悬浮的高阻态,这种情况是不建议长时间保持的,因为如果做输入检测,而内部上拉下拉没有打开同时外部也没有加上拉或者下拉电阻,那么此刻状态时未知不确定的,所以输入检测是没有意义的(当然不排除有些应用再某些特殊情况下需要保持IO高阻)。所以我们在使用输入功能的时候,是建议内部上拉下拉使能或者外部单独加上拉下拉电阻的,当然内部的上拉下拉电阻是弱上拉(大约几十k欧姆),如果需要强的输入能力,最好还是外部单独加上拉或者下拉电阻。

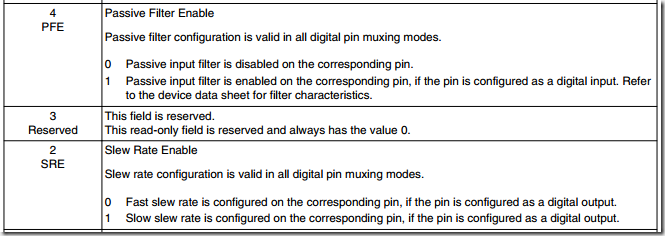

5. Kinetis的GPIO在配置成IO输入时支持有源滤波器功能,在配置成输出时支持输出斜坡控制?

这两个功能是我最喜欢的Kinetis GPIO两个特色功能,即在配置成输入时可配置成有源滤波器以减少外部干扰,而配置成输出时其斜坡控制功能则可以减少单片机本身形成的EMI干扰以及阻抗不匹配造成的通路震荡问题(即正常输出高低电变化时如果理解成斜率很高的方波的话,如果高低电平变化很快会给系统带来很大的高次谐波,而如果打开斜坡控制功能的话则其高低电平的变化则会有一个较平缓的过渡,减少谐波的引入)。总之,这两个功能的确是让我很惊喜的,而且也是颇为Kinetis加分的特色了,哈哈。

好了,今天就写到这里了,IO这个问题虽然看似简单,但是实际上深究起来还是很多学问的是吧,希望大家看下来能有所收获,哈哈。另外,在这里我需要再提一下关于转载我博客的问题,一直有很多博友转载分享我的文章,首先是灰常感谢的(这说明俺写的还是深得民意滴),不过还是希望大家在转载时注意加上文章的出处原链接(我的原创文章一般都是最先在ChinaAET发表的)和俺这个作者的大名啊,不然的话……,不然我也没办法了,呵呵,虽然很无奈但是我心里还是有点深深的那份执着,希望我们国内对知识产权的重视能越来越重视,这个还是靠我们广大工程师们的共同努力地,fighting。。。

再聊,未完待续~