【转】FPGA三国志-第三篇/SOPC篇3-2

0赞

总线结构是SOPC的最重要的战场,也是区分SOPC是否高效的关键因素!

1--说到SOPC,最基本的集成首先是CPU的内置,但是CPU的有下列因素决定总线结构。

- CPU---冯诺依曼结构,CISC体系多采用这种方式,特点,就是指令功能强大,总线结构复杂,堆栈结构设计庞大。 因为要解决所有Master和Salve之间的运算和重写,另外寻址模式非常丰富。 缺点是酒?峁垢丛樱?面积偏大,面积偏大导致这类CPU的频率不能太高!

- CPU--哈佛结构,总线独立,能够提高并行,基本上以数据流加工为主。 所以DSP,以及一些RISC的体系也很多 。

这里声明,RISC,CISC和CPU结构无必然联系。

简单说来:RISC是以总线结构越少越好,通络尽可能简单。例如大部分指令面向寄存器,然后数据操作多数在寄存器完成。 有很多甚至基于堆栈。

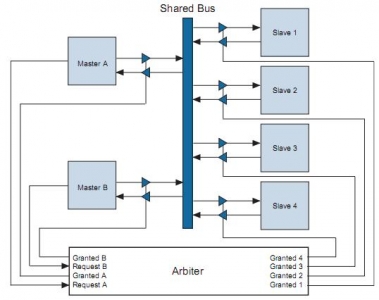

共享总线的速度设计与性能总结:

- 完成相对高的总线频率

- 相对低廉的成本

- 不能并行!(这个是缺点)

- 共用的仲裁结构(缺点,反应速度慢)

- 所有主设备对从设备的存取都存在竞争关系(同时访问时候)

当然在FPGA中,双向三态的实现是依靠多选一和DFF的隔离来实现的,而且,多数为同步设计。 当然在现代分离系统的设计中,已经很早有这样的先例。

例如一个ARM和TI的DSP进行协同的系统,TI DSP中有对总线进行释放的功能机制,释放的时候,可以由ARM来对DSP中的数据结果进行交换,或者是操作参数的更新。 然后再将总线控制权返回给主控的ARM.在FPGA中,也是同样的道理。

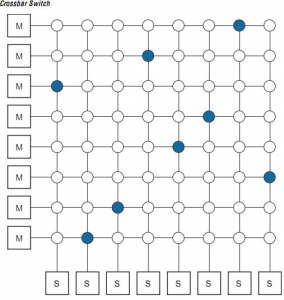

NIOS II的总线结构Avalon是具有全数字交叉的总线结构,支持多主并发的结构。

FPGA中,由于FPGA中丰富的互联结构,以及FPGA中本身的逻辑胶合的本身设计定位,决定了在FPGA中的SOPC的总线结构:全数字交叉的互联结构是SOPC在FPGA中性能发挥的调节棒!

很多人对此有以下担忧:

- 仲裁结构复杂,

- 规模过于庞大

- 对设计工具要求高(每次互联设计,可能要修改太多东西)

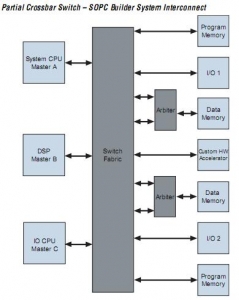

Altera采用了一个折中的方式就是部分数字交叉结构。

而且将仲裁机制放在了从端,这样做的好处,就是有冲突访问可能的从设备,就对他增加仲裁,好处:

- 降低了总线规模

- 提高并行性

- 仲裁效率高

没有优良的总线结构,一切都是空谈,有效的机制,可以弥补CPU的性能的低能化!

总线接口的抽象!Xilinx和Altera志同道合

尽管总线接口的抽象不同,但是,不代表总线结构一致。 X是总线共享型,A是数字交叉型。

例如Avalon-MM,Avalon-SM

Xilinx是PBv,和Fastlink来对应

MM是意思采用存储地址映射抽象,就是将所有端口定义为可以用内存地址来寻址操作。 而SM是代表流媒体数据型,也就是一般和DMA都有一定的联系,当然,也是一种要不就是不断接收数据流 ,要不就是发送数据流的接口。 例如,VGA的数据缓冲,DSP信号数据的输入和输出,例如AD数据的输入,以及DA的输出,同时具有FIFO功能。

并行,并行,再并行。

FPGA中用的设计语言,VHDL,Verilog HDL等,这些都是并行的,FPGA之所以能在很多DSP领域进行大显身手,也是因为他良好的并行扩展性。 那同样。 在SOPC中,要提高系统的整体性能,还是要并行,并行再并行!

上面就结构已经进行了简单的说明。 那么在数据处理的单元上如何设置呢。

1---动态总线宽度的适应。

当你要将32bitNIOS和8bit,或者16bit的系统进行连接的时候,他应该能自动适应!

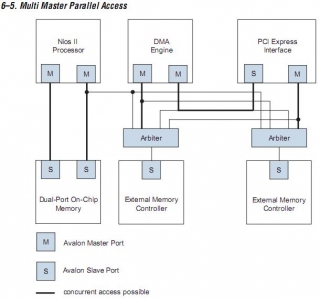

2--增加多个主控单元,对一些控制进行有效并发。

归纳为三点:

多增加CPU的个数,SOPC支持多CPU,而且现在很多CPU也在发展多核。 商用PC已经很成熟了。

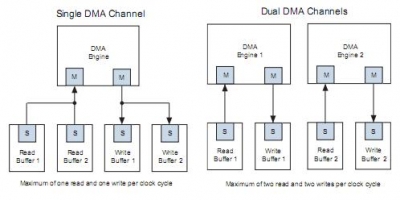

多增加DMA的通道个数,这样CPU可以干别的事情,至少数据吞吐加大

增加PCI-e的设备,这样,NIOS,FPGA不方便处理的,可以通过这样的接口进行功能上的折中。 当然以后也可以增加RapidIO来和TIDSP进行数据的互换。

3--创建分离的数据通路

4--用多DMA进行辅助。 例如

没有新的发明,只是新的组合!

实际上今天很多所谓的创新,也就是一些不同设计元素的合并和组合。 TSMC,在20年前开始代工的时候,有很多人质疑这种方式,实际上这个是一种商业模式的创新。 Altera是前期一些Fabless的厂商之一,很多人也怀疑没有自己的工厂?怎么可以做好产品。 但是回顾今天,大家不都是走这样的路吗。 当然也有一些自己领域的佼佼者,内存,CPU还是自己开灶。

话题拉回,当你一个系统已经不方便的时候,或者是某种功能要求有很突出表现的时候,两个或者多个CPU的系统,或者是拆解再增加必要的子系统。 也是一种创新。

分割为多个子系统的好处:

- 方便管理

- 由于分割后,从设备可以分在不同的有限个主设备中,提供并行,降低冲突。

-

从系统之间耦合较松,就是说可以

依靠共享内存,消息传递,信号灯互锁,FIFO等机制进行同步和信息交换。

一生二,二生三,三生万物.....

现在的工具都很方便复制和例化多个功能单元。 当你设计好一个上面的系统的时候,你也可以将他们又构成一个模块,然后复制这些模块来达到更大的系统。 这种在DSLAM的设计,或者是多路以太网复用到光设备等经常应用。

因此,

一生二,二生三。。。。

当然这种思想是建立在大批量复制功能单元的策略。

另外,还有一种大家熟悉的方式,

就是提高局部的流水动作以提高系统吞吐。 你不仅要有火尖枪,同时也要有混天绫。互相配合才是自然之道。

流水的数据操作分为两类:

- 读流水

- 写流水

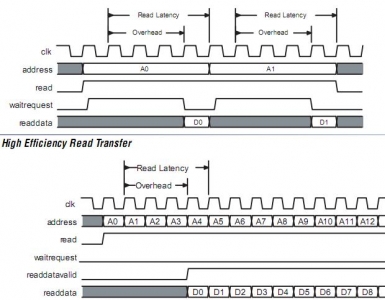

读流水和写流水主要是针对目前的一些存储外设来设计的,就是一个主设备可以在第一读的动作发生,但是没有数据返回的前提下,连续发出多个读的动作,然后在适当的时钟延迟后,连续得到由连续发出读的指令而产生的返回数据序列。 好处是,用个图来表达就明白了。

当然了,你可能说,这个说易行难,设计经验不足。 没有关系,SOPCbuilder的master和Slave接口,已经将这些都做好了。 如果你想自己设计一个,实际知道这样的时序,你也可以的。 不外乎就是要做一个读和返回地址的计数器,计数器的差值是在Readdatavalid的返回时候发出的地址数目,当然你也要设计好数据的宽度

ARM Vs Nios II

大家对ARM和NiosII喜欢比较,今天就说上几句。

最快的NiosII (250Mhz) 比ARM7快,

最小的NiosII比最小的ARM7要小

另外NiosII已经有了MMU,而且对Linux进行了支持

ARM7是把西瓜刀

NiosII是把瑞士军刀。NiosII做一个分型算法借助C2H,速度是ARM7的400倍,不算慢。 但是ARM7的生态资源广,这两个应用实际上是相辅相成。

RemyMartin:

Nios其实最大的缺点在于需要外挂一个Memory,这一点使之成为鸡肋。

很不明白,很简单的一个程序要NIOS IDE 一编译就会弄出来至少几KB,基本上要在几十KB,谁也不可能用片上的mem来做这个:

1--小容量的FPGA,mem不够用

2-- 大容量的也许够,但是谁能把宝贵的片上ram全都给nios,再说,即使都给了nios,软件要是有功能增加和改动,万一不够了怎么办?要用Nios,就需要外加mem,这一点太可恶了。

------------------

nios不扎地,sopc builder倒是个好东西。

bb69:

1. 最小的NiosII做做ARM7,51的工作还是有可能。从Altera合作厂商可以了解的到Nios在OSD、GUI这些应用上还是有比较完整的解决方案,比如一个叫D/AVE的IP就是基于Nios,做的是导航和汽车仪表这些东西,再高级一点的应用如3D加速、能实现的分辨率就很低了,关键还是受性能影响(存储器带宽、包括主频),Nios能做的最高级别的事情也可能就是这些了。

2. 最快的NiosII (250Mhz) 恐怕的在Stratix上才能跑这么快了,看看现在广泛应用的CPU就知道频率好像不是什么卖点,再说了250M对非软核CPU应该是一个很低的频率了吧,何况在要用到Stratix的项目中如果使用传统cpu(ARM、MIPS、Xscale、coldfire)所有提供的丰富外设以及成熟的平台才是方案设计者所看重,在这样的项目或系统中nios恐怕没有市场(个人臆测)。

工艺在进步,FPGA收益,ASIC同样也收益,也许以后会有更多的nios出现在项目中,何况nios(或者软核)有一个天生的局限,必须在FPGA中实现或者原型设计中使用了Nios然后转到ASIC的芯片中存在(synopsis好像提供了Nios综合流片的支持),不知道这是份额是多小!呵呵 ~~ 。

-----------------------------------------------------------------------------------------------------------------------------------------

Nios也好Microblaze也罢,厂商开发这些东西出来真正的目的不是取代现有的CPU,为的只不过是为了卖更多的FPGA。大家使了劲的玩Nios,FPGA厂家当然也乐意推了。 一句话有时间弄NiosII还不如看看ARM、PowerPC的datasheet,这两系列一个代表大批量,一个代表高端。 当开始一个新的项目的时候你的FPGA里面要做做什么UART、IIC这些简单的接口或协议的时候又不想辛苦写状态机NiosII是一个不错的选择。

想了一想老是拿NiosII这级别的东西说事是有点低级了,RemyMartin说的没错 “nios不扎地,sopc builder倒是个好东西。” 能把互联做的十分方便。以后FPGA容量大了用的IP多了,用这么个东西来配置还真是方便。

说了这么多希望对大家实际做项目有点用。