PCIe扫盲——高级错误报告AER(一)

0赞连载目录篇:http://blog.chinaaet.com/justlxy/p/5100057779

前面的文章提到过高级错误报告(Advanced Error Reporting,AER),接下来详细地介绍一下这一功能。在已有的PCIe错误报告机制上(之前文章介绍的),AER还支持以下特性:

· 在登记实际发生的错误类型时,有更好的粒度(Granularity,可以理解为区分度或者精确度)

· 区分各种不可校正错误的严重程度

· 支持登记包头中的错误

· 为Root通过中断报告接收到的错误消息提供了标准化的控制机制

· 可以定位错误源在PCIe体系结构中的位置

· 能够独立地屏蔽某种(或者多种)错误类型的报告

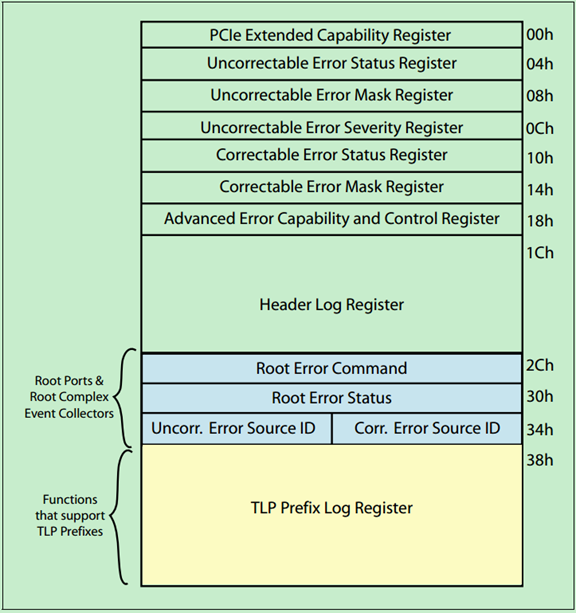

配置空间中的AER相关寄存器结构如下图所示:

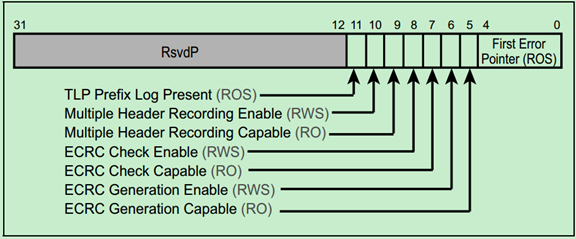

前面的文章中多次提到过,ECRC的产生于校检需要AER的支持,相关控制bit位于高级错误功能控制寄存器中,如下图所示:

其中,最低5bits为当前错误指针(First Error Pointer),当相关错误状态更新时,该指针由硬件自动更新。一般情况下,当前错误指针指向的错误是优先级最高的错误,需要最先被处理的,往往也是其他错误的根源。PCIe Spec V2.1还支持多个错误的追踪(Tracking Multiple Errors)。

图中的ROS、RWS、RO等字符的意义如下:

· RO——只读(Read Only),由硬件控制

· ROS——只读且不被复位(Read Only and Sticky)

· RsvdP——保留且不可以用于其他用途

· RsvdZ——保留且只能被写0

· RWS——可读可写且不被复位(Readable,Writeable and Sticky)

· RW1CS——可读,写1清零,且不被复位

不被复位是指该bit的内容不会因为复位(断电后的上电复位除外)而发生改变。PCIe总线中有多种复位概念,Sticky bit(不被复位的位)不会受到功能层复位(Function Level Reset, FLR)、热复位(Hot Reset)和暖复位(Warm Reset)的影响,甚至不受冷复位(Cold Reset)的影响(当主电源切断后,Vaux等二级电源仍保持正常供电)。关于PCIe总线的复位机制,后续的文章会详细地介绍。