以太网扫盲——SMI(MDC/MDIO)介绍

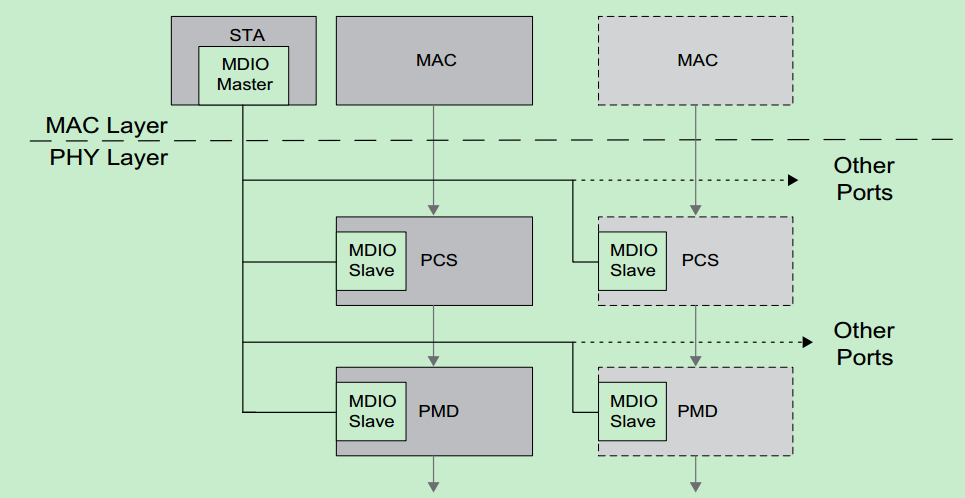

3赞SMI:串行管理接口(Serial Management Interface),通常直接被称为MDIO接口(Management Data Input/Output Interface)。MDIO最早在IEEE 802.3的第22卷定义,后来在第45卷又定义了增强版本的MDIO,其主要被应用于以太网的MAC和PHY层之间,用于MAC层器件通过读写寄存器来实现对PHY层器件的操作与管理。

MDIO主机(即产生MDC时钟的设备)通常被称为STA(Station Management Entity),而MDIO从机通常被称为MMD(MDIO Management Device)。通常STA都是MAC层器件的一部分,而MMD则是PHY层器件的一部分。MDIO接口包括两条线,MDIO和MDC,其中MDIO是双向数据线,而MDC是由STA驱动的时钟线。MDC时钟的最高速率一般为2.5MHz,MDC也可以是非固定频率,甚至可以是非周期的。MDIO接口只是会在MDC时钟的上升沿进行采样,而并不在意MDC时钟的频率(类似于I2C接口)。如下图所示。

MDIO接口有两个版本,通常被称为卷22版本和卷45版本。卷22版本的MDIO接口最多支持连接32个MMD(PHY层设备),每个设备最多支持32个寄存器。卷45版本的MDIO接口最多支持连接32个MMD,32个设备类型,每个设备最多支持64K个寄存器。卷22版本的MDIO接口的数据帧格式如下:

具体每个bit描述如下:

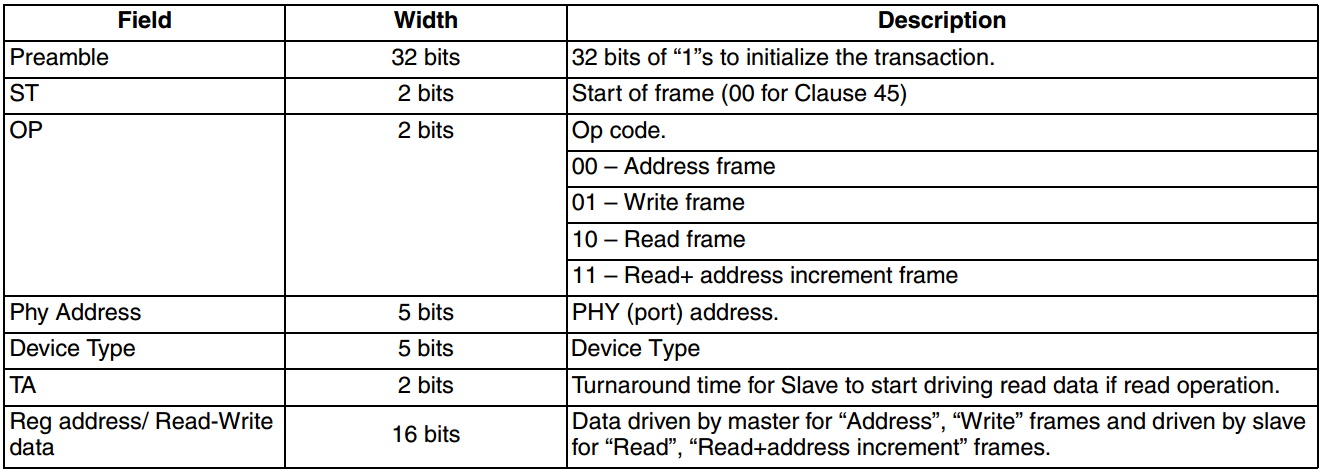

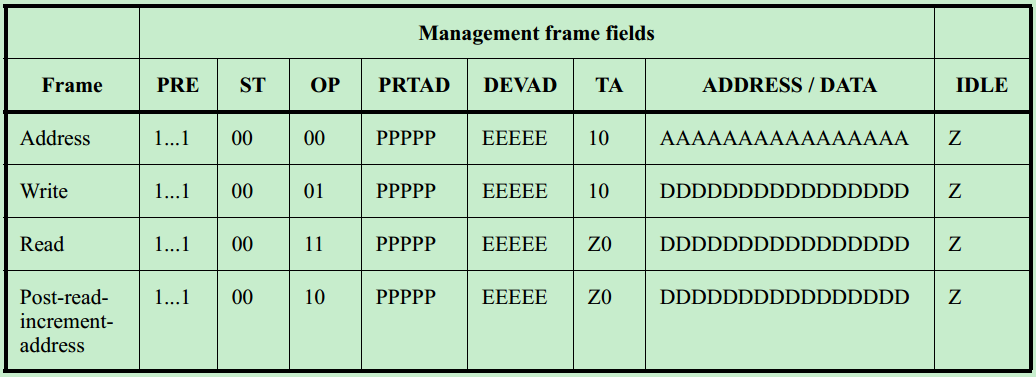

卷45版本的MDIO接口的数据帧格式如下:

具体每个bit的描述如下:

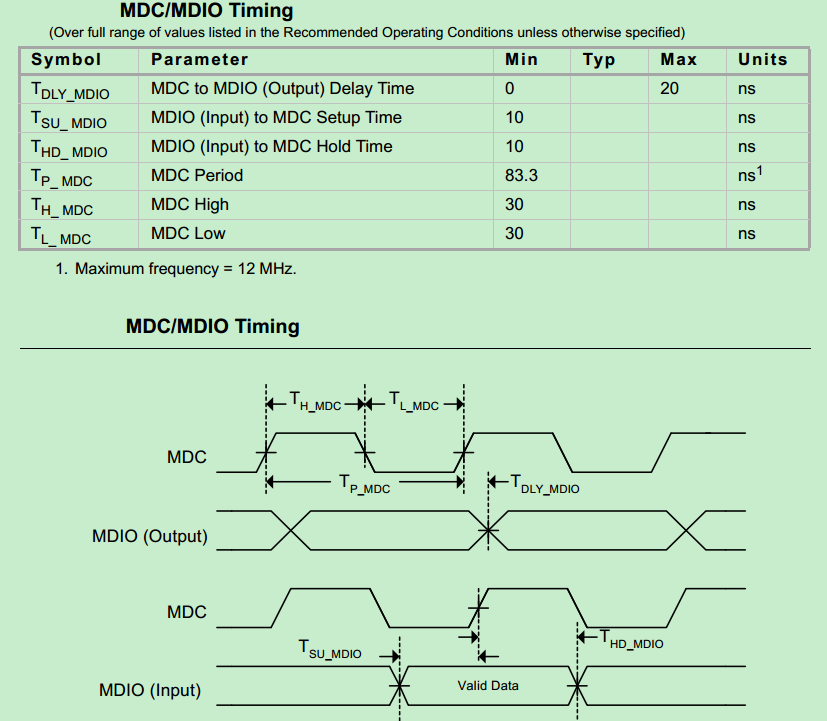

如果是STA(MAC层设备)驱动MDIO,则MDIO相对于MDC上升沿,至少要有10ns的建立时间(Setup Time)和10ns的保持时间(Hold Time)。如下图所示:

如果MDIO是由MMD(PHY层设备)驱动的,则MDIO相对于MDC的Tco(Clock to Output Delay)的范围是0ns~300ns。如下图所示:

实际上,MDC的频率也并非一定是小于或等于2.5MHz,比如Marvell的88E1512最大支持12MHz的MDC:

IEEE 802.3建议同时对MDIO进行下拉(下拉电阻建议为2k欧姆+5%),和上拉(上拉电阻建议为1.5k欧姆+5%),使得在TA时,MDIO处于中间态。但是并非所有的PHY器件都有这样的要求,比如Marvell的88E1512只要求对MDIO进行上拉即可,上拉电阻范围为1.5k~10kΩ。

主要参考资料

1、IEEE 802.3 第22卷,第45卷

2、网友落尘纷扰的博客:https://blog.csdn.net/jasonchen_gbd/article/details/51628992

3、Lattice, RD1194, MDIO Master and Slave Controllers User Guide

4、Marvell,Alaska 88E1512 Datasheet